通用存储装置设计*

2012-12-28张颖,林伟

张 颖,林 伟

(福州大学福建省微电子集成电路重点实验室,福州350002)

在我们现实生活中,会经常用到一些电子设备。然而不同的电子设备有不同的数据存储方式,如NAND Flash、NOR Flash等,这样在使用时就需要进行坏块扫描等各种复杂操作,给用户的直接使用带来不便。同时,电子设备中又有着各种不同的通信接口,例如USB接口、并行总线接口、串行设备接口(SPI)、I2C接口及SD接口等等,如果需要在具有不同接口的电子设备之间进行数据的传输和转存,往往需要专门设计通信接口,或者通过转接器来实现(例如串口转USB等),不仅会带来设计上的不便,而且会造成成本上的增加,不利于大规模生产。

基于目前现有电子设备的不足,我们设计了一种通用存储装置,它不仅提供数据存储器NAND Flash而且还会提供NAND Flash管理。在此装置上设计了多种接口,外部的数据访问请求首先通过某种接口通知该装置;该装置通过对请求的解析访问相应地址的NAND Flash,这样就大大方便了我们的使用,而且也不会增加成本。

1 硬件结构设计

1.1 总体结构设计

本文所设计的通用存储装置包含两个核心部分,存储介质和存储访问接口。存储介质是指存储数据的载体,比如软盘、光盘、硬盘、内存、DVD等,本文是以NAND Flash存储器作为存储介质,并在此基础上提供FLASH管理,使用户可以透明的线性访问NAND Flash空间,并且通过ECC进行数据纠错,在一定程度上保证了数据的可靠性。

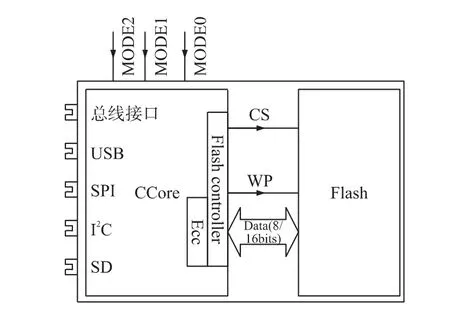

同时,在本装置上有5种可以通过模式的配置进行灵活选择的存储访问接口:USB接口、并行总线接口、串行设备接口、I2C接口及SD接口。其总体硬件结构框图如图1所示。

图1 总体硬件结构框图

由于本装置具有多个接口,所以需要通过模式脚来进行模式选择。如图1所示,在本装置外部接有3 个模式脚:MODE 0、MODE 1、MODE 2,它们只有0和1两种模式,而且只有在上电时才有效。通过对这些模式脚的设置(用外部跳线配置工作模式)来判断装置将运行在何种模式下,然后跳转到该种模式运行。当3个模式脚都配置成0时,为USB模式,这也是该装置在默认情况下运行的模式。当3个模式脚都配置成1时,为SD模式。表1显示了模式脚的配置与模式的对应关系。

表1 模式脚配置与模式对应表

当外部通过这5种接口中的任意一种访问本设备时,将模式脚设置为相应的模式,使设备跳转到相应的模式下运行,通过对应的协议(USB接口协议、并行总线接口协议、串行设备(SPI)接口协议、I2C接口协议及SD接口协议)进行处理后将数据传到NAND Flash存储器进行存储,如上面的图1所示。

1.2 存储访问接口

1.2.1 USB接口

本通用存储装置默认工作在USB模式下。

当本装置工作在USB模式下时,USB接口遵循通用USB2.0协议,可以如同U盘一样访问本装置。

1.2.2 总线接口

总线接口信号连接如图2所示。

图2 总线接口信号示意图

总线接口控制信号共4根。Busy信号表示当前装置是否正在访问NAND Flash,Cmd信号表示向该装置发送控制命令,Data_clk信号则提供数据传输同步信号,Ack信号为该装置收到命令或者数据的反馈信号。

由于总线接口使用了8 bit数据总线,如果设备正在访问NAND Flash,则将Busy信号置为有效,外部数据访问必须等待,直到NAND Flash访问结束;当该装置访问NAND Flash结束,则将Busy信号置为无效,此时该装置将响应外部的数据请求。

本通用存储装置的总线接口在控制过程中为从端模式。控制过程包括接收命令、接收数据和发送数据3种情况,都受到外部访问端的控制;总线的握手过程,不论是命令还是数据的传输,都必须在Busy信号无效的情况进行。其中,外部访问端通过cmd信号的控制命令将数据包按字节发送至本装置;data_clk信号控制是从本装置接收数据还是外部访问端向本装置发送数据。本装置接收到命令和数据后,返回Ack信号,以确认接收成功。

1.2.3 串行设备接口(SPI)

串行设备接口信号如图3所示。

图3 SPI接口信号示意图

SPI接口包括4根信号线,分别为MISO、MOSI、SCK和SS,本通用存储装置作为SPI的Slave端工作,而外部访问端作为Master端。

本装置的工作流程如图7所示,外部访问端工作流程如图8所示。其中,外部访问端向本设备发送命令和数据的过程机制相同,即主端发送从端接收,其区分通过从端即本装置对命令的解析确认实现。本装置向外部访问端发送数据的过程为从端发送主端接收。

1.2.4 I2C接口

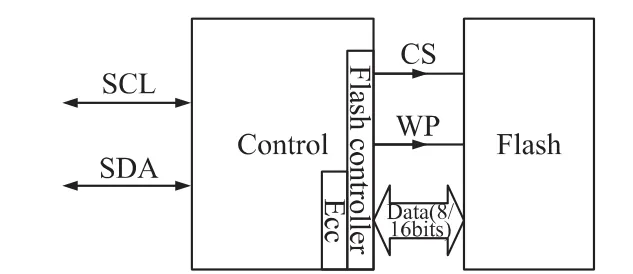

I2C接口信号如图4所示。

图4 I2C接口信号示意图

I2C接口包括两根信号线:SCL、SDA。SCL是串行时钟线,SDA是串行数据线。SDA线上的数据必须在时钟的高电平周期保持稳定,数据线的高或低电平状态只有在SCL线的时钟信号是低电平时才能改变。本通用存储装置在使用I2C接口通信的过程中作为Slave端,外部访问端作为Master端,工作流程如图7、图8所示。

1.2.5 SD接口

当本装置工作在SD模式下时,遵循SD协议,可以如同SD卡一样访问。

1.3 硬件连接图

如图5所示,通用存储装置的 CPU采用CCM1101,通过将USB接口芯片,总线接口芯片,SPI接口芯片,I2C接口芯片和SD接口芯片引脚与CPU上对应的的引脚相连来实现多种接口对NAND Flash的访问。

图5 硬件连接图

2 软件设计

2.1 NAND Flash管理

本通用存储装置具有良好的NAND Flash管理,向用户提供线性的NAND Flash地址空间,用户可以对NAND Flash进行透明的访问,而不需要深入了解NAND Flash的具体技术细节。

NAND Flash是采用Nand结构技术的非易失存储器,内存有8 bit和16 bit两种组织形式,本设计所采用的NAND Flash是8 bit的。NAND Flash可支持读(Read)操作、写(Program)操作和擦除(Erase)操作[1]。其中读操作和写操作的基本单位是页,擦除操作的基本单位是块。在NAND Flash中,与页大小相同的页寄存器,用于数据缓存。当读数据时,先从NAND Flash内存单元把数据读到页寄存器,外部通过访问FLASH的I/O端口获得页寄存器中数据(地址自动累加);当写数据时,外部通过NAND Flash的I/O端口输入的数据首先缓存在页寄存器,写命令发出后才写入到内存单元中[2]。

由于NAND Flash本身固有的技术缺陷,在出厂时NAND Flash会有一定比例的坏块[3-5]出现,造成某些地址空间不可用,这就需要建立一份块对照表,并设计一种管理算法,将上层对逻辑地址的读写操作转换成对NAND Flash物理地址的读写操作,这样上层应用就不必关心NAND Flash如何进行坏块管理。

FLASH管理程序由两部分组成:MTD层(Memory Technology Devices Layer)[6]与 FTL 层(Flash Translation Layer)[7]。MTD 层完成基本的读/写/擦操作,MTD层主要针对闪存控制命令、地址字节数不同这些差异,实现相应的驱动,并且封装这些差异向FTL层提供统一的接口,使得FTL层能够访问任意物理地址的数据,而不关心控制命令序列和地址字节数。FTL层完成坏块管理与逻辑地址到物理地址转换,消除NAND Flash固有特性带来的不足,让上层应用程序以类似于读写磁盘的方式对NAND Flash进行读写访问。这样用户就不需要深入了解NAND Flash的具体技术细节,便可以对NAND Flash进行透明的访问。软件架构图如图6所示。

图6 软件架构图

对NAND Flash读写操作过程如下:

在读数据时.FTL层将根据收到的上层逻辑地址计算其对应的逻辑块号,然后再根据块对照表查找对应的物理块,最后调用MTD层接口函数来完成读操作。

在写数据时,FTL层将同样要根据收到的上层逻辑地址计算相应的逻辑块号,然后从备用的空闲块中分配一个擦除次数最少的空闲块给对应的逻辑块号,并将空闲块的物理地址记录在块对照表中[8-9]。最后再调用MTD层接口函数完成写操作。为了进一步平衡NAND Flash块的擦除次数,延长NAND Flash的使用寿命。在空闲时将擦除次数比较多的块数据拷贝到擦除次数较少的块中,将那些擦除次数比较多的块作为空闲块备用。

2.2 通信协议与数据结构

外部访问端对本通用存储装置的访问,如果通过USB接口或者SD接口,则直接按照USB和SD协议实现,如果通过其他的接口,则遵循以下统一的通信协议和数据结构。

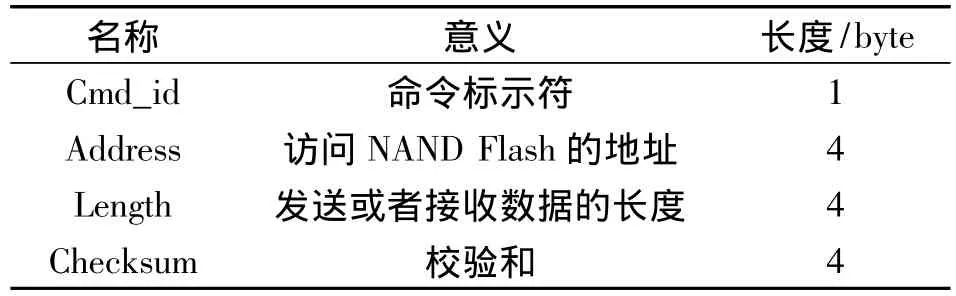

外部请求通过控制命令的方式实现,控制命令共 4 个字段,分别为 Cmd_id,address,length 和checksum(校验和),其中 Cmd_id 占一个 byte,addr,len和checksum各占四个byte,共13个byte。

控制命令的数据结构如表2所示。

表2 控制命令的数据结构表

其中命令ID包括以下类型,如表3所示。

表3 命令ID与值对应表

本装置接收到控制命令后将返回确认数据包,包含2个byte,命令标示Cmd_id和错误类型,Cmd_id即为该装置接收到的命令标示,错误类型则取决于以下情况(表4)。

表4错误值与错误类型值对应表

外部访问端需要根据接收到的命令确认数据包决定是否进行数据传输。

2.3 控制流程

当本通用存储装置工作在USB模式下,将遵循USB通信协议;当本通用存储装置工作在SD模式下,将遵循SD协议。

当使用其他接口时,本装置的内部控制流程如图7所示。

图7 通用存储装置内部流程图

外部访问端控制流程如图8所示。

如图7、图8所示,本装置与外部访问端之间的通信以命令开始,数据结束,即必须先有外部访问端发送命令,本装置对命令进行验证确认,并返回确认数据包,两端确认命令传输无误后再进行数据的传输。

图8 外部访问端控制流程图

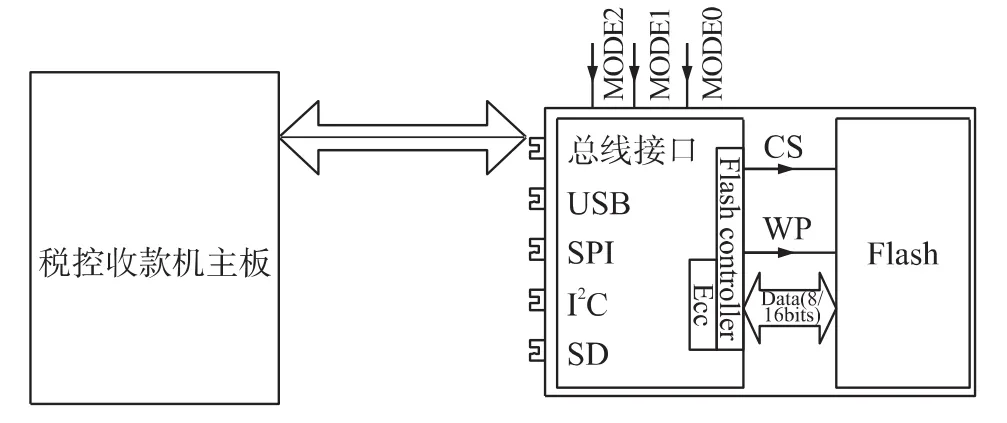

3 应用实例

本通用存储装置能够实现多种接口对NAND Flash的访问。目前,它已经成功应用到一款税控收款机上。用本通用存储装置的其中一种接口-总线接口与税控收款机主板相连,进行数据交互以实现将税控数据存放到存储装置的NAND Flash上。这样用户便可以对税控数据进行线性的访问了。而其他的接口可以留作别的用途,这样就节约了成本。其硬件结构框图如图9所示。

图9 税控收款机硬件框图

主要工作原理:首先要将模式角配置成001,使设备跳转到总线模式下运行。总线接口控制信号一共有4 根:Busy,cmd,data_clk,Ack。Busy 作为判断NAND Flash是否处于忙状态的标志,如果设备正在访问NAND Flash,则将Busy信号置为有效,外部数据访问必须等待,直到NAND Flash访问结束;当该装置访问NAND Flash结束,则将Busy信号置为无效,此时该装置将响应外部的数据请求。命令和数据的传输必须在Busy信号无效的情况下进行。税控收款机通过cmd信号的控制命令将数据包按字节发送到存储装置;data_clk信号用来控制是从存储装置接收数据还是税控收款机向存储装置发送数据。当存储装置接收到命令和数据后,返回Ack信号,以确认接收成功。

4 结论

本通用存储装置提供了可管理的NAND Flash存储器以及多种访问接口,使得电子设备的数据存储与访问可以直接通过该装置实现,而不需要额外的设计或者转接器,给电子设备的设计使用带来便利,并能够节约成本。同时,它在一款税控收款机上的成功应用也验证了它的可行性。

[1]李斌,薛质,胡永华.NAND Flash在基于CCM3118税控收款机上的应用[J].中国集成电路,2005,7.

[2]魏韬,林平分,孙丽华,等.NAND Flash管理算法的设计及实现[J].电子元器件应用,2010,12(8):66-68.

[3]周军.NAND Flash的坏块管理设计[J].单片机与嵌入式系统应用,2010(9):15-20.

[4]彭兵,步凯,徐欣.NAND Flash坏块管理研究[J].微处理器,2009(4):113-115.

[5]XSR 1.5 Bad Block Management Application Note[EB/OL].2010(4).http://www.samsung.com/glohal/business/semiconductor/products/flash/FlashApplicationNote.html.

[6]段权顺.Nand Flas控制器的规格设计[J].电子产品世界,2006(2):116-118.

[7]Lu Sheng,Li Chunping.Using Statistical Model to Improve the Efficiency of Mining Maximum Sequential Patterns[C]//Proc.of the 2nd International Workshop on KGGI,2004.

[8]杜家瑞,刘正强,李应启.NAND Flash在嵌入式系统中的应用[J].微处理机,2010(2):115-118.

[9]时正,陈香兰,纪金松,等.大容量NAND Flash文件系统中的地址映射算法研究[J].小型微型计算机系统,2010,31(1):155-159.