高速高密度PCB电源完整性分析

2012-12-28闫静纯苏浩航

闫静纯,李 涛,苏浩航

(北京空间机电研究所,北京100076)

随着器件工艺和封装集成技术的发展,更多功能的模拟和数字电路制作或集成到单个芯片中。从芯片的集成度[1]和工作频率发展趋势上看,①芯片的工作电流在不断增加,功耗也在相应的增加。②芯片主时钟频率越来越快,从而要求边沿切换时间越来越短。③芯片的工作电压却不断减小,电压噪声容限也随之减小。因此,当大量高速开关器件同时快速切换状态时,就会产生电源噪声,干扰周围的高速信号,并且由于噪声容限变小,严重时,可引发芯片的误动作,造成不利影响。因此对电源完整性的研究显得越来越重要[2-3]。

本文以一块8层板为例,运用目标阻抗法对其电源分配网络进行分析,针对网络中的电源完整性问题,采用合适的修改措施,使其电源分配网络设计满足要求。

1 电源分配网络设计

高速PCB电源完整性的意义就是为系统内所有器件或芯片提供足够的电源,并满足稳定性要求[4]。在实际高速电路系统中,电源分配网络在不同频率时,存在不同电源阻抗,当大量开关同时切换状态产生的噪声电流通过时,会产生一定的电压降和电压摆动,造成供电不连续,可能会影响高速系统的正常工作。所以为了保证每个器件始终都能得到正常的电源供应,就需要对电源分配网络的电源阻抗进行控制,尽可能降低其阻抗。

PCB的电源分配网络PDN组成部件[5]如图1所示,包括稳压模块VRM、去耦电容、电源地平面耦合电容。它们分别在不同的频率范围内做出响应。稳压模块的频率响应范围大约是0~1 kHz;大电解电容提供电流并在1 kHz~1 MHz频率范围内保持较低阻抗;高频陶瓷电容在1 MHz至几百兆赫兹频率范围内保持较低阻抗;电源地平面对则在100 MHz以上频率范围内保持较低阻抗;更高频率范围的低阻抗要求则需要芯片内部电源网络来提供。

图1 PDN的组成部件

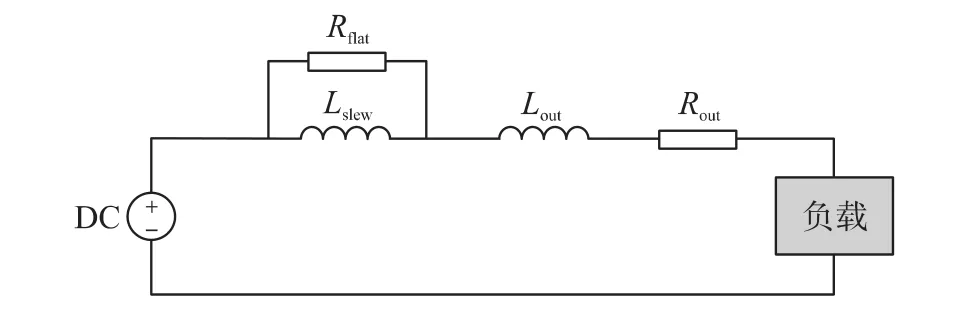

稳压模块VRM(Voltage Regulator Module)是最大的电荷存贮和输送源,为整个电子系统提供能量。图2是VRM的简化线性模型,Rout为等效输出电阻,Lout为等效输出电感,Rflat为等效串联输入电阻,Lslew为等效串联输入电感。

图2 VRM的简化线性模型

去耦电容[6]的主要功能是可以在开关器件瞬时状态切换时提供电荷。当VRM的输出阻抗超过目标阻抗时,去耦电容可以把VRM旁路,为高频突变电流提供低电感的回路,直接给开关电路供电。使用去耦电容可以有效的抑制同步开关噪声,减小电压波动。

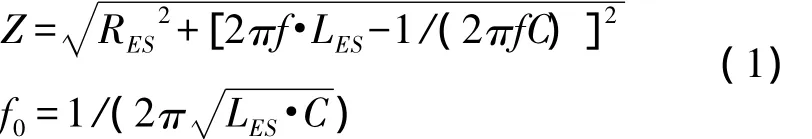

由于去耦电容本身存在等效串联电阻RES和等效串联电感LES。因此在电源完整性分析中采用的简化电容模型是由电容、电阻和电感串联组成的,即一个RLC串联谐振电路,其等效阻抗和谐振频率为:

式中:Z是电容的等效阻抗;f0为电容的谐振频率;RES为电容的等效串联电阻;LES为电容的等效串联电感。

在进行PCB设计时,要选择RES较小、谐振频率和电路工作频率相近的去耦电容,在此基础上,容值较大,LES较小为好。在实际电路中,为使去耦电容在一定的工作频率范围内保持较低阻抗,通常采用大小电容并联的方法,且并联电容的容值相差两个数量级即100倍。并联使得RES和LES减小,容值增大,去耦效果更好。

在高速PCB上放置去耦电容的基本原则是靠近电源管脚且确保安装电感尽量小。布线时尽量减少焊盘与电源地连线的长度,使用宽的连线。如果空间允许的话,可以多打连接过孔,形成并联方式来降低电感;如果工艺允许的话,可以直接在电容焊盘上打盲埋孔,这是降低电感的最好办法。

当前电源完整性分析的主要方法是目标阻抗设计法[7],计算公式如下:

式中:Zm为目标阻抗;Vsupply为供电电压;IDynamic是ΔI噪声电流与瞬态负载电流的总和。

电源完整性分析将PDN看成一个网络,以各个功耗器件的最大电流激励PDN,为了使电压波动小于电源噪声容限,PDN的电源阻抗必须小于目标阻抗。通过PDN的频域阻抗曲线,可以清楚地判断在哪些频点上会出现严重的电源噪声。

2 电源完整性仿真

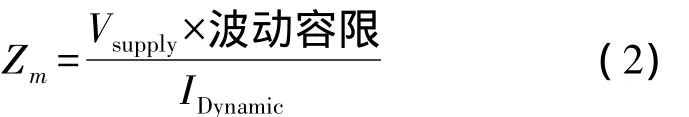

本文以一块8层板为例,如图3所示,对其电源完整性进行分析,分析软件为 Ansoft SIwave。该PCB板的叠层如图4所示。板上包含模拟电路和高速数字电路,其中3.3 V的电源主要支持板上FPGA器件和数传的主要工作,信号上升时间小于1 ns,因此该电源层上的噪声对整个电路的影响至关重要,在设计中需要对3.3 V电源进行详尽分析。

图3 8层板PCB图

图4 8层PCB板叠层设置

2.1 谐振分析

首先对整板进行谐振分析,发现在FPGA附近有一个33 MHz左右的谐振模式,如图5所示。如果谐振被激发,会影响FPGA的正常工作,故需进一步进行电源阻抗分析,以消除这个谐振,减小电源对FPGA工作的影响。

图5 33 MHz谐振模式的电压波动图

2.2 电源阻抗分析[8]

在3.3 V数字电源上,器件时钟频率为100 MHz,估算取3.3 V电源上的ΔI噪声电流与瞬态负载电流总和为1 A,允许波动范围取5%,则根据式(2)可知,目标阻抗为0.165 Ω。通过计算在信号上升时间为1 ns时,根据信号完整性理论可知,其信号的转折频率[9]为500 MHz,因此该3.3 V电源的阻抗在500 MHz内均需要小于目标阻抗。

在各数传芯片及FPGA的电源引脚处放置探针,对其进行电源完整性仿真,结果如图6所示。

图6 阻抗仿真结果图

频率100 MHz时各探针处的阻抗值如图6所示,可以看出,只有port5处的阻抗值(0.289 Ω)高于目标阻抗(0.165 Ω),其余均低于目标阻抗。但在500 MHz内并不满足要求低于目标阻抗的要求,需降低其电源阻抗。并且FPGA处的电源阻抗在30 MHz左右有一个波动,尖峰处(在31.3 MHz时为0.199 Ω)超过了目标阻抗,这与谐振分析一致。因此需要在附近添加去耦电容,以降低电源阻抗。

2.3 添加去耦电容

本文选取了容值为33 nF,寄生电感为0.47 nH,寄生电阻为0.03 Ω,谐振频率为40 MHz的电容,以降低FPGA附近30 MHz处的高电源阻抗。选取2.2 nF、5.6 nF、470 pF三组电容降低500 MHz以内的高阻抗。这几种电容具体的谐振曲线如图7所示。

图7 电容谐振曲线图

2.4 修改后的阻抗分析

在FPGA及各数传附近添加去耦电容之后,30 MHz左右时FPGA处的的电源阻抗尖峰消除了,并且FPGA及各数传处的电源阻抗在530 MHz范围内都低于目标阻抗值。3.3 V数字电在工作频率范围内满足了阻抗低于目标阻抗设计要求,具体仿真结果如图8所示。再次对PCB板进行谐振分析,FPGA附近33 MHz时的谐振消失了,仿真结果如图9所示。

图8 修改后的3.3 V电源阻抗分析图

图9 修改后的33 MHz谐振模式的电压波动图

3 结论

本文以具体的多层高速高密度PCB板为例,详细地对电源完整性加以分析,并通过添加去耦电容,有效地改善了电源分配网络的设计,对整个PCB的电源系统的设计具有明显的指导意义。

[1]Sridharan V,Swaminathan M,Bandyopadhyay T.Enhancing Signal and Power Integrity Using Double Sided Silicon Interposer[J].IEEE Microwave and Wireless Components Letters,2011,21(11):598-600.

[2]白同云.高速PCB电源完整性研究[J].中国电子科学研究院学报,2006,1(1):22-30.

[3]周子琛,申振宁.高速嵌入式系统中的电源完整性设计方法[J].单片机与嵌入式系统应用,2010(3):19-21.

[4]张木水.高速电路电源分配网络设计与电源完整性分析[D].西安:西安电子科技大学,2009.

[5]Swaminathan M,Kim J,Novak I,et al.Power Distribution Networks for System on Package:Status and Challenges[J].IEEE Transactions on Advanced Packaging,2004,27(2):286-300.

[6]Tzong-Lin Wu,Hao-Hsiang Chuang,Ting-Kuang Wang.Overview of Power Integrity Solutions on Package and PCB:Decoupling and EBG Isolation[J].IEEE Transactions on Electromagnetic Compatibility,2010,52(2):346-356.

[7]Madhavan Swaminathan,Ege Engin A,著.芯片及系统的电源完整性建模与设计[M].李玉山,等译.北京:电子工业出版社,2009:13-14.

[8]李学平,李玉山.基于Ansoft仿真分析的SSN解决方案探讨[J].微型机与应用,2011,30(4):68-70.

[9]林少晶.板级电源的完整性设计及验证方法[J].广东科技,2009(12):211-213.