一种改善DDS电路系统杂散方法研究

2012-10-25高建栋韩壮志郭宝锋

高建栋,韩壮志,何 强,郭宝锋

(军械工程学院雷达工程教研室,河北 石家庄 050003)

0 引 言

直接数字频率合成器(direct digital frequency synthesizer,DDS)具有频率转换时间短、频率分辨率高、输出相位连续、稳定度高、可编程、全数字化、易集成等优点[1],已经广泛应用于通信、航天、雷达和高速仪表仪器等领域。在实际应用中,DDS的输出都会存在一定量的杂散信号。DDS芯片的杂散信号主要有相位截断误差、幅度量化误差和DAC非线性误差[2-3]3个来源。文献[4]主要对相位截断误差进行了分析,并提出了用相位抖动注入法和延时叠加法来改善DDS的输出杂散。文献[5]对无相位截断情况下幅度量化杂散信号的功率和频域特征进行了系统深入的分析、仿真和实际测量,得到一些重要的规律性结论。相对其他两种杂散来源,对DDS输出信号频谱影响最为关键的是DAC的非线性干扰[6]。对于DAC的非线性对DDS输出信号的影响,研究比较少[7]。

DDS的3种杂散来源,都是由DDS自身的结构特点决定的,当DDS芯片的各个参数确定以后,这些杂散不可避免地要出现在输出信号中,引起输出信号的不纯净。由于已经有较多文献对相位截断误差和幅度量化误差做了深入的分析[2-6],本文不再对这两种杂散进行研究。本文主要研究DAC非线性对输出杂散的影响,分析了DDS电路系统中引起杂散的原因,并提出了一种能有效改善DDS电路输出杂散的方法。

1 理想条件下DDS输出频谱分析

在理想条件下,DDS等效于一个理想的采样保持电路。其中,相位累加器和查询表结合起来相当于一个采样器,采样周期为Tc=1/fc,DAC相当于一个理想的保持电路,对采样数据实现阶梯方式重构。

设输出信号频率为f0,对信号S1(t)=sin(2πf0t)进行采样,得到采样信号为

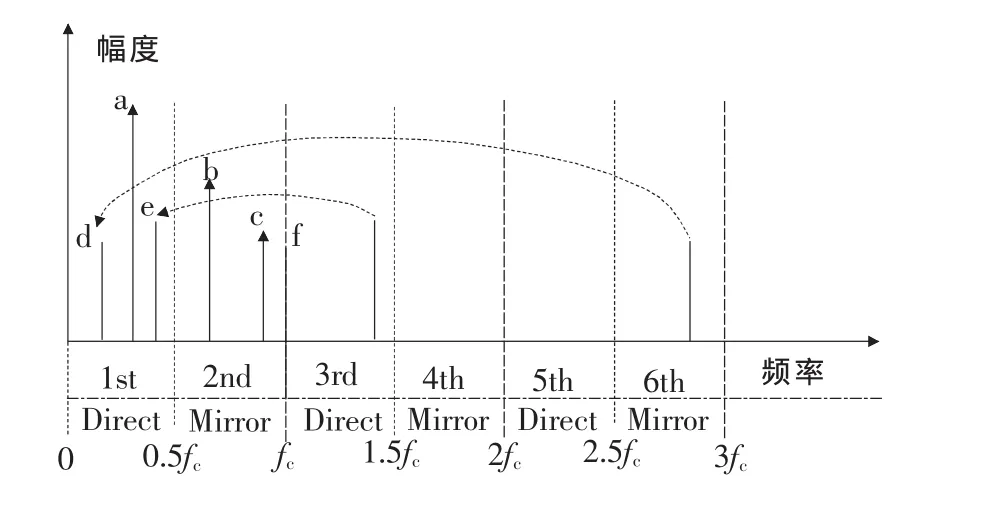

通过式(3)可以看出,理想DDS输出频谱是包络为Sa函数的离散谱线,且仅存在于mωc±ω0(m=0,1,2,…)。图1是理想DDS输出的频谱图。

图1 理想DDS输出频谱图

由奈奎斯特采样定理可知,要恢复出理想波形,输出频率 f0不能超过 0.5fc。若超过 0.5fc,则一阶镜像频率就会落在奈奎斯特带宽内,即0.5fc内,就不能恢复出理想波形了。而且考虑实际的滤波器并不是理想的,它存在一个过渡带的问题,所以工程上一般将DDS的输出频率限制在0~0.4fc内。

2 DDS电路系统输出杂散分析

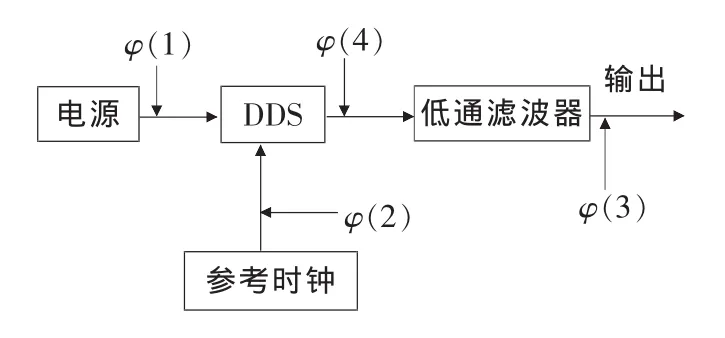

当DDS芯片的各个参数确定以后,引起DDS电路系统输出杂散的模型如图2所示。其中φ(1)表示的是电源纹波引入的杂散,φ(2)表示的是参考时钟质量不佳引入的杂散,φ(3)表示的是低通滤波器设计不合理引入的杂散,φ(4)表示的是DDS输出频段选择不合适引入的杂散。除此之外,还有电路电磁兼容性设计不合理引入的杂散,下面分别加以分析。

图2 DDS电路杂散模型

(1)电源纹波较大。电源纹波是叠加在直流稳定量上的交流分量,它是调整和滤波电路后面直流输出电压中所残存的交流和噪声成分。纹波一般是通过调制的方式干扰有用信号,易在电路中产生各种频率成分的谐波,所以电源纹波会增加额外的杂散。

(2)参考时钟质量不佳。DDS内置PLL倍频部分,可以使外部较低频率的参考时钟经过倍频后产生较高频率的DDS系统参考时钟源。这样虽然可以简化电路结构,但会使输出谱严重恶化,而且噪声基底也会变高,近端噪声也较大。除此之外,启用内部PLL还会使工作电流增大100mA左右,这对长期工作的DDS芯片也有不利的影响。

(3)滤波器设计不合理。一般在DDS的输出后面都要加一个滤波器来抑制杂散,滤波器设计不当会造成滤波效果不好,会使杂散分量落入输出频带,使系统性能下降。

(4)输出频段选择不合适。输出频段选择不合适时,由于DAC非线性产生的谐波分量会与时钟频率产生差频信号,差频信号很容易落入奈奎斯特带宽内,引起较大杂散。

(5)电磁兼容设计不合理。电磁兼容是指电气及电子设备在共同的电磁环境中能执行各自功能的共存状态,电磁兼容性对系统的杂散等重要性能有很大的影响。如果系统PCB设计不合理,或屏蔽措施不当,也会使系统输出杂散很大。

对于这几类引起DDS电路较大杂散的原因,本文主要分析了输出频段选择这方面对输出杂散的影响,并结合具体仿真实验进行讨论,提出了如何选择输出频段来改善输出信号的办法。

3 输出频段选择对杂散影响

理论上DAC为线性器件,DAC在转换中数字量的最低位所表示的模拟量称为LSB(least significant bit),然后数字输入每增加1,模拟输出就会增加一个LSB,所以输入输出曲线成台阶状。但由于不理想状况的存在,包括DAC的积分非线性、差分非线性、DAC转换过程中出现的毛刺等等,使得输出并不能完全代表输入,包括幅度上和时间上的不同,而且每一个台阶上的高度也不尽相同,有高有低。

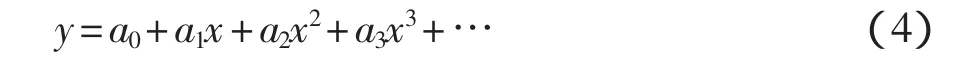

理想DAC的特性曲线是一条斜线,设为y=ax+b,数字输入位于x轴,模拟输出位于y轴。x轴上输入范围是 M~N,y轴的输出范围是 P~Q,其中 M、N、P、Q表示的是边界值。信号g(t)代表一个无失真的正弦波输入,由M~N之间离散的数字组成,时间轴向下。信号u(t)代表信号的模拟输出,范围在P~Q内,时间轴向右。

理想条件下,DAC的特性曲线为线性,当输入信号为正弦波时,通过DAC的输出信号也为同频率的正弦波,只是幅度上有所差异,如图3(a)所示;在非理想条件下,由于前面分析的不理想状况的存在,使查表所得的幅度序列从DAC的输入到输出经过一个非线性过程。设非线性特性曲线函数为y=f(x),如果f(x)的各阶导数存在,则可以展开为如下幂级数,系数取决于y=f(x)的各阶导数

由于x的值较小,可以忽略三次方项以上的高次项,即

其中a0+a1x属于线性函数,不会产生谐波分量。为了分析非线性对DAC的影响,可以令非线性特性曲线为y=a2x2,通过作图法,得到的输出结果u(t)如图3(b)所示。可以看出,信号输出明显出现了失真。根据傅里叶级数展开式,会产生输出信号f0的各次谐波分量。尽管实际中DAC器件的特性曲线与理想的直线几乎没有偏差,但是即使有最微小的偏差也会导致输出频谱中出现谐波杂散。由于DDS是采样系统,这些谐波会以时钟频率fc为周期进行搬移,产生混频信号f,即

式中:m,n——任意整数。

当输出频段选择不合适时,这些混频信号落到奈奎斯特带宽内就形成了不需要的杂散频率,频率的位置可以确定,但幅度一般难以确定。一般说来,谐波次数越低,幅度就越大。

图3 DAC输入输出波形图

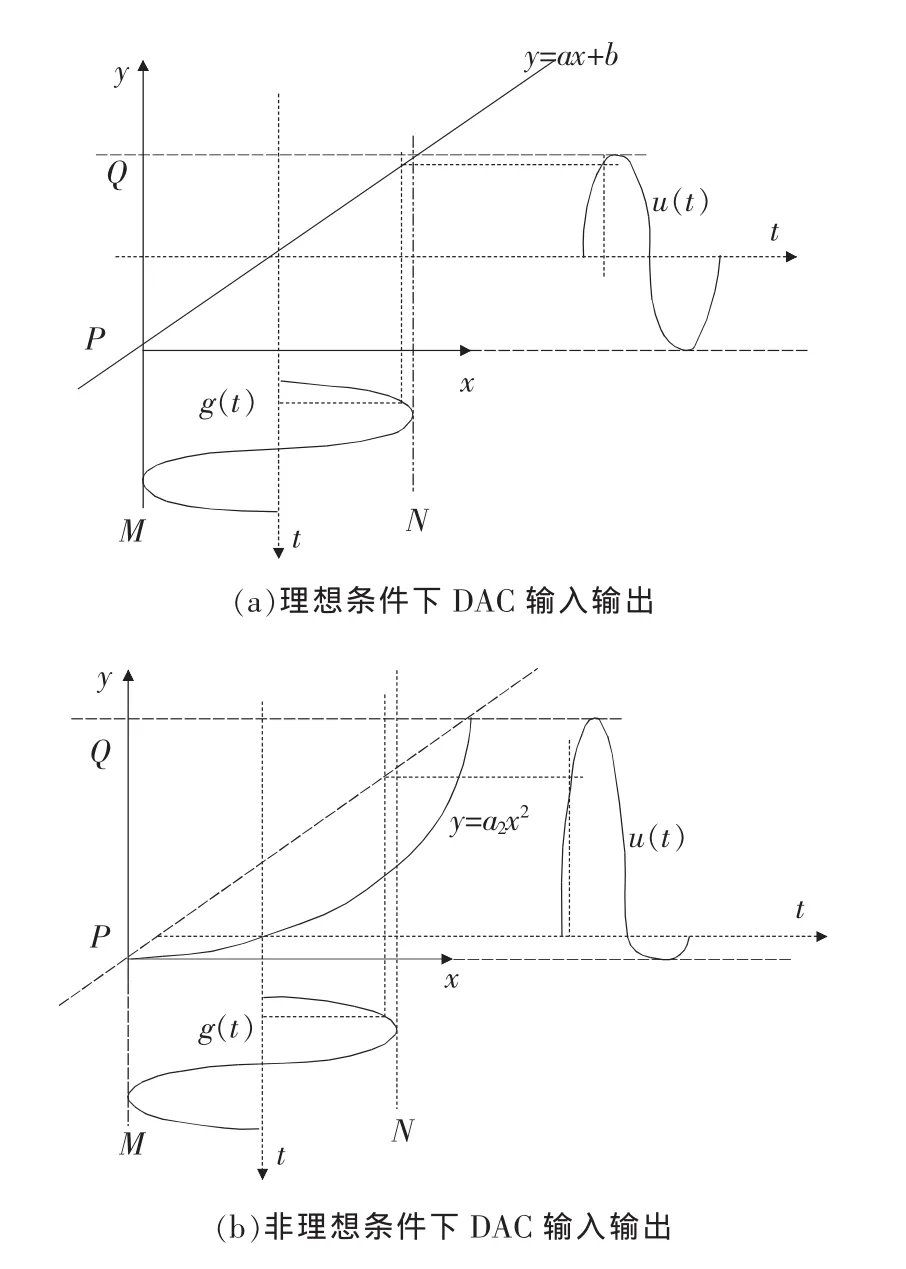

上面分析了由于DAC的非线性会产生输出频率f0的谐波。根据奈奎斯特准则,所有大于0.5fc的谐波都将搬移到0~0.5fc范围内(称为第一奈奎斯特带),第二奈奎斯特带为 0.5fc~fc,第三奈奎斯特带为fc~1.5fc,依此类推。搬移时奇数奈奎斯特带的频谱直接复制到第一奈奎斯特带,而位于偶数奈奎斯特区域的频谱经过镜像搬移到第一奈奎斯特区域。DDS非线性引入杂散如图4所示。其中,a谱线是输出频率f0的主谱线,f是时钟频率fc泄露谱线。根据DDS的内部工作原理可知,b、c是由于DAC非线性产生的a的谐波,d、e是由于频谱搬移产生的谱线。如果考虑DDS的外部因素,由于DAC的外部器件也会存在一定的非线性,所以产生了谐波b、c谱线,d、e则是谐波与时钟泄露f产生的差频。

图4 DDS非线性引入杂散频谱图

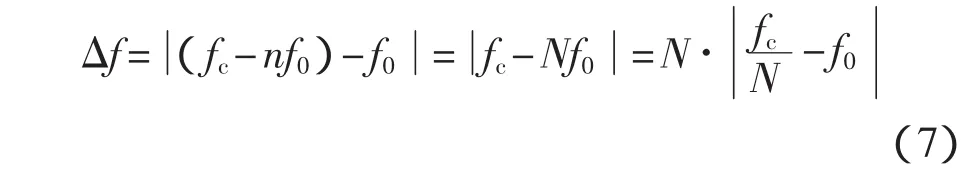

根据图4可以看出,时钟频率泄露与输出频率谐波nf0产生的差频信号d、e很容易落入奈奎斯特带宽内,并且有可能造成离主谱线很近。判断这种杂散离主谱线距离的一般公式为

式中:N——离输出频率f0最近的特殊频率的除数,表达式为N=。

由式(7)可以得到如下结论:当 N=3,4,5,6,7…,即当输出频率 f0靠近 fc/3、fc/4、fc/5、fc/6、fc/7…时,差频信号产生的杂散离输出频率f0很近,最后当距离主谱线只有几十千赫兹时,这时候的杂散很难用滤波器去除。而且,这种杂散的幅度比较大,当经过倍频电路后还要恶化,所以这种杂散会带来严重的输出频谱谱质不纯,在实际应用中不能让它们出现在要求的输出通带内。所以在工程设计时,要充分考虑输出频带,避免杂散分量落入其中,以此来获得较好的杂散指标。设计中,DDS的输出频带要限制在0~0.4fc这一频段,而且不要跨越时钟频率的整数分频点,也不要使输出频段离这些点太近。

4 实际电路应用

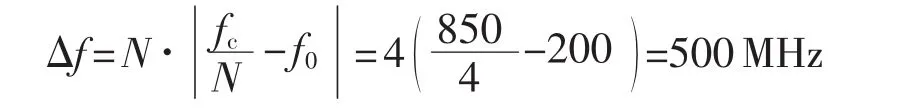

当输出频率f0=200 MHz,fc=850 MHz时,根据=212.5MHz离输出频率最近,所以取N=4。代入式(7),杂散离主谱线的距离为

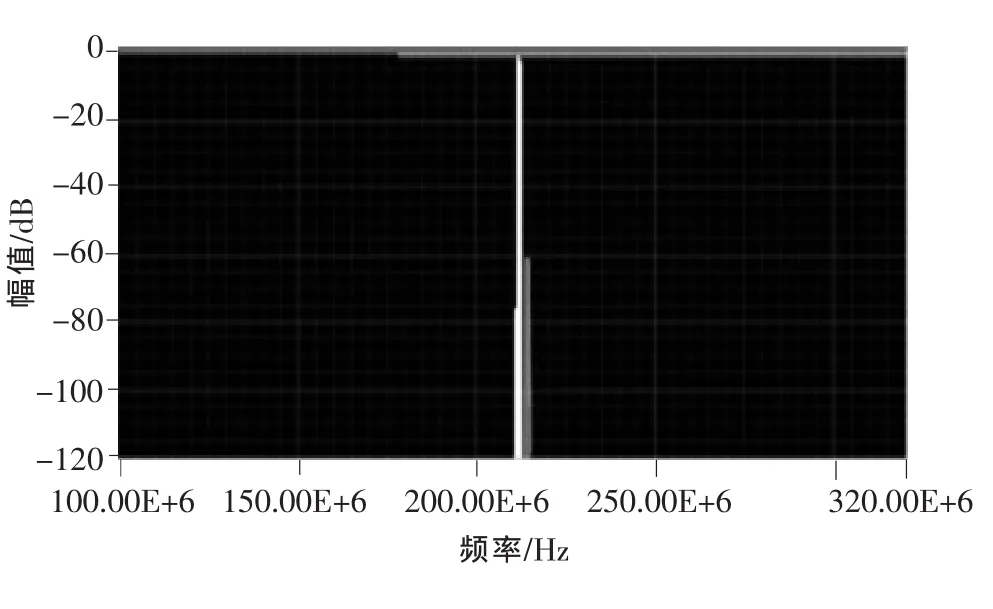

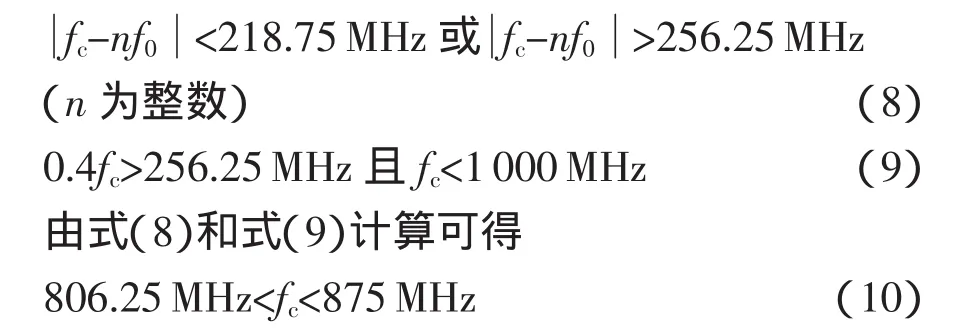

使用AD公司的在线仿真工具ADIsimDDS对DDS的杂散特性进行的仿真,DDS芯片选择AD9912芯片,结果如图5所示。

图5 输出频率f0=200MHz频谱图

从图5中可以看出,杂散(左数第二根线)离主谱线50MHz,与计算值相符。

图6 输出频率f0=212MHz频谱图

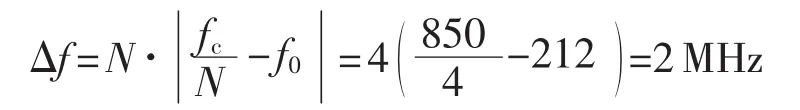

同理,当输出频率f0=212MHz时,可以计算得到杂散离主谱线的距离为频谱如图6所示。可以看出,此时杂散(左数第二根线)离主谱线只有2MHz。

本课题中,要求DDS芯片AD9912的输出频率范围 f0为 218.75~256.25MHz,为使时钟与输出频率的差频谐波不在DDS的输出频带内,应满足:

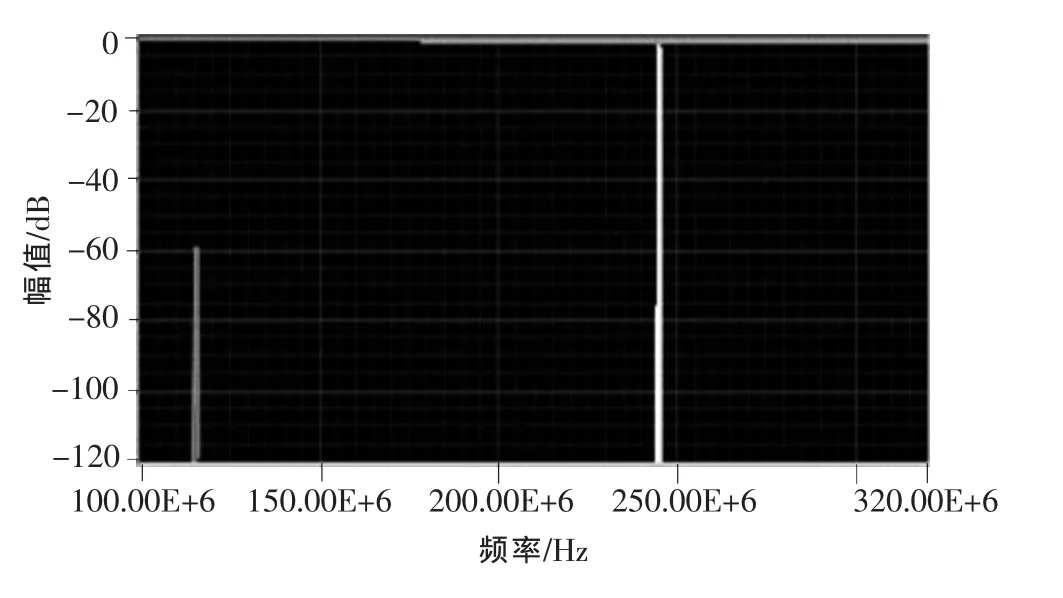

因此,取参考时钟fc为850MHz。当输出频率为245 MHz时,参考时钟为850 MHz仿真结果如图7所示,可以看出差频杂散(左数第一根线)离主频较远,通过设计合理的滤波器就可以把这些杂散抑制得很好。

图7 输出频率f0=245MHz频谱图

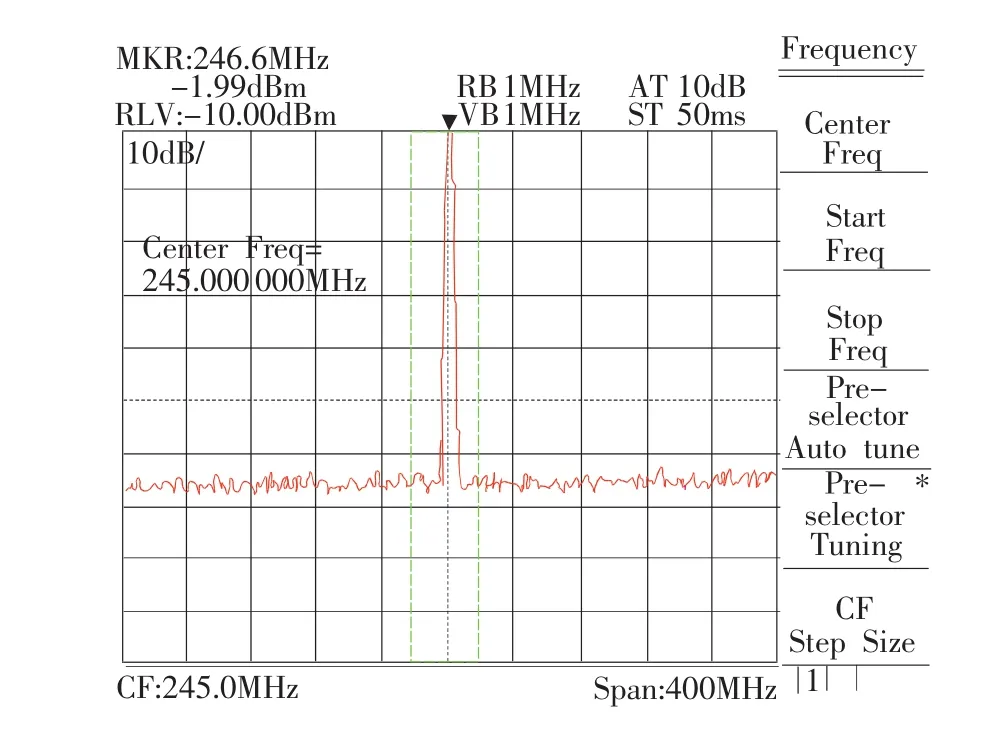

最后,本课题选择电源纹波较小的线性电源和质量较好的850 MHz参考时钟信号,优化电磁兼容性设计,结合带通滤波器滤除镜像频率分量,测得输出频率为245 MHz信号的频谱如图8所示。图中Span为400MHz,横轴每格代表40 MHz,可以看出,除了设定的输出频率外,DDS输出杂散谐波已被带通滤波器滤除掉,杂散抑制优于-70 dBc,可以满足绝大多数场合的要求。

图8 DDS输出频谱(主频245MHz)

5 结束语

在DDS电路系统设计过程中不免要引入杂散,包括DDS芯片自身的原因以及外部环境造成的影响,引起输出信号的不纯净。本文主要分析了DDS电路系统中引起杂散的原因,并通过仿真分析提出了通过选择输出频段来改善输出杂散的方法,对提高DDS电路输出信号的质量有很好的促进作用,在DDS电路设计方面具有指导意义。

[1]张美仙,王红亮,丁海飞.基于DDS芯片的信号源设计[J].仪表技术与传感器,2010(9):54-56.

[2]蔡剑华,王先春,胡惟文.DDS杂散抑制技术的研究与实现[J].微电子学与计算机,2009,26(7):127-133.

[3]胡仕兵,汪学刚,姒强.直接数字频率合成技术杂散信号频谱性能分析[J].电路与系统学报,2009,14(5):87-91.

[4]张海涛,苗圃,李珍.DDS杂散抑制技术研究与仿真[J].计算机仿真,2011,28(2):397-401.

[5]田新广,李文法,孙春来,等.无相位截断情况下DDS的幅度量化杂散特性分析[J].仪器仪表学报,2008,29(5):914-920.

[6]杨杰,杨光,蒋国琼,等.基于DDS的低杂散捷变频合成器设计[J].信息与电子工程,2011,9(4):422-425.

[7]马令坤,张震强,党宏社.DDS频率合成器杂散的分析与仿真[J].微电子学与计算机,2007,24(7):132-134.