基于软件无线电的嵌入式系统总线研究及应用

2012-09-28李燕斌黄扬洲刘伟敏

李燕斌,覃 超,黄扬洲,刘伟敏

(中国西南电子技术研究所,成都610036)

1 引 言

软件无线电是一种新型的无线电体系结构,它通过硬件和软件的结合使无线网络和用户终端具有可重配置能力。软件无线电提供了一种建立多模式、多频段、多功能无线设备的有效而且相当经济的解决方案,可以通过软件升级实现功能提高[1]。软件无线电的基本思想是以开放性、可扩展、结构精简的硬件为通用平台,把尽可能多的无线电功能用可重构、可升级的构件化软件来实现。为了便于硬件模块的升级和扩展,软件无线电系统需采用标准的、高性能的开放式总线结构,内部各功能模块间通过标准嵌入式总线相连。

作为系统内部各模块间数据传输和交换的通道,总线是系统的血管和经络,对整个无线电系统而言,其重要性不言而喻。过去的软件无线电系统一般采用VME、PCI等并行总线结构,随着高速总线技术的发展,现在软件无线电系统主要基于高速串行总线结构来设计,未来全光数据交换结构将是发展方向。

2 传统的并行总线传输方式

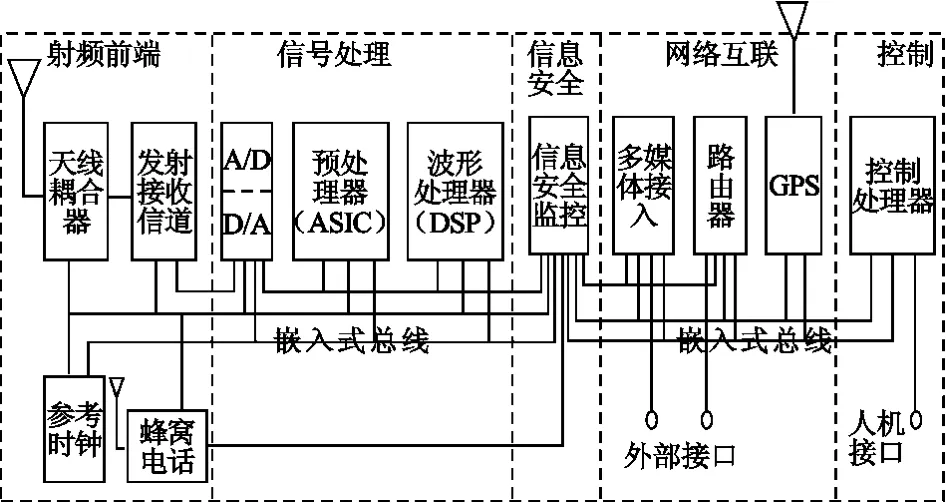

图1所示为典型的软件无线电系统结构。软件无线电系统传统的总线方式大都采用并行架构,VME和CPCI是2种最常用的嵌入式总线方式,其结构形式参见图2。

图1 典型的软件无线电系统结构Fig.1 Typical system frame of SDR

图2 传统的软件无线电嵌入式系统结构Fig.2 Traditional embedded system frame of SDR

CPCI总线实现的是一种Big Pipe的数据传输模式,其采用一组并行线挂接多个功能模块,最高负载模块数量不超过8个(CPCI),可支持较小的电子系统;传输位宽支持 32/64,最高传输速率为528 Mbyte/s,其带宽较宽、速率高,适合作为高速处理和计算平台的接口标准,机械结构和尺寸能胜任恶劣环境下应用。

VME总线相对于CPCI总线来说负载能力更强,其最高负载模块数量达21个,可支持较大的电子系统;但其带宽较窄、速率较低,不适合作为高速处理和计算平台的接口标准,需要增加专用数据传输通道实现实时高速数据传输;机械结构和尺寸能胜任恶劣环境下应用。

随着软件无线电通信系统对带宽需求的增长,VME和CPCI等多负载并行总线技术已很难适应新一代系统的需求。为满足高速率并行传输,其重点已集中在源同步标准并行总线上。典型的源同步并行总线标准有CSIX、SPI-4.2(Double)等,由于其总线时钟频率系统同步并行,传输能力有很大提高,但其要求数据和源同步时钟信号是同步传输的。随着频率的提高,控制时钟和数据信号之间的物理/电气特性偏移也越来越困难,信号质量会受到总线长度限制、信号失真、电路板布线处理通道畸变、抖动等多方面的影响,并行总线结构的局限性日渐显现。通信技术在不断地发展,总线技术相应也在不断地更新,而串行总线结构在高数据交换速率、多模块和具有高速内部交换网络的高端系统上其优势性日益显现。

3 串行总线架构的优势

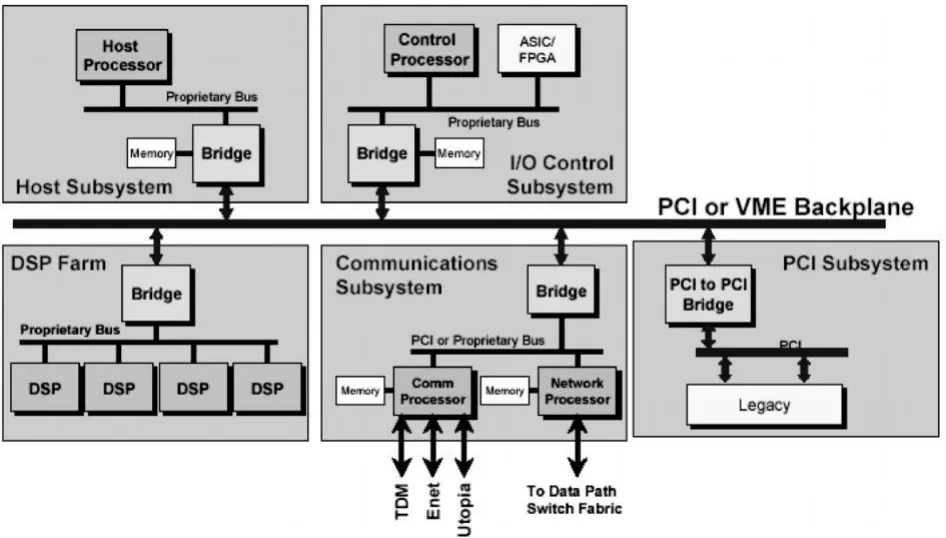

随着通信技术和总线技术的发展,新型软件无线电系统嵌入式总线架构以串行替代并行,以Pointto-Point方式替代Big Pipe方式,以包交换替代电路交换,以Switch Fabric替代共享总线已成为必然。新型的软件无线电系统嵌入式结构如图3所示。

图3 基于串行总线的嵌入式体系架构Fig.3 Embedded system frame based on serial bus

串行总线主要有以下几大优点:

(1)串行传输可以最大限度地减少芯片管脚数,减小背板的尺寸和系统设计造价,提供更多的传输链路,现有的技术已经能够实现千兆级的传输率;

(2)点到点通信方式最大程度地减小了通信链路的负载,有利于进一步提高时钟频率/数据率,同时系统负载模块数量可以大大增加,可满足各种电子系统需求;

(3)由于避免了VME和CPCI等并行总线架构的总线仲裁问题,因此基于串行总线的嵌入式系统模块间可以实现很高的传输效率;

(4)Switch Fabric是利用新一代开关器件结合分组交换技术实现的一种交叉开关网络,系统中多个点到点的通信链路被组织在一起,最终能够实现所有芯片/模块间的任意互连和并发传输。

目前可以支持千兆级的常用串行传输总线包括RapidIO 、PCI Express等。

4 多种高速总线性能比较

可用于软件无线电系统的嵌入式高速串行总线种类很多,目前最为通用的是RapidIO、PCI Express、StarFabric、千兆以太网等,它们都可以提供高速、可靠的点对点互联。

千兆以太网技术是百兆以太网技术的升级,支持10/100/1 000Mbit/s全双工数据传输,最初用于局域网内和广域网内的互联,是非常可靠的互联选择。但千兆以太网技术较RapidIO、PCI Express等技术效率稍低,而且系统延时较大,不适合实时嵌入式系统内部的互联,是系统外部总线接口的良好选择。

RapidIO总线基本规范于2001年完成,2003年该互联规范被国际标准总线和国际电工委员会(IEC)一致通过,这使RapidIO(ISO)成为互连技术方面得到授权的唯一一个系统[2]。串行RapidIO技术是专门为嵌入式系统互联而设计的,只要有足够多的交换机,就可以实现任意结构的拓扑。其传输带宽高,最高可达64 Gbit/s。

PCI Express技术是着眼于最大的兼容PCI总线技术而设计,为了能够兼容传统的PCI总线技术,PCI Express的拓扑结构只能是树形结构。这种结构在PC机和服务器内非常适用,如果合适的话,也能用在嵌入式系统内。但在PCI Express的结构中除了要有交换机,还需要有一个模块来做统一的管理,这增加了硬件的开销。

StarFabric是一种高速、点对点的串行交换总线技术,主要面向实时应用的嵌入式领域的系统级互联,每一链路支持的带宽支撑的带宽达2.5 Gbit/s[3],这些链路可以热插拔。该技术由Star-Gen公司发起推广,目前比起PCI-E和RapidIO总线来说传输速率和效率稍低,应用也没有那么广泛。

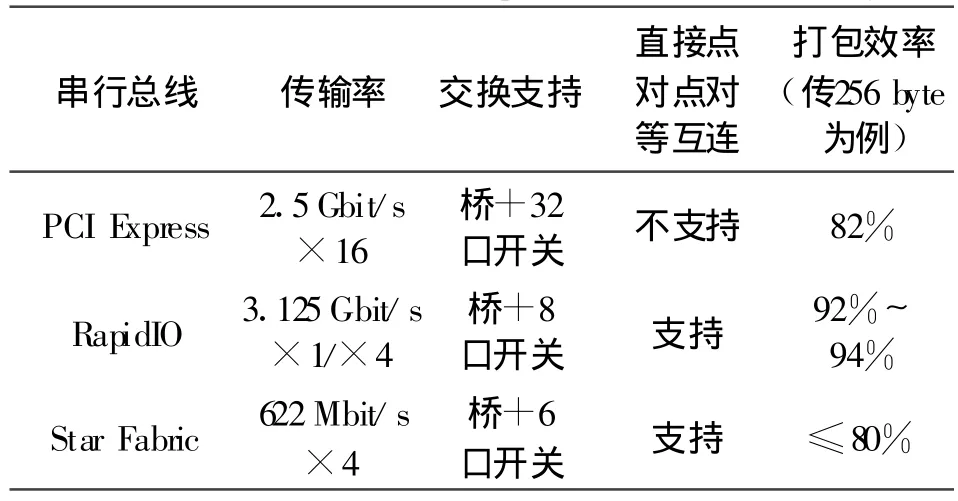

表1给出了几种常用嵌入式串行总线的性能。通过以上几种高速串行总线技术比较可以看出,串行RapidIO技术各方面性能都较好,同时 FPGA、DSP、CPU和很多专用芯片都支持这种标准,是目前软件无线电嵌入式系统内实现互联的最佳选择,其他各类串行或并行总线可以做为子系统或模块内部的数据交换总线。

表1 几种常用的嵌入式串行总线性能Table 1Several common serial bus performance in embedded system

5 在工程中的应用

在基于软件无线电设计思路的某项目中,其架构为4路收发通道,为了支持系统动态可重构能力,在各路中频信号数字化后通过RapidIO总线和交换网络建立了一个基本的点对点网络(如图4)。信号处理模块可以根据需要从网络中选取不同信道的采样信号,或向不同的信道发送调制信号,信号处理模块本身根据不同的通道和工作模式实现软件动态加载。信号处理模块和其他模块间通过RapidIO总线实现数据信息交互。

图4 四路点对点网络结构Fig.4 4-gateway point-to-point network frame

数字中频处理模块将来自接收通道的中频信号ADC采样后送给FPGA,FPGA经数字下变频等信号预处理后,通过RapidIO高速串行总线送往开关交换网络,再经交换判决送到对应的信号处理模块。另一方面,数字中频处理模块FPGA接收来自信号处理模块经开关网络送来的高速串行数据,通过解串处理后送DAC进行数模转换,最后输出发中频信号送往信道发送端。

数字中频处理模块选用Xilinx V5系列FPGA。用FPGA开发RapidIO具有以下优点:

(1)FPGA集成了RapidIO收发器[4],可以支持多达8路串行RapidIO同时传输;

(2)支持RapidIO 2.0标准,提供高达12.5 GHz的带宽,支持标准的1x/4x模式;

(3)实现了RapidIO的三层协议:逻辑层、传输层和物理层;

(4)支持命令、流数据和突发数据的传输;

(5)为应用层提供统一的接口,使软件开发人员可以专注于应用开发。

为了对内数据交换和对外协议处理的方便,本平台的信号处理模块选用TI的DSP芯片TMS320C6455[5]来实现RapidIO总线和千兆以太网接口。TMS320C6455内嵌了SRIO模块,拥有4个全双工的port(端口),支持SRIO 1x/4x串行协议。每个 port支持1.25 Gbit/s、2.5 Gbit/s、3.125 Gbit/s的波特率,每个port可以单独构成1x模式,也可以4个port共同构成4x模式[6]。

本系统平台4个信号收发处理通道,具有8个RapidIO节点,通过专用交换芯片构成交换网络,可实现任意信号处理通道和任意信道收发通道之间高速数据交换,交换芯片数据包延迟小于2 μ s。

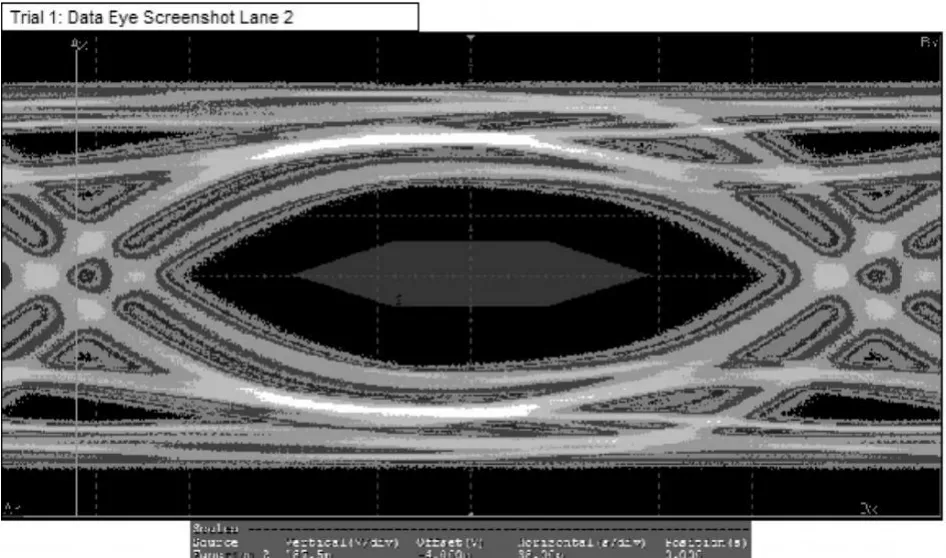

图5是用高速信号分析仪对串行RapidIO链路层电压驱动幅值、抖动总量测试、确定性抖动测试的分析结果,图6是眼图分析结果。通过分析结果可以看出各项指标都还有较大的裕量,从眼图来看,眼睛张开幅度较大,眼图较稳定,交叉点在幅值的中间,由综合测试结果可知RapidIO链路工作稳定,性能良好。

图5 SRIO电气性能测试结果Fig.5 Test result of SDIO electric performance

图6 SRIO测试眼图Fig.6 SRIO test eye-fig

6 结束语

基于软件无线电嵌入式新一代互联技术已经将系统由“bus and board”推向“fabric and blade”。多负载并行总线技术的确已经没有太多的发展空间。新一代互连技术、串行传输、Switch Fabric已经是大势所趋,其中的传输可靠性(包括模块和背板高速信号完整性设计等)、低成本测试性[7]和系统高速数据交换稳定性等是嵌入式系统良好运行的关键因素。

本文通过多种通用并行和串行总线的比较,论证了RapidIO串行总线是当前软件无线电嵌入式系统的优选总线。同时在基于RapidIO总线交换网络实的某应用项目中,实现了数据的高速实时传输与交换,具备了硬件平台良好的开放性和可扩展性以及软件良好的可重构和可升级性,为RapidIO作为软件无线电嵌入式总线进行了有效的实践。当然,要实现一个良好的软件无线电系统,在嵌入式总线高速组网、高稳定性、高可靠性、可测试性和高效传输等很多方面还有很多技术难题,还需要花很大精力去不断完善。

[1]杨小牛,楼才义,徐建良.软件无线电技术与应用[M].北京:北京理工大学出版社,2010.YANG Xiao-niu,LOU Cai-yi,XU Jian-liang.SDR Technology and Application[M].Beijing:Beijing Institute of Technology Press,2010.(in Chinese)

[2]徐俊毅.高速总线竞争日趋白热化[J].电子与电脑,2007(11):37-40.XU Jun-yi.The Competition of High Speed Bus is more and more intense[J].Compotech China,2007(11):37-40.(in Chinese)

[3]黄亚雯,黎想,刘海清,等.基于StarFabric高速总线技术的研究与应用[J].计算机工程,2009(1):221-223.HUANG Ya-wen,LI Xiang,LIU Hai-qing,et al.Research on and Application of High-speed BusTechnology Based on StarFabric[J].Computer Engineering,2009(1):221-223.(in Chinese)

[4]张静.数字信号处理模块中的串行RapidIO设计[J].火控雷达技术,2011,40(1):64-75.ZHANG Jing.Design of Serial RapidIO in Digital Signal Processing Module[J].Fire Control Radar Technology,2011,40(1):64-75.(in Chinese)

[5]黄克武,吴海洲.基于TMS320C6455的高速SRIO接口设计[J].电子测量技术,2008,31(9):143-192.HUANG Ke-wu,WU Hai-zhou.Design of high-speed SRIO interface based on TMS320C6455[J].Electronic Measurement Technology,2008,31(9):143-192.(in Chinese)

[6]Texas Instruments Incorporated.TMS320C645x DSP serial RapidIO user′s guide[EB/OL].[2010-05-12].http://www.ti.com.

[7]Mike Kondrat.PCI高速总线测试挑战[J].半导体技术,2004(4):38-39.MikeKondrat.PCI High-speed Bus Test Challenge[J].Semiconductor Technology,2004(4):38-39.(in Chinese)