用于卫星双向时间传递系统的调制器设计

2012-09-28王学运张升康

王学运,张升康

(北京无线电计量测试研究所,北京100854)

1 引 言

卫星双向时间传递是目前远距离时间同步和校准的高精度和高准确度的手段之一,其工作原理是参加比对的两个地面站向卫星发送定时信号,并接收经卫星转发的对方的定时信号,两站分别通过时间间隔计数器测出对方定时信号与本地定时信号的时差值,然后再根据链路上的各种延时值计算出两地的钟差[1-2]。

卫星双向时间传递系统的核心是调制解调器,目前国内外卫星双向时间传递链路常采用德国timetech公司的stare专用时间传递调制解调器,我国在这种设备的研制方面还有待提高,而且国内外针对卫星双向时间传递调制解调器设计的专门文献较少。本文采用伪码扩频调制体制设计开发了用于卫星双向时间传递的调制器,其原理是在FPGA中将本地1 PPS信号和时间信息伪码扩频,同时进行CRC校验处理,然后再利用DDS实现BPSK调制,并完成70 MHz的中频输出。仿真测试实验表明,该调制器能满足基本的应用需求。下面对系统架构及主要功能模块进行详细介绍,并结合仿真测试结果进行分析说明。

2 调制器总体设计

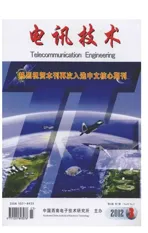

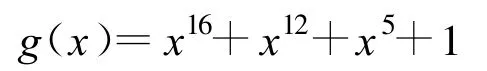

在卫星双向时间传递系统中,本地1 PPS信号和时间信息通过调制器单元的编码调制之后输出,调制器的主要功能是将数据信息按一定格式组帧并进行扩频处理,然后调制成70 MHz中频信号后输出。其原理框图如图1所示。

图1 调制器系统框图Fig.1Modulator system

调制数据有两部分,一是1 PPS秒脉冲信号,二是本地时间信息。1 PPS秒脉冲信号用于实现卫星双向时间传递,它是由参与时间比对的原子钟提供的。在硬件实现时将1 PPS信号用帧头替代,除要保证秒脉冲沿与帧头精准对齐之外,还要保证对1 PPS信号的采样误差要小于系统的同步精度,因此对采样时钟频率要求较高。本地时间信息主要包含时间比对信息、时码信息、电离层时延信息、Sagnac信息及其它信息等,它们对完成卫星双向时间传递起到辅助的作用。对于这些信息数据采用常规处理,将其包含在数据帧中作数据的调制解调。

扩频单元一般选取Gold码作为扩频序列,它是m序列的复合序码,具有良好的自相关和互相关性能。码周期长度一般可选用10的倍数,但要保证截短后的码序列仍然要具有良好的自相关和互相关特性。码周期长度越长,其抗噪声性能越好,但是接收端捕获的速度就越慢。

调制方式选择BPSK调制,BPSK比较简单可在FPGA中实现,也可采用具有调相功能的DDS芯片实现。为提高通信的可靠性,系统中需要加入CRC校验功能,以对可能或已经出现的差错进行控制。CRC码是一种有效的编码技术,它以其检出概率高且易于用硬件实现的优点在移动通信、计算机通信、USB接口、测控等领域有着广泛的应用。

3 调制器的FPGA实现

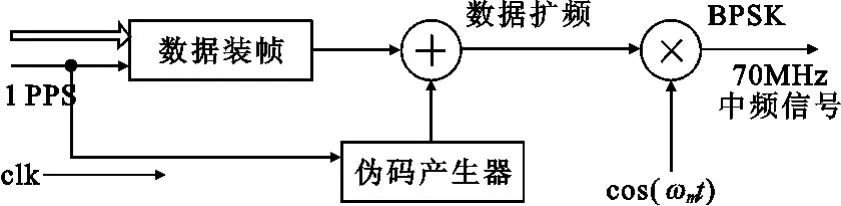

调制器的FPGA硬件实现框图如图2所示。FPGA内部完成的主要工作有数据成帧、扩频及CRC校验、串口通信等,DDS芯片AD9852实现BPSK调制功能。

时钟clk和1 PPS信号是由参与时间比对的原子钟提供的。1 PPS信号是调制器各功能单元的启动和控制信号,是功能实现的协调者和组织者。数据成帧单元、CRC校验单元、扩频单元、码产生单元都是在1 PPS信号的控制下工作的。

图2 调制器的FPGA实现Fig.2Modulator designed based on FPGA

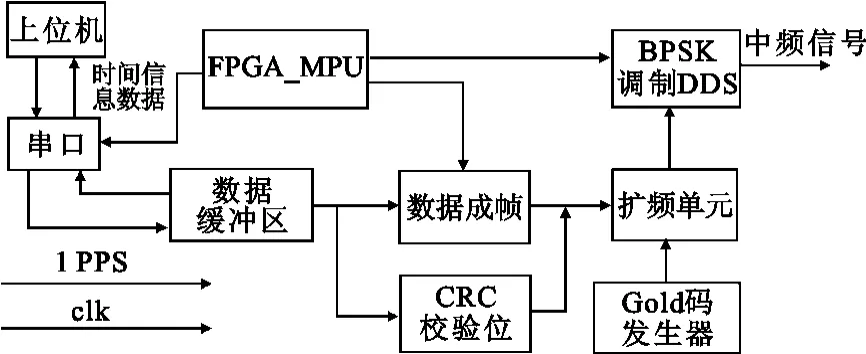

系统数据帧格式如图3所示,其中帧头是13 bit的Barker码序列,数据速率为500 Hz。

图3 数据帧格式Fig.3 Format of data frames

3.1 CRC校验模块的实现

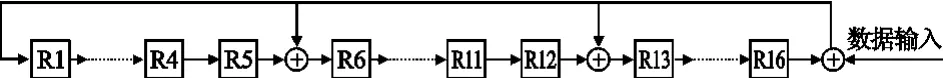

本系统采用CRC-CCITT标准,其生成多项式为

CRC校验的硬件实现所要求的速度并不高,因此可以选用串行实现方式,即经典的LSFR方法[3],其实现结构如图4所示。当最后一位数据进入该结构之后,寄存器中所存储的值就是CRC校验位,然后读取这16个寄存器的值并将其存储到规定的存储区域,最后输出成帧。用Verilog HDL语言可以很方便地实现此算法。需要注意的是,CRC的工作受到1 PPS脉冲信号的控制。

图4 CRC串行结构框图Fig.4 Serial architectural of CRC

该模块的测试方法:人为给定其一串输入数据,通过modelsim仿真观看其输出结果,然后再与matlab计算出来的结果进行比较。

3.2 扩频的硬件实现

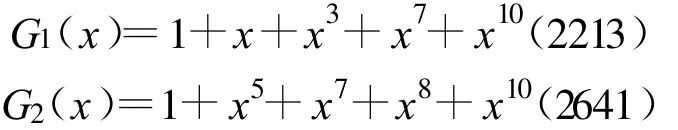

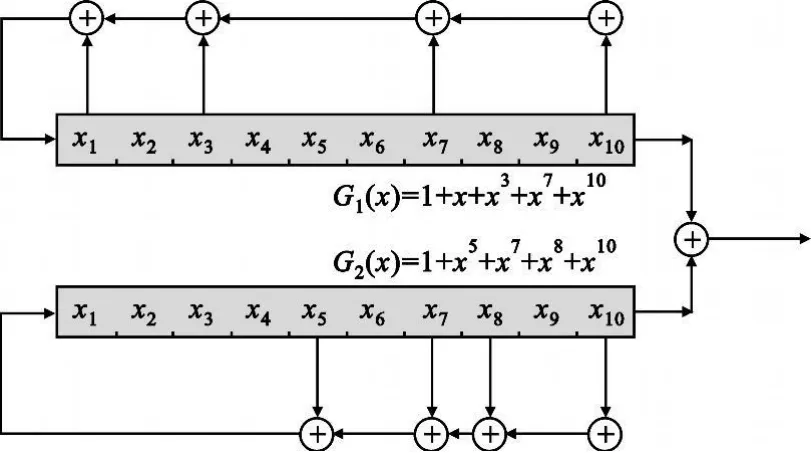

经研究,系统选用的Gold码周期长度为1000,码速率为2.5MHz和5MHz可调。m序列优选对[4]为

其硬件实现结构如图5所示。由于使用的是截短的码周期为1000的码序列,因此当码发生器产生1000个码片后就要将移位寄存器的值设置为初始状态值,而初始状态值可以为全1,也可以为其他非全0值,并且在1 PPS的信号到来时将移位寄存器恢复成初始状态值。最后,将数据帧信息与扩频码序列在1 PPS脉冲信号控制下进行异或运算,从而实现扩频功能。

图5 Gold序列硬件实现框图Fig.5 Design of Gold based on hardware

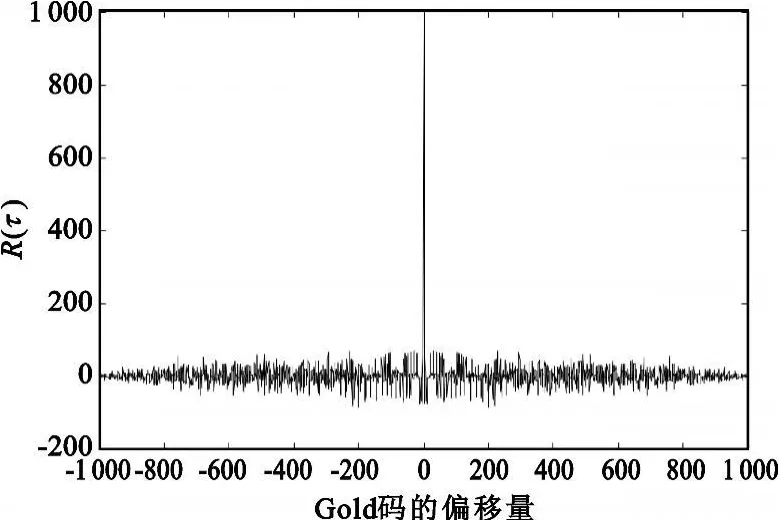

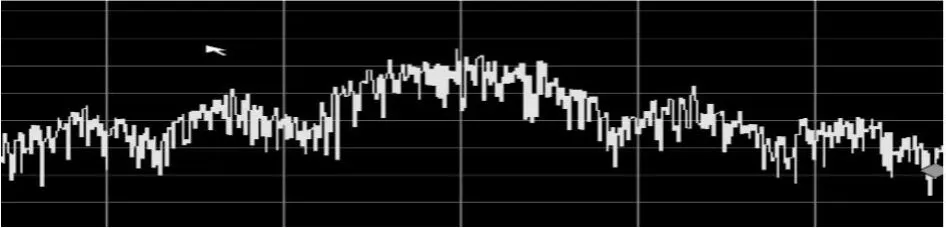

图6 是截短Gold码的自相关仿真图,横坐标表示Gold码的偏移量,纵坐标表示自相关值。从中可发现截取的1000个码片具有良好的自相关性。

图6 截短Gold码序列自相关仿真波形Fig.6Autocorrelation of truncatedGold code

3.3 BPSK调制

系统采用AD9852实现BPSK调制。令AD9852工作在PSK模式,采用差分时钟,频率为10 MHz。对AD9852内部寄存器的配置通过在FPGA中编写的状态机来控制实现。最后将扩频数据调制到70 MHz的中频输出,输出功率为-15 dBm,经过低通滤波之后送到后级卫通变频设备。

4 系统仿真与测试

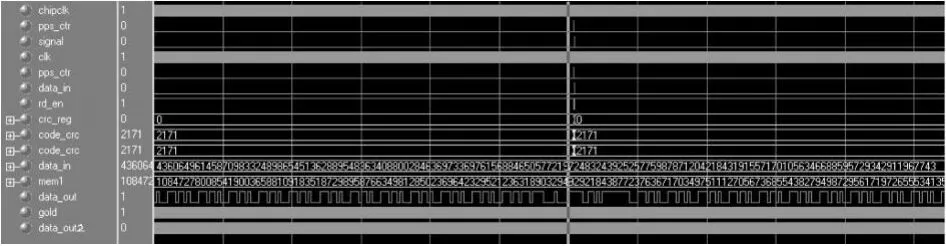

对整个基带系统利用modelsim SE进行仿真,仿真结果如图7所示。该仿真可以验证数据装帧的正确性,由于之前已单独对CRC校验进行了验证,在此,将code-crc以及已知的输入数据和帧头数据按照图3所示的数据帧格式进行组合,然后与mem1的数据进行比较,比较结果说明硬件实现的正确性。

图7 基带仿真结果总体图Fig.7 Simulation results of baseband

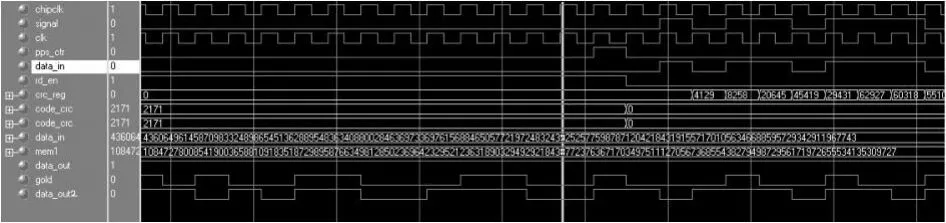

Data-out是数据成帧后的输出数据,此信号同生成的Gold码(Gold信号)进行异或完成扩频,生成扩频信号data-out2。这些动作都是在1 PPS信号控制下完成的。可以看一下中间竖线的细节,见图8。当1 PPS信号到来时,crc以及扩频单元才开始进行数据采集,从而保证动作的一致性。

图8 基带仿真结果细节图Fig.8 Detail simulation results of baseband

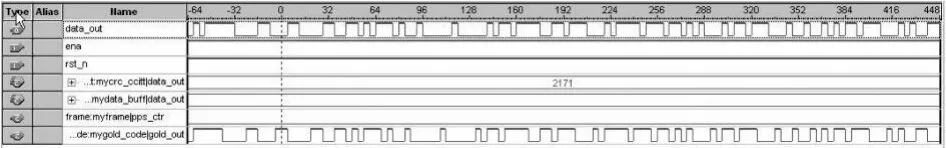

此外,可使用QuartusII自带的ELA工具对数据进行观测,进一步验证硬件实现结果,部分观测结果如图9所示。图10是用频谱仪观测到的中频输出,频谱仪设置如下:RBW设置为100 kHz、VBW设置为100 kHz、AVG设置为on,经测试可得,其中频输出主瓣峰值功率为-15 dBm,中频输出频率为70 MHz。

图9 ELA测试结果Fig.9 ELA test results

图10 中频输出频谱Fig.10 The spectrum of IF

5 结束语

调制解调器是卫星双向时间传递系统的核心设备,本文设计完成了用于卫星双向时间传递系统的调制器,其功能结构与一般的扩频系统相似,但对1 PPS信号需要进行特殊处理。系统仿真测试结果表明,该调制器可以实际应用,并已经过实际试验验证。为与商用设备直接相连组成系统,需要实现调制器的中频输出功率可调,且需考虑实际系统中1 PPS信号的使用方式。同时,该调制器也为解调器的研制工作提供了一个良好的测试平台,可进一步加快解调器的研制步伐。

[1]Kirchner D.T wo-Way Time Transfer Via Communication Satellites[J].Proceedings of the IEEE,1991,79(7):983-990.

[2]李宗扬.时间频率计量[M].北京:原子能出版社,2002.LI Zong-yang.Metrology of time and Frequency[M].Beijing:Atomic Energy Press,2002.(in Chinese)

[3]叶懋,刘宇红,刘桥.CRC码的FPGA实现[J].重庆工学院学报(自然科学版),2007,21(3):85-87.YE Mao,LIU Yu-hong,LIU Qiao.Implementation of CR C Based on FPGA[J].Journal of chongqing Institute of technology(Natural Science Edition),2007,21(3):85-87.(in Chinese)

[4]查光明,熊贤祚.扩频通信[M].西安:西安电子科技大学出版社,1990.ZHA Guang-ming,XIONG Xian-zuo.Spread Spectrum Communication[M].Xi′an:Xidian University Press,1990.(in Chinese)