PCB设计中同步开关噪声问题分析

2012-09-28李颖宏

李颖宏,罗 勇

(北方工业大学机电工程学院自动化系,北京100144)

1 引 言

随着通信设备电路板上大量使用高集成度的高速数字芯片,同步开关噪声(Simultaneous Switching Noise,SSN)问题成为制约高速PCB设计的一个瓶颈[1]。SSN是指当器件上多个逻辑电路或I/O管脚同时处于开关状态,产生瞬间变化的电流,在经过回流路径上存在电感时,形成交流压降,从而引起噪声。如果引起地平面的波动,造成芯片地和系统地不一致,这种现象称为地弹。同样,如果引起的芯片电源和系统电源差异,就称为电源反弹。

根据电源完整性的理论[2],产生SSN的一个主要原因是电源分配系统存在阻抗。具体讲就是从电源的输出端到芯片的输入端存在着一段距离,在这段路径上存在着阻抗。从集中模型来看,相当于串联了集中分布的电阻和电感元件,当一定数量的输出驱动电路同时打开时,就会有很大的电流瞬间涌入这些感性元件中,这种瞬间快速变化的电流会在感性元件上产生感应电动势,引起芯片电源输入端的供给净电压不足或过高。同样,根据信号完整性的理论[3],造成SSN的另一个重要原因是互感耦合,尤其是在芯片封装、PCB边沿周围产生的互感耦合。芯片BGA封装上的焊球与PCB上的过孔都属于紧耦合的多导线结构,每个I/O焊球及其相应的PCB过孔与离它最近的接地焊球和接地过孔构成一个闭合环路,当多个I/O口的状态同时发生变化时,会有瞬态I/O电流流过这些信号环路,这种瞬态I/O电流又会产生变化的磁场,从而侵入邻近的信号环路造成感应电压噪声。

SSN危害是非常大的,会增加电源噪声,影响信号质量和时序,从而导致数字电路误采样。另外,SSN引起的问题一般隐藏很深,只是在器件多个逻辑单元同时开关时才发生,用正常的业务测试方法很难发现,容易漏测,这给设备可靠运行带来了巨大风险。

本文基于同步开关噪声的机理,设计了一种暴露SSN问题的可靠性测试方法,并利用这种方法发现一个具体的Serdes链路异常问题,针对该问题,借助噪声和阻抗分析等实验验证方法找到了PCB设计上存在的缺陷并进行了修改。最后,总结输出PCB设计过程中抑制同步开关噪声的一些方法。

2 SSN可靠性测试方法

可靠性测试就是让设备暴露在各种可能的极限工作状态下进行验证,找到系统的设计缺陷,对同步开关噪声来说,我们可以从产生的机理和常见的危害来设计测试用例。例如,当大量总线在同一时刻切换,会在相邻的管脚上引入串扰噪声,对这种情况,在测试设计时需要对被测设备施加一种特殊的业务负荷,让总线暴露在尽可能大的串扰条件下,并用示波器观察总线信号质量和时序是否可接受。以16位并行总线为例,为了将这种影响极端化,设计测试报文时让16根信号中有15根线的跳变方向一致,即15根信号线都同时从0跳变到1,同时让另一根被干扰的信号线从1下跳到0。可以设计一个循环程序,让16根线依次遍历这种测试场景。

另外,同步开关噪声也可能影响回流路径上的敏感信号,这是并行总线非常恶劣的一种工作状态,为了验证产品在这种工作条件下工作是否可靠,必须在被测设备加上一种特殊的SSN测试报文进行验证。如果被测总线为16位宽,要使所有16根信号线同步翻转,报文内容应该为:FFFF 0000;如果被测总线为32位宽,要使所有32根信号线同步翻转,测试报文内容应该为:FFFF FFFF 00000000。

当然,设备的工作环境也可能有高温或低温的情况,而温度对电路的影响是十分显著的,比如低温和高温时电容的容值会发生变化,低温时器件内部的时序参数会发生漂移,高温时PCB走线的阻抗变大等,因此在进行上述SSN可靠性测试时,还需要增加温度应力来验证系统的可靠性。

3 实例分析

3.1 问题背景

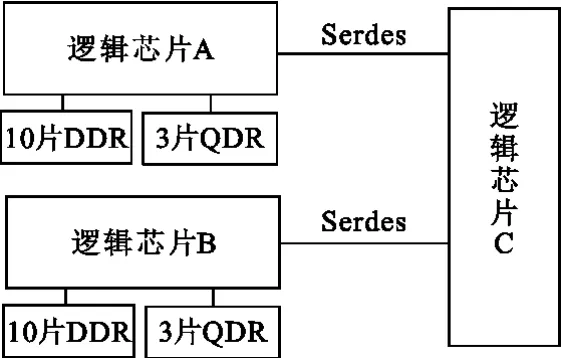

某PCB单板上的逻辑芯片连接关系如图1所示,芯片之间的数据通道都是高速Serdes信号,逻辑芯片A/B外围都挂着10片用来缓存报文的随机存储器DDR和3片用来进行流量管理的QDR,逻辑芯片A/B和DDR之间通过高速并行总线互连,该并行总线的工作时钟频率高达400 MHz,并且信号数量众多,拓扑结构复杂。在PCB上器件布局密度越来越高的情况下,这些高速信号可能会遇到同步开关噪声等问题,对于这些可能存在的风险,从硬件可靠性角度,我们按照SSN可靠性测试方法设计了测试报文,让被测单板在高温60°、低温-10°的温度条件下带业务进行环境试验。发现在逻辑芯片A/B的DDR总线上运行伪随机二进制序列(PRBS)报文时,Serdes链路业务传输正常;而当运行按SSN报文时,Serdes链路业务传输出错,其中,逻辑芯片A出现异常的Serdes链路为链路6、链路4、链路0,逻辑芯片B出现异常的Serdes链路为链路10、链路8、链路4、链路2、链路0。

图1 逻辑芯片连接关系Fig.1 The connected relation of the logic chip

3.2 原因分析

根据SSN报文设计原理,由于总线同时开关,按照公式 V=N·L·(di/dt),N就是总线的位宽,此时同步开关噪声V是最大的。而PRBS码流是伪随机码,同步开关的驱动器小于总线位宽,产生的噪声V要远小于SSN码流。运行SSN报文时,产生的过大同步开关噪声可能使高速Serdes信号受到干扰,噪声裕量降低导致数据采样出错。

SSN报文翻转时通常情况下最直接的表现是DDR供电1.8 V的噪声会较大,但是从实测结果来看,运行PRBS码流时噪声为24 mV,运行SSN报文时噪声为32 mV,两者之间差别并不大,说明1.8 V电源平面的电源完整性比较好,对问题Serdes链路影响应该不大。那么DDR接口的同步开关噪声怎么影响到了逻辑芯片间的Serdes链路呢?查看PCB版图,出问题的Serdes链路和DDR接口的同步翻转数据信号线均布在15层和17层,两者空间上物理距离比较近,串扰比较大。另外,该两层到16层的1.5 V电源平面间距比到14层和18层要近,因此,15层和17层上的信号回流都将以16层作为参考平面,根据信号回流原理,当运行SSN码流时,DDR的数据信号同步翻转的同时,在数据信号线上产生瞬间变化的大电流,其参考平面上返回电流也将产生瞬间大的波动,噪声将会瞬间增大。很明显,DDR接口在同步翻转时,在参考平面16层1.5 V电源平面产生较大的回流。同时,出问题的Serdes链路参考的1.5 V平面局部地区只有一个100 μ F的电容(C1),没有足够滤波电容,大的回流波动就产生了波动的噪声,在该位置测试1.5 V电源的噪声,当运行SSN报文时C1处的噪声达到140 mV,运行PRBS码流时噪声为42 mV,变化很大,用频谱分析仪测得该噪声频点为400MHz,正好为DDR工作时钟。相反,有大量滤波电容的QDR接口处1.5V电源平面,在SSN报文情况下噪声仅有16 mV左右。结合前面的分析,由此可以明确,正是由于问题Serdes链路以1.5 V电源平面噪声比较大的局部地区为参考平面,平面上的高频噪声耦合到Serdes链路上,降低了时序裕量,导致链路传输异常。

另外,仔细分析单板的层叠设计,发现15层更靠近16层的1.5 V电源平面,理论上在15层的链路应该更加容易出问题。逻辑芯片A模块的链路6、链路4和逻辑芯片B模块的链路10布在15层,从测试中也发现这几条链路出错的概率最高,进一步验证了DDR数据总线的同步开关噪声导致了Serdes链路传输异常。

既然明确Serdes链路异常是由于DDR数据信号的SSN造成1.5V电源平面噪声偏大影响的,那么就降低干扰源,优化1.5 V电源平面滤波,保证敏感信号参考平面尽量干净。改善噪声主要有以下手段:

(1)在不影响信号时序及噪声裕量的情况下,降低逻辑芯片A/B的DDR接口输出驱动能力;

(2)调整逻辑芯片A/B的DDR接口的输出相位,使10个DDR接口错相输出;

(3)DDR的SSN主要体现在数据信号上,15层和17层数据信号目前都以16层的1.5 V电源平面为参考平面,将15层、17层DDR的数据信号分别和4层、8层的DDR地址信号调换,降低噪声源,避免问题serdes链路信号都参考噪声大的16层1.5V电源平面;

(4)在DDR模块周围添加100 nF的电源滤波电容,为回路电流提供低阻抗通路;

(5)在Serdes信号路径参考的16层1.5 V电源平面上放置滤波电容;

(6)在不影响通流的情况下,优化1.5 V电源平面阻抗,没有使用该电源的地方都铺地平面。

根据芯片资料,芯片更改驱动能力会影响时序,更改逻辑芯片A/B的10个DDR接口输出相位,配置比较繁琐,最好能从PCB滤波方面去优化解决问题。所以在Version B版本PCB设计时,我们重点从优化Serdes信号参考的16层1.5 V电源平面噪声的角度去优化PCB设计,在1.5 V电源平面上增加了回流滤波电容。

Version B版本单板回板后,使用了和Version A版本单板相同的SSN报文在温箱里进行带业务验证,验证结果基本上也证明了我们上面分析的正确性,但是仍然没有彻底解决问题。逻辑芯片A模块所有链路在SSN测试报文下,高低温不再出问题,表明优化到位;但是逻辑芯片B模块链路10在高温下仍然会出问题,出错概率相比Version A版本单板降低。

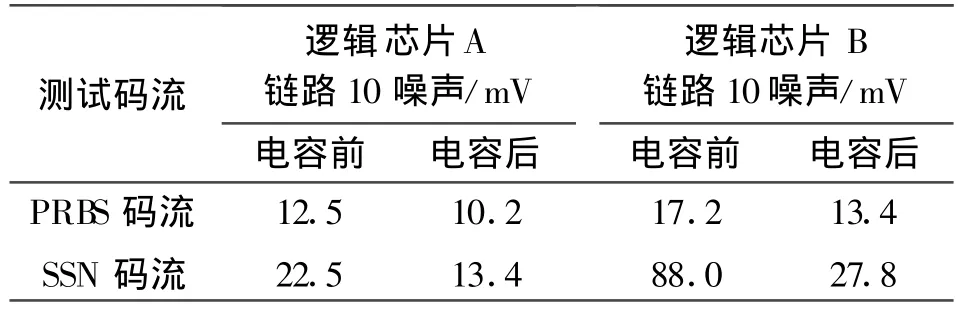

为了对比A/B模块问题Serdes链路信号受到的耦合噪声大小,我们关闭了Version B版本单板A模块的链路10和B模块的链路10,去掉交流耦合电容,测试耦合电容前后Serdes信号线上的静态噪声大小,如表1所示。

表1 Serdes信号线上静态噪声Table 1 The static noise of Serdes signal line

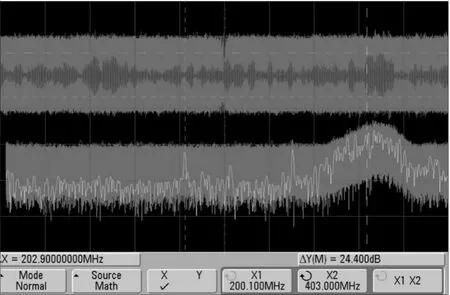

从上面的对比测试数据可以很清楚地看到,在由PRBS码流变成SSN码流下,电容前这段走线耦合到的噪声变化非常明显,增加近60 mV。从噪声频谱上也可以看出明显的噪声频点在400MHz左右,如图2所示。

图2 Serdes信号线上噪声频谱Fig.2 The noise spectrum of Serdes signal line

很明显,在Version B版本PCB上,我们优化了耦合电容后这段走线的参考平面噪声,但是却忽略了耦合电容前这段走线受到干扰的可能性,导致我们没有优化彻底。链路10电容前这段走线走在11层,参考的电源平面主要是12层的1.0 V,相应位置上的滤波电容也很少,同时也有大量的DDR接口的数据信号线走在11层,所以在SSN码流下电容前这段走线耦合的噪声相比PRBS码流变化非常大。

因此,决定直接优化12层的1.0 V电源平面,在Serdes信号沿路添加100 nF的去耦电容。共计添加10枚电容,加工了Version C版本单板。Version C版本单板回板验证,测试结果和预料的一样,采用Version B单板相同的参数配置,多块单板顺利通过温度应力试验,Serdes误码问题完美解决。

4 同步开关噪声抑制方法

通过Serdes链路异常问题的分析,可见同步开关噪声对电路可靠性的影响越来越大,随着器件速率的不断提高,这一影响将更加明显,那么,如何尽量避免SSN问题带来的危害呢?一般我们在单板PCB设计时可以参照如下规则进行设计。

(1)DDR存储类器件,数据总线最好不要走在同一层,降低SSN情况下对参考平面噪声的影响;可以考虑和地址总线布在同一层,数据总线优先参考其I/O电源。

(2)Serdes等敏感信号尽量避免走在参考平面边缘。

(3)Serdes等敏感信号和RAM数据总线在PCB上尽量拉开距离,布在不同走线层,避免参考同一电源平面。

(4)在满足通流的情况下,电源平面不要铺得太大。在有高速I/O信号或者Serdes敏感信号参考该平面情况下,在没有使用该电源的地方做铺地处理。

(5)电源平面不能大面积没有高频去耦电容,尤其是平面边缘有高速信号跨分割的地方推荐添加去耦电容,去耦电容可以使用分立电容或埋容[4]。

(6)进行电源平面谐振仿真分析评估,尽量避免和存储类器件工作频率产生谐振。

(7)在紧靠芯片的电源输入端加足够的退耦电容,可以起到稳压的作用,并最好使用L型或π型LC滤波电路。

(8)I/O的布线层优先靠近TOP面,减小信号换层引起的环路电感。

(9)逻辑芯片的pin排布时,将堆在一起的同步I/O散开,减小空间耦合引起的环路电感,未使用的pin脚接地或电源处理,增加返回路径。

(10)在芯片内加旁路电容或选用低阻抗特性封装的芯片。

(11)对于抑制甚高频的同步开关噪声,可以考虑采用高阻抗电磁表面结构(EBG)[5],采用EBG结构作为PCB衬底时,可以实现在微带电路衬底中集成具有很宽阻带的滤波器,当和其他电路元件有机地结合起来时,可节省电路空间。

5 结束语

总的来说,文中提到的根据单板上逻辑单元或I/O接口的总线结构,在测试阶段构造特殊报文,让这些接口同步翻转的测试方法,能快速发现设计缺陷,暴露电路板上潜在的同步开关噪声问题,提升单板的可靠性。同时,根据具体问题总结出的抑制同步开关噪声的方法既是前期设计阶段需要遵循的原则,也是后期解决问题的方案。后续我们还可以通过等效模型的方法,在前期对单板可能存在的同步开关噪声风险进行仿真分析,提前规避问题。也可以设计出可编程的SSN测试程序,让芯片厂家内嵌在控制器里,可以在可靠性测试阶段直接调用验证,增强单板的可测试性。

[1]Altera Corp.Simultaneous Switching Noise(SSN)Analysis and Optimizations[M]//Quartus II Handbook(Version 11.1,Volume 2).San Jose′,CA:Altera Corp.,2011.

[2]Brain Young.Digital Signal Integrity Modeling andSimulation with Interconnects andPackage[R].New York:Prentice Hall PTR,2000.

[3]Steve Sharp,Panch Chandrasekaran.Managing signal Integrity[J].Xcell Journal,2005(3):82-85.

[4]侯红英.埋容在高速传输板卡设计中的应用[J].电讯技术,2011,51(5):123-126.HOU Hong-ying.Applicationg of Buried Capacitance in Design of High-Speed Transmission Board[J].Telecommunication Engineering,2011,51(5):123-126.(in Chinese)

[5]黄小龙.一种抑制同步开关噪声的新颖电磁带隙结构[J].电子科技,2010(5):55-57.HUANG Xiao-long.A Novel EBG Structure for SSN Suppression[J].Electronic Science and Technology,2010(5):55-57.(in Chinese)