基于SOPC嵌入式系统中软硬件协同设计方法研究

2012-09-25董雷刚祝裕璞程书伟王冬星

张 丹,董雷刚,祝裕璞,张 华,程书伟,王冬星

(大庆师范学院 计算机科学与信息技术学院,黑龙江 大庆 163712)

0 引言

随着半导体技术的高速发展,集成电路的规模不断增大,以及大规模可编程逻辑器件的出现,使得整个系统集成在单个芯片上并实现在系统可编程成为可能,这就是片上可编程系统SOPC(System on a Programmable Chip)。它支持并行SOPC技术具有灵活的设计方式:可裁减、可扩充、可升级,并具有软硬件在系统可编程的功能。

基于 FPGA(Field-Programmable Gate Array,即现场可编程门阵列)的片上可编程系统SOPC 设计近年来在半导体领域中呈现出高速增长态势,成为系统级设计者的首选,但是随着系统规模的不断增大,使得整个系统的设计变得非常困难,系统开发周期越来越长,而现今的嵌入式电子产品对系统的开发周期是非常敏感的,因此快速、高效的设计方法是一个值得探讨和研究的问题。对于嵌入式系统设计中存在的这些问题,研究者提出了一种软硬件协同设计的新方法。

SOPC系统是软件和硬件的综合体,系统中许多功能模块既可以由硬件来完成,也可以由软件来实现。硬件实现的特点是性能高、速度快,但是成本较高、灵活性差;而软件实现的特点是灵活性好、成本较低,但是性能差。因此,设计实现过程中如何兼顾系统的功能和性能(如功耗、成本、面积等)需求,使它们达到一种最优组合,这正是软硬件协同设计方法所要解决的主要问题[1]。

1 传统电子设计方法

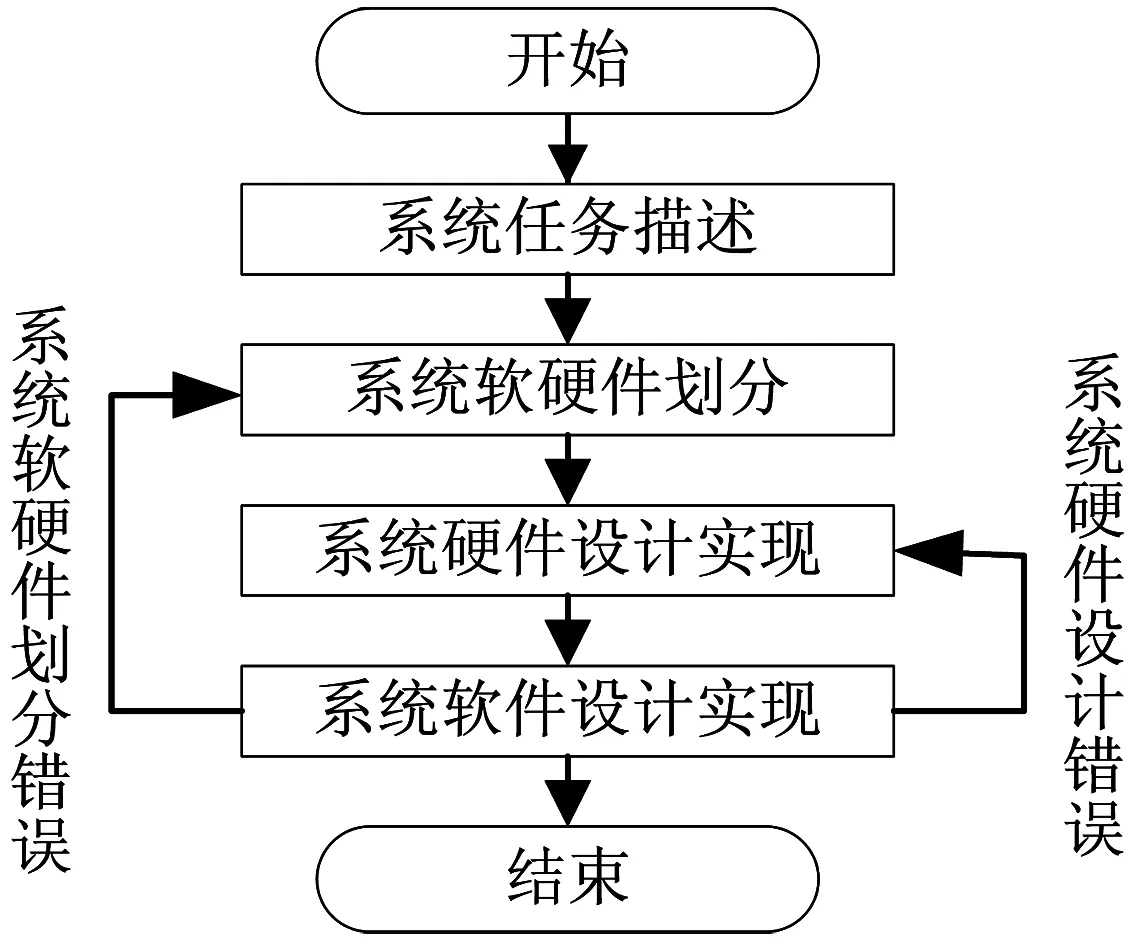

目前,国内外的企业普遍采用的是传统的嵌入式系统设计方法。这种方法的步骤是首先对系统的需求描述进行定义,然后进行系统的软硬件划分,划分好以后就开始分别进行硬件和软件的设计,如果硬件和软件设计中发现错误将直接返回到软硬件的划分。传统的嵌入式系统设计流程如图1所示。

图1 传统的嵌入式系统设计流程

这种方法的缺点如下:

1)系统的软件设计和硬件设计的并行性低,设计周期较长。这种设计流程采用先对硬件进行设计,然后是软件设计。即硬件设计好之后,在此硬件基础之上进行软件设计。此串行化的设计方法当硬件设计完成再进行软件的调试时,如果发现硬件设计出现错误,纠正错误就要付出高昂的人力、物力代价。不能对系统的软硬件进行协同验证,导致了设计重复性工作的次数大幅度增多,加大了设计成本。

2)系统设计层次低,系统级设计依赖于手工,设计的大规模超出了设计人员的能力,系统的软硬件的开发流程缺少沟通与协调,导致设计效率的降低。

3)对于定制的嵌入式处理器不支持,嵌入式处理器为固定的模块,不支持设计的可重用。

2 软硬件协同设计方法的特点

因为传统的嵌入式系统设计方法的这些缺点,人们开始探索新的设计方法来适应高速发展的嵌入式系统,这种方法就是软硬件协同设计方法。它早在1993年就已经成为嵌入式系统中系统级设计领域的研究方向和热点。

软硬件协同设计方法的特点如下[2-3]:

1)软硬件协同设计技术采用并行设计和协同设计的思想,使得设计开发周期缩短,设计效率大大提高。

2)软硬件协同设计采用了统一工具和表示方法,对软硬件合理进行划分,合理分配系统功能,对成本、性能、功耗等各个方面进行权衡,尽可能得到最优化的设计。

3)软硬件协同设计采用软硬件协同仿真的方法,对整个系统进行全局的设计验证。

软硬件协同设计对于设计的抽象层次有了很大的提高,而且拓宽了设计的覆盖范围,它可以使嵌入式系统的设计效率更高,速度更快。软硬件协同设计是一种新的设计方法和思想,它不仅仅是一种设计技术,它是要把软件和硬件的设计联系起来,以免这两部分设计过早的独立起来。软硬件协同设计技术现在正处于发展阶段,有很多理论还不成熟,然而这种技术极大地提高了嵌入式系统的设计效率,有很大的研究价值和社会意义。

3 软硬件协同设计的开发流程

嵌入式系统设计的主要任务包括:系统任务描述,系统建模,用来实现系统的功能需求;对系统进行适当的软硬件划分,用以满足性能要求、降低成本和功耗;系统的协同综合和对系统实现及规范性进行仿真。软硬件协同设计的目的是使系统的各影响因素之间可以相互协调地完成系统功能。软硬件协同设计基本流程如图 2 所示。

3.1 系统任务描述

要想设计一个SOPC系统,第一步是要明确系统的需求,也就是系统的性能和要实现的功能,接下来是对系统进行建模。SOPC系统的模型主要有有限状态机模型、数据流图模型、任务流图模型、离散事件模型、Petri网模型等。建立一个对软硬件通用的系统功能描述方法,来解决系统的统一描述问题,目前通常情况下是采用系统描述语言的方式。这样在软硬件划分后,才能编译并映射成硬件描述语言和软件实现语言,为系统的软硬件协同工作提供有力的保证。

图2 嵌入式系统软硬件协同设计基本流程

3.2 系统软硬件划分

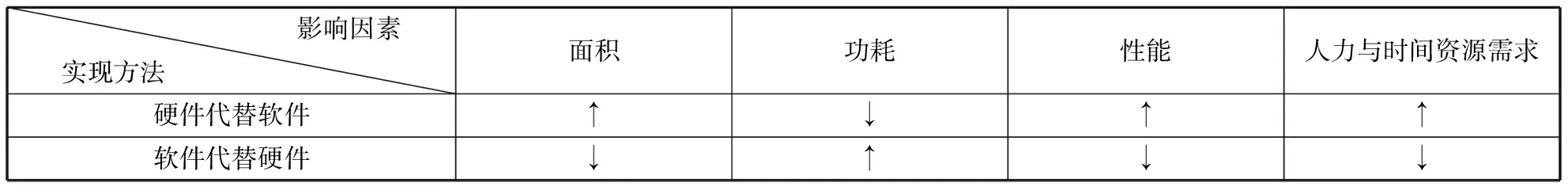

在传统的嵌入式设计方法中,软件和硬件的开发过程是割裂开的,它们之间缺乏沟通。这样就使得系统的设计效率很低。针对这一缺点,提出软硬件协同设计的方法,这种方法中软硬件系统的划分是软硬件协同设计中关键的步骤之一。系统中硬件实现部分对系统的性能有决定作用,通常硬件实现部分速度较快,但是成本控制在这部分也起着决定性的作用。系统中软件实现部分通常具有很大的灵活性,决定着系统配置的灵活性,但是要占用一定的FPGA逻辑单元和耗费一定的时间。如表1所示。表1指出了系统是由硬件实现还是软件实现对芯片面积、功耗、性能和人力与时间资源需求的影响,合理的软硬件协同设计方案,对嵌入式系统的设计有很重要的作用。软硬件的合理划分,在满足系统功能的基础上,能够充分发挥硬件处理的快速和软件控制灵活的特点。

表1 软硬件设计对系统的影响因素

软硬件划分的结果追求的是提高系统运行速度、减小面积、降低成本、减少功耗。但软硬件划分通常是一个传统的难题,由于划分问题本身就具有很大的难度,而且SOPC具有巨大的搜索空间,所以情况更加严峻。现如今自动划分算法仍然不能取代有经验的设计者。划分的方法基本上从两个方面入手:一是面向软件,从软件到硬件要求满足时序的特点; 二是面向硬件,从硬件到软件要求降低成本。在进行划分时,要考虑整个目标系统的体系结构、粒度、软硬件实现的成本等各个因素。划分完成后,产生软硬件系统的分割的界面,提供给软硬件进行沟通、验证和测试使用。常用的软硬件协同划分算法有模拟退火算法、遗传算法等。遗传算法和模拟退火算法的互补性比较好,将这两种算法相结合而形成的遗传退火算法将继承这两者的优点,在软硬件划分上的效能很好,现在这种智能算法是软硬件划分算法领域的一个研究热点[4]。

3.3 软硬件协同综合[5]

软硬件划分完成以后,分别进行软件系统和硬件系统的设计实现。对划分完成的系统进行设计的阶段叫做综合。这个步骤的主要任务是将划分完成的系统的描述转换成为可以综合的硬件描述和可以编译的软件程序。构建包含软件和硬件的实现结构描述的设计转换过程。比如说划分后的描述可以翻译成为Verilog HDL(硬件模块)和C(软件模块)。软硬件协同综合包含以下三个步骤:

1)处理单元分配,决定嵌入式系统由哪些处理器、DSP及专用硬件等体系结构级别的单元组成;

2)任务指派,决定系统当中哪些功能由硬件处理单元实现,哪些功能由处理器用软件来实现;

3)任务调度,决定分配给每个处理单元上任务的开始时间和执行顺序。

3.4 软硬件协同仿真

软硬件协同仿真验证是对整个系统设计的正确性和性能指标确定的一个评估阶段。在嵌入式系统设计的各个阶段,可以把仿真验证分为系统级仿真、行为级仿真、寄存器传输级(RTL 级)仿真和门级仿真。系统级仿真一般情况下用来评估系统的整体功能和对算法的正确性的验证;行为级仿真可以对所设计的逻辑进行仿真,但不会考虑目标器件的特性,比如容量,延迟等,行为级仿真可以使用高级的语句,比如报错语句、文件读写语句、浮点格式等,但这些语句通常都是不能在目标器件中实现的;寄存器传输级仿真检查各模块的逻辑功能是否正确,然后,将通过仿真的各模块集成在一起,对整个系统进行功能仿真,这一阶段的仿真没有包括硬件电路的时间信息,因此,只能从逻辑功能方面对设计进行验证;门级仿真是将使用综合软件综合后生成的门级网表或者是实现后生成的门级模型进行仿真,不加入时延文件的仿真。

典型的软硬件协同仿真一般是在CPLD或FPGA的 开发环境下,在Quartus II下运行。系统如果采用的 IP 核等一些资源已经进行了单独的验证,则对它的门级或者RTL级的仿真验证可以省略。

4 软硬件协同设计工具简介

4.1 Altera公司的Quartus II

Quartus II是最近几年由Altera公司推出的一套用于PLD(programmable logic device) /FPGA器件开发综合性的集成良好的开发环境。用来完成系统的输入(原理图、VHDL、VerilogHDL和AHDL(Altera Hardware Description Language))、综合、布局布线、仿真、编程等完整的PLD设计流程。该软件使用方便,一直保持PLD 器件领域的性能上的领导地位。

4.2 SOPC Builde

SOPC Builde是在Quartus II中可以快速建立、开发及维护系统的一个强大的SOPC设计平台,用来构建基于总线的系统,它集成在Quartus II的所有版本当中。这个系统包含了一些模块,比如Nios II处理器、存储器、DSP、总线等IP核,SOPC Builde可以自动地生成片上Avalon总线和总线仲裁器等一些所需的逻辑,以便将微处理器核、外围设备、存储器和其它IP核相互连接起来。 SOPC Builde提高了设计集成度和可重用性,提高了FPGA设计人员的工作效率。

4.3 Nios II IDE

NIOS II IDE(NIOS Integrated Develop Environment) 是Altera公司所提供的专门用来开发SOPC的一套集成开发环境,所有的软件开发任务都可以在此环境下来完成,这些功能包括对代码进行编辑、编译、连接、调试和下载等一些功能。NIOS II IDE还提供了一个统一的用于所有的NIOS II处理器系统的开发平台。NIOS II IDE还集成了许多软件组件,比如RTOS(Real-time operating system)、LWIP(Light Weight Intellectual Property)等软件组件,并且提供了图形化的参数编辑方式。因此基于这个平台可以很方便地进行SOPC应用软件的设计。

4.4 Cadence Virtual Component Co design (VCC)

第一个为IP复用所设计的工业系统级HW/SW co-design开发平台环境。在设计的早期就可以确定软硬件划分的临界体系结构。通过电子供给链进行交换设计信息,为SOPC和系统库提供必要的框架。

4.5 System C

一种能够支持系统级软件和硬件协同设计仿真和验证,基于C/C++的通过类的对象扩展的建模平台,以C++为基础的新型的建模方法,方便IP 交换和系统级设计。在这种语言描述中,进程是最基本的构造块。System C的源代码可以用来综合硬件,可以把它写的硬件描述综合成为门级网表,以便于IC(integrated circuit)实现,或者综合成一个Verilog HDL或VHDL的RTL的描述,以便于FPGA综合。用System C开发的硬件模型可以用标准的C++编译器来编译,经编译后形成一个可执行的应用程序,设计人员可以通过console来观察系统的行为,验证系统的功能和结构。

5 结束语

基于SOPC的软硬件协同设计方法能够在宏观上把握复杂系统,克服了传统设计方法存在的缺点,能够充分挖掘软件和硬件之间的协同性,对系统的软硬件进行正确划分,并能够选取合适的IP,建立系统的设计平台和验证平台,推动软件和硬件的并行研发,降低设计风险,缩短开发周期,在嵌入式系统的设计中发挥着重要的作用。随着逻辑设计和EDA工具的支持,基于SOPC的软硬件协同设计技术在嵌入式应用系统的设计中发挥越来越重要的作用,将是今后 IP-SOPC 设计领域中的最核心技术。

[参考文献]

[1] 徐海涛. 基于SOPC的软硬件划分算法研究[D].哈尔滨:哈尔滨理工大学硕士学位论文, 2009.

[2] Y.B. Li,T. Callahan. Hardware-software co-design of embedded reconfigurable architectures[C].Proceedings of the 37th Annual Design Automation Conferenc, 2000:507-512.

[3] J. Schlessman, C.Y. Chen, W. Wolf,et al. Hardware/Software Co-Design of an FPGA-based Embedded Tracking System[J].Computer Vision and Pattern Recognition Workshop, 2006,123:17-22.

[4] G. Stitt , R. Lusecky , F. Vahid.Dynamic Hardware/Software Partitioning[M].California: Anaheim, 2003:20-25.

[5] 韩玺.SOPC软硬件协同设计的方法研究[D].北京:北京交通大学硕士学位论文, 2006.