多DSP的以太网并行系统任务下载技术研究

2012-09-11杨彦鑫

杨彦鑫,黎 英

(1.云南大学信息学院,昆明 650091;2.云南农业大学工程技术学院,昆明 650201;3.昆明理工大学信息工程与自动化学院,昆明 650093)

1 引言

计算机仿真[1]是指以计算机为主要工具,运行真实系统或预研系统的仿真模型,通过对仿真模型的输出信息分析与研究,实现对实际系统运行状态和演化规律的综合评估与预测。它是分析评价现有系统运行状态或设计优化未来系统性能与功能的一种技术手段,现已广泛应用于国民生产的各种领域。随着人们对复杂、大型系统如基因工程、气候预报、军事演习、电力系统等的深入研究,原有串行仿真系统已经不能满足庞大的计算量需求,并行仿真系统越来越受到人们的青睐。并行系统的基本构建方式主要有两种,第一种是使用大型机甚至巨型机,将多个CPU通过高速总线连接,这种方式的管理效率、数据传输速度和可靠性都非常高,整个并行程序的运行效率也很高。但是,这种方式购置、维护、管理费用非常昂贵,系统的扩展性及可移植性也较差[2]。并且由于系统成本太高、专业性太强、难以被中、小型企业和普通用户所接受;第二种方法使用分布式计算模式,多主机间通过通信线路互联,将复杂的计算任务分解至各主机进行计算,这种方法相对于大型机来说,价格低廉、可扩展性强、可移植性好。目前来说基于TCP/IP协议的以太网多DSP并行处理系统应用较广。该系统通过以太网将一组高性能的DSP连接起来,在并行操作系统和集成开发环境的支持下统一调度,可以实现高效的并行计算。这种系统的开发设计较为方便,也具有很好的扩展性能[3]。但是,由于在系统的各并行节点间数据的传输采用TCP/IP协议,将大量精力应用在保证数据传输的可靠性及数据流的控制上,这不仅需要花费较多的处理时间来实现协议,占用大量的系统资源,而且通信也存在有不确定性。直接将这种耗时长、不确定的通信技术所构成的并行系统应用于实时仿真时,仿真的速度将受限于并行节点间的数据通信开销,实时性难以得到保证。

实时仿真需要仿真系统的仿真时间和自然时间完全一致[4]。为了满足仿真时间与自然时间一致的要求,通过对以太网TCP/IP通信协议的优化和裁剪,设计出基于MAC层数据传输的通信方式,大大降低了系统通信开销,提高了通信速率,为并行实时仿真系统的实现奠定了基础。并行仿真系统中,并行计算需要将复杂的任务进行划分,通过调度算法将任务分配至各节点机进行处理。因此,各节点机必需预先下载经过编译系统编译完成的任务。但当并行系统中节点数量较多时,每个节点单独下载任务的方式将变得非常繁琐复杂,不仅耗时长而且增加很大工作量。如果任务调度的算法改变,也会遇到同样的问题。通过对DSP启动方式及加载方式的研究,提出一种多重加载的下载方法,很好地解决了并行任务下载至各节点机的问题。

2 并行系统结构

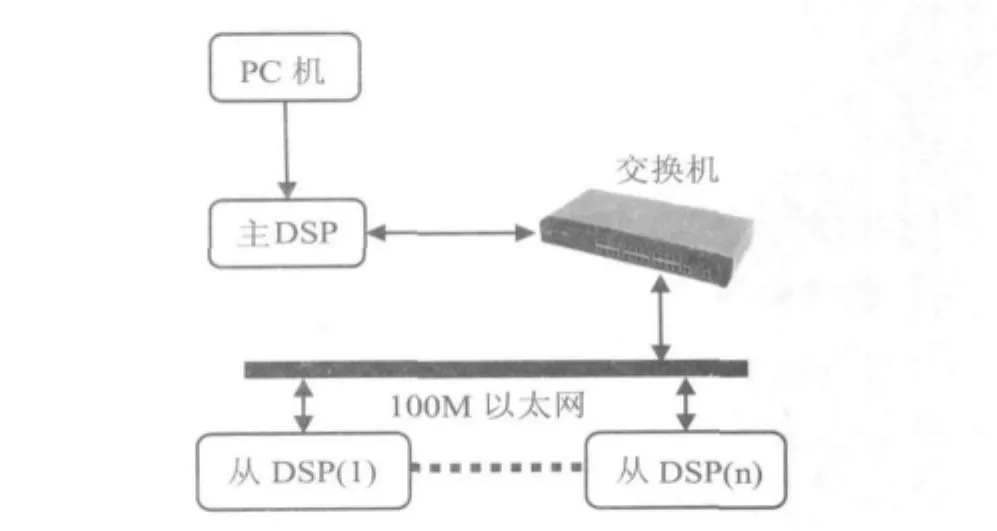

多DSP并行系统的基本性能主要取决于处理单元即DSP的处理速度、并行系统的结构和任务调度算法三个方面[5]。三者之间紧密联系、相互依赖。此并行系统使用美国模拟器件公司(ADI公司)生产的Blackfin系列ADSP-BF548型号的DSP芯片作为处理单元,该芯片具有强大的运算能力,主频最高可到600MHz,并具有低功耗、片内资源丰富、控制功能强的特点。虽然BF548已经在片内融入了并行处理技术,如多级流水线、并行计算单元等,但多片并行的技术处理任务速度更快,性能更强,并且扩展灵活,是并行技术发展的主要方向。多片DSP如何实现通信控制与数据交换,即如何建立起多DSP之间的信号连接通道SLC(Signal Link Channel)[6],是并行系统结构设计的核心问题。并行系统采用基于以太网的双重网络体系主从结构设计,如图1所示。

图1 并行网络结构

在双重网络结构下,各节点的通信和数据交换方式也分为两类。第一类是主机与各从机间的通信。在此方式中主机相当于大型机的中央管理系统,负责对并行仿真的任务进行划分和调度,将划分好的任务分配到各处理机上,使任务按照一定的顺序执行,从而将复杂任务分解成简单任务,获得了很高的处理性能,主机还可以对各从机进行管理。对于复杂的并行系统,在管理和调度任务时需要使用操作系统。μC/OS-II是一种基于优先级的抢占式多任务操作系统,包含了实时内核、任务管理、时间管理、任务间通信同步(信号量,邮箱,消息队列)和内存管理等功能。μC/OS-II的最大特点是源码公开,可方便的将其移植到本系统中,并且方便维护。由于系统采用静态任务调度方法,主要保证数据传输的稳定性和可靠性,对任务的划分和调度没有非常严格的时间要求,所以在这类网络中使用以太网TCP/IP协议提供可靠的传输服务;第二类是从机间的数据交换。在并行计算的过程中,多任务间具有一定的耦合性,各从机间需要交换数据信息。为满足实时仿真的要求,DSP间的数据交换采用了通信速度较快的基于MAC地址的网络传输机制。标准的TCP/IP协议栈在传输过程中占用了大量CPU资源和通信开销,由于DSP并行系统中所有节点均处于同一局域网内,可将上层协议进行裁剪,保留MAC层以下的协议,使用MAC地址进行数据传输。经测试,在以交换机组成的局域网内,采用MAC层收发数据,可以降低通信开销、提高通信速率,特别是短数据帧的通信速率。另外,从机可根据并行仿真的需要通过交换机灵活配置成各种并行结构,具有很好的可重构性和扩展性。这种双重网络结构的并行系统继承了大型机和分布式系统的优点,既有运算能力强、可靠性高、管理效率良好的特点,又具有成本较低、扩展灵活、可满足仿真实时性要求的优势,是一种可应用于中、小企业和个人用户的高效廉价的并行仿真系统。

3 BF548启动方式及装载文件结构

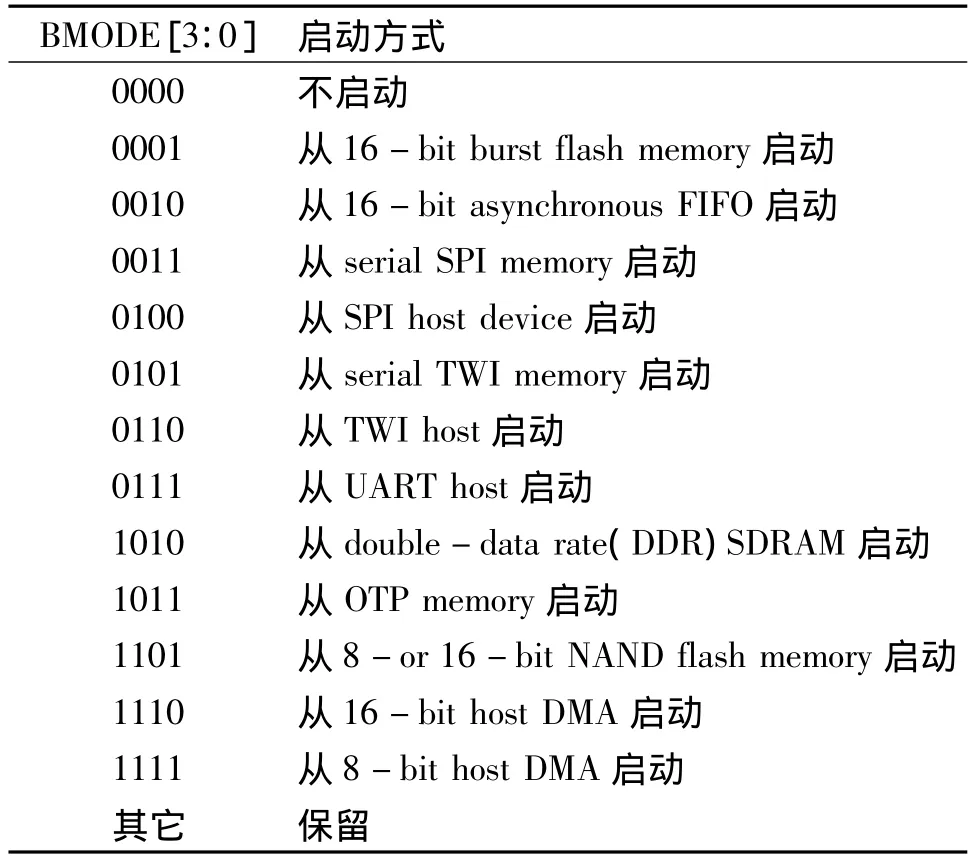

BF548芯片的引导启动方式非常灵活,有多种启动方式可供用户选择,在不同的启动方式下,初始执行的程序地址并不相同,读取执行文件的方式也不相同。为了使DSP能够从固定地址执行并行计算程序,必需掌握BF548芯片的启动方式。BF548的启动方式由芯片的4根BMODE输入引脚决定,各种启动方式见表1。

表1 BF548启动方式

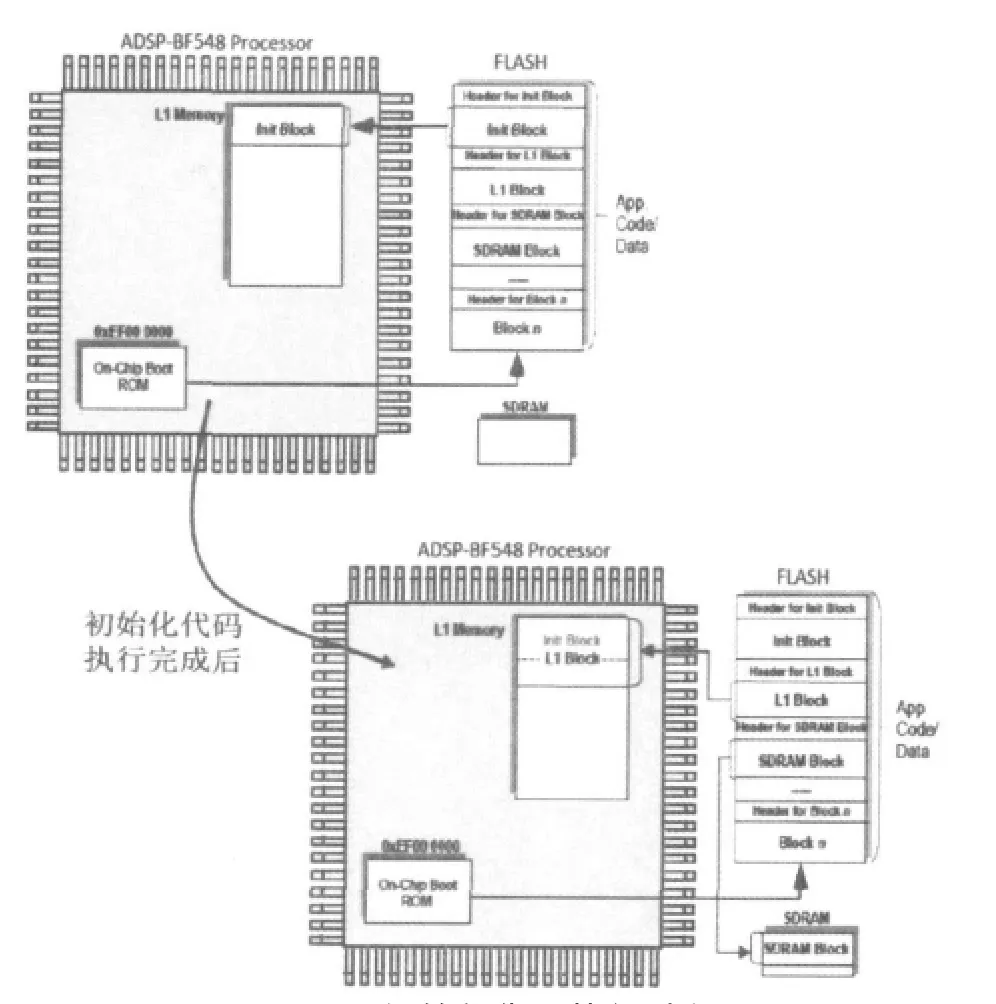

为了便于任务下载,各 DSP选择从16-bit burst flash存储器启动的方式,该方式的启动过程可以看作是从flash存储器上读取启动码流即LDR文件到DSP内部的L1存储器和SDRAM存储器的过程,如图2所示。启动工作全部由位于DSP存储器地址0xEF000000到0xEF0003FF的片上Boot ROM中的启动代码完成。DSP处理器复位后会从Boot ROM的起始地址开始执行,启动代码首先读取启动码流最开始的16个字节,它们是启动文件的头信息,内核通过分析包含在这16个字节中的DMACODE位来确定DMA通道的宽度和步长,同时配置DMA通道。一旦DMA的配置完成后,启动码流将以子块为单位读取LDR文件中的其它程序信息。启动代码根据头信息中的目标地址(Target Address)和子块长度(Byte Count)将启动码流的每个子块传输到各存储器的指定位置。当所有的块传输完成后,启动代码会自动跳转到应用程序的起始地址开始执行,默认的地址为0xFFA00000存储在EVT1寄存器中,通过更改EVT1中的地址值可实现执行不同位置的应用程序。

图2 BF548启动过程

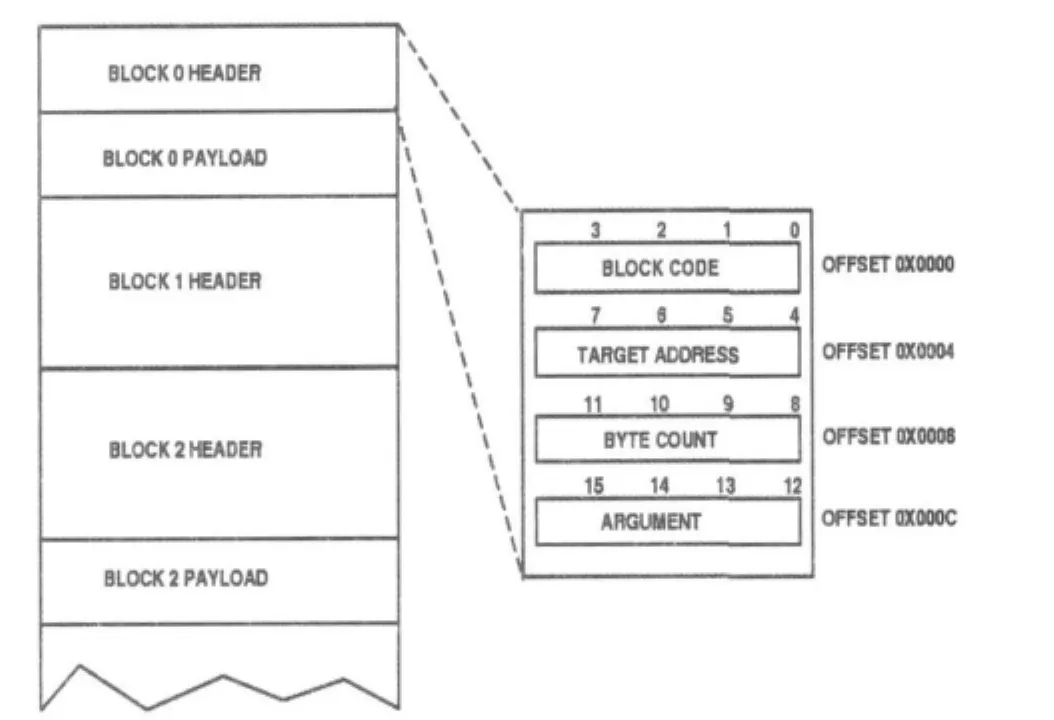

装载文件,即LDR文件,它包含着全部的启动码流,LDR文件保存在静态存储器中供启动使用,它可以通过ADI公司提供的集成开发和调试工具VDSP中的 ELFLOADER功能生成。ELFLOADER解析输入的可执行文件(DXE文件),生成带有头信息的启动码流。LDR文件由多个子块组成,每个子块可以分为头部和负载两个部分,但有部分特殊子块只有头部,没有负载区。头部区共有16个字节,分别存储着头部的CRC校验数据、标志符、目的地址、块大小和块参数。头部标志符共有16字节,如图3所示。

图3 LDR文件头部标志符

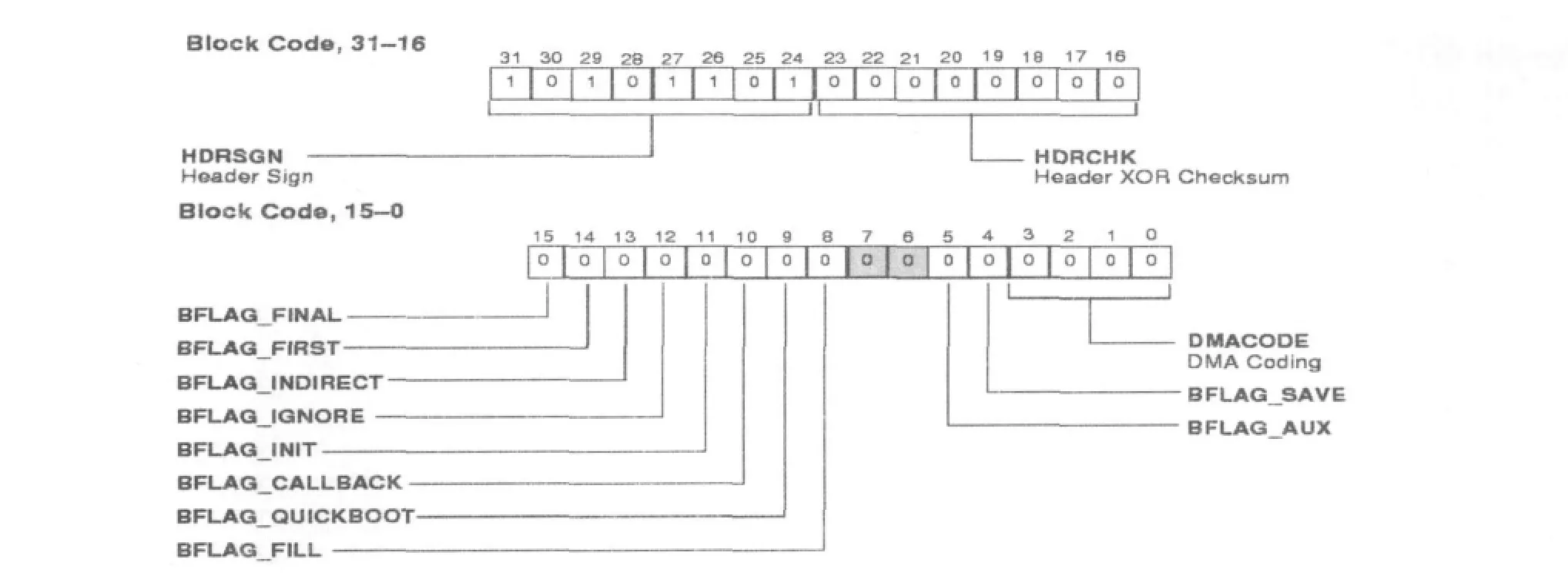

前4字节为区块代码(Block Code),如图4所示。

其中 BFLAG_FINAL、BFLAG_FIRST、BFLAG_INIT和BFLAG_FILL四个标志符,它们分别指出当前的子块为结束块、开始块、初始化块和填充块。一般情况下每个LDR文件都会存在这四个标志符。不同的区块会令Boot ROM对启动过程产生不同的影响。利用启动文件中的区块加载方式,可设计多重加载的启动方式。

图4 区块代码

4 任务下载方法

4.1 通信程序

要实现将PC机上VDSP编译好的LDR文件从主DSP下载到各从DSP中,要通过以太网,所以PC机和DSP中必需有网络通信程序以实现数据传送。加载文件传输过程主要保证传输的正确性,对时间和效率的要求不高,所以上下位机都使用TCP/IP通信协议。PC机中使用VC++编写程序,利用TCP/IP协议提供的编程接口套接字(Sockets)开发通信程序。套接字的实质是通信端点的一种抽象,它提供一种发送和接收数据的机制。Windows Sockets规范以U.C.Berkeley大学BSD UNIX中流行的Sockets接口为范例定义了一套Windows下网络编程接口。Windows Sockets具体实现使用Winsock应用程序接口(API),Windows Sockets提供面向连接的流式套接字(Stream socket)和面向无连接的数据报套接字(Datagram socket)。在VC++中可利用MFC封装的CAsyncSocket和CSocket两个类中的相关函数实现。在BF548 DSP中,使用μC/TCPIP协议栈,μC/TCPIP是一个精简、实时、高效的TCP/IP协议栈,可支持64位的嵌入式处理器,所有代码遵循Motor Industry Software Reliability Association(MISRA)C标准,可根据用户需要裁减,它的原码公开,可方便移植入BF548平台。运行μC/TCPIP需要多任务的实时操作系统,操作系统需要具有计数信号量,μC/TCPIP中封装了支持μC/OS-II的软件层,所以与μC/OS-II配合使用更加方便。μC/TCPIP可支持Sockets、TCP、UCP、IP等协议,所以 PC 机和DSP均可使用相同的方式创建网络连接。主从DSP间进行文件传输也通过Sockets套接字进行编程,程序流程如图5。为确保LDR文件传输的正确性,主从DSP间经过多次交互,从DSP还应将写入flash的文件读出后再发送至主DSP进行校验,如果校验失败,要求主DSP重新进行传输。

图5 通信程序流程图

4.2 初始化代码

在BF548芯片复位后,系统均要通过启动过程加载可执行的程序进入L1或RAM中执行,加载过程通过芯片Boot ROM中的启动代码完成。DSP选择从16-bit burst flash存储器启动的方式,系统将加载保存在flash中的启动码流。在DSP的启动过程中,首先要判断flash中是否已经存储了并行任务的LDR文件,如果没有,则需要加载通信程序和主DSP通信下载并行任务的LDR文件;如果已经存储了并行任务,则直接加载并行任务的LDR文件进行并行仿真计算。为了实现此过程,必需运用BF548初始化块预先加载的特性实现多重加载。BF548在实际应用程序加载之前,允许预先加载初始化块。当Boot ROM中的启动程序检测到某些子块的头部标志符具有BFLAG_INIT标志时,认定这些区块为初始化块,并首先将这些区块载入DSP的存储器中,然后发出一个调用指令给其目标地址来执行该块。初始化块中可包含一段初始化代码(Init Code),用C语言函数,原型如下:

void initcode(ADI_BOOT_DATA*pBootStruct)也可以声明一段初始化代码。初始化代码执行完后将通过一条RTS指令返回BOOT ROM继续加载过程,将要加载区块的地址保存在DSP的R0寄存器中,在初始化代码中改变R0的值,可实现加载不同LDR文件。初始化代码执行完成后,已加载的初始化块将被其它区块所覆盖。其过程如图6所示。

图6 初始化代码执行过程

4.3 多重加载程序流程

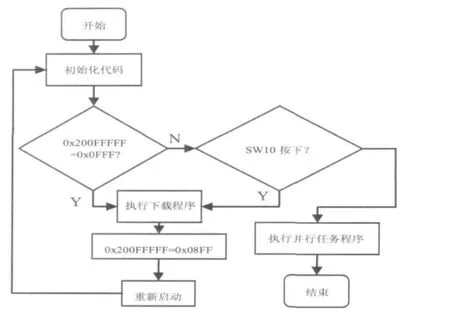

在初始化程序中,判断Burst Flash存储器中地址为0x200F FFFF的存储单元存储的内容是否为0x0FFF,如果是,则表明DSP中没有下载过并行任务程序,初始化程序修改R0寄存器内容,调用网络下载程序,网络下载程序将与PC机通信,下载任务程序,将下载的LDR文件写入存储器0x20100000之后的空间,同时修改0x200F FFFF地址单元内容为0x08FF;如果不是,则设置定时器延时一段时间,用户在定时时间内如按下SW10按键则重新下载LDR文件,更新任务程序,更新完成后重启DSP;如未按下SW10按键则调用下载好的任务程序开始并行仿真过程。程序流程图如图7所示。

图7 多重加载过程

5 结束语

在对比传统并行系统结构的基础上,构建了一种基于以太网的多DSP并行仿真系统。系统采用双重网络结构,静态任务调度管理和并行实时仿真过程使用不同网络架构进行数据通信,使得调度管理过程灵活、可靠;通过对以太网协议的裁剪优化,缩短了并行结点间数据通信的时间,为并行系统实现实时仿真提供了基本保证。同时提出的利用多重加载方式下载并行任务的方法具有很强的实用价值。特别是当并行系统中DSP数量较大时,可节约大量的下载时间和工作量,减少通过仿真器下载时硬件插拔造成的损伤,也可以用于DSP程序的在线升级更新。此方法不仅适用于ADI公司的BF548芯片,略加修改还可应用于其它Blackfin系列DSP中。但是此方法也有一定的局限性,要求DSP板必需有以太网接口,由于移植了操作系统和网络协议栈,对于存储器的容量也有一定的要求,因此该方法仍需进一步完善。

[1]胡峰,等.动态系统计算机仿真技术综述[J].计算机仿真,2000,17(1):1 -7.

[2]任晓明,等.网络并行计算系统模型[J].计算机工程与应用,2001(15):118-119.

[3]柳林,李涛,荆涛.基于多节点多核的样本级并行仿真技术研究[J].系统仿真学报,2010,22(11):2597-2599.

[4]姚新宇,黄柯棣.仿真中的时间和实时仿真[J].系统仿真学报,1999,11(6):415 -417.

[5]黄飞,等.网络互联型多DSP并行处理系统设计[J].计算机工程,2007,33(23):230 -232.

[6]杜金榜,等.多DSP并行处理系统的设计与开发[J].计算机测量与控制,2006,14(5):658-660.