应变硅技术在纳米CMOS中的应用

2012-09-05刘国柱王树杰

刘国柱,姚 飞,王树杰,林 丽

(1.中国电子科技集团公司第58研究所,江苏 无锡 214035;2. 南通航运职业技术学院船舶与海洋工程系,江苏 南通 226026)

应变硅技术在纳米CMOS中的应用

刘国柱1,姚 飞1,王树杰2,林 丽1

(1.中国电子科技集团公司第58研究所,江苏 无锡 214035;2. 南通航运职业技术学院船舶与海洋工程系,江苏 南通 226026)

应变硅技术具有迁移率高、能带结构可调的优点,且与传统的体硅工艺相兼容,在CMOS工艺中得到广泛地应用,尤其是MOS器件的尺寸进入纳米节点。文章综述了应变硅技术对载流子迁移率影响的机理,并从全局应变和局部应变两个方面介绍了应变硅在CMOS器件中的应用。同时,将多种应变硅技术整合在一起提升MOS器件的性能是未来发展的趋势。

应变硅;CMOS;全局应变;局部应变

1 引言

随着微纳技术的发展,CMOS工艺已经进入了(超)深亚微米阶段,晶体管的特征尺寸已达纳米级。SiO2作为栅介质,厚度已降低到物理极限(约1nm),使MOSFET性能恶化,如关态漏电、功耗密度增大、迁移率退化、短沟道效应、热载流子效应等。因此,通过等比例缩小的方法提高当前主流硅CMOS器件的性能,受到越来越多物理、工艺的限制。为了使集成度继续延续摩尔定律的发展速度,必须开发与硅工艺兼容的新材料、新结构和新性质,如SOI技术、应变工程技术(strained engineering)、浅结工程技术(shallow junction engineering)、低接触电阻及多层内连技术(multilayer interconnect)等。

近年来,与硅工艺相兼容的应变硅技术在MOS器件中表现出了独到的优势而备受关注。高质量的应变硅的生长可以把应变工程和带隙工程引入成熟的硅工艺中。在MOS器件的沟道中引入应变,不仅可以提高载流子的迁移率,且有助于抑制DIBL效应。据报道,同尺寸的应变硅与体硅MOSFET相比,功耗减小1/3、速度提高30%、特征频率提高50%以上、功耗延迟积仅为后者的1/5~1/6、器件的封装密度提高50%。因此,应变硅技术在高速和低功耗领域有很大的应用潜力。

本文主要简述了应变硅技术对载流子迁移率影响的机理,同时从全局应变和局部应变两个方面综述了其应用,并简述了各自在MOS工艺中应用的优缺点。

2 应变对载流子迁移率的影响

在MOS器件的沟道中引入应变可以提高载流子的迁移率,其主要原因来源于两方面:载流子有效质量的降低和能谷间声子散射率的降低[1,20,25,26]。在室温的条件下,与体硅相比,应变硅中的电子迁移率增加约60%~95%[3,4],空穴迁移率增加约30%[3]。公式(1)描述了迁移率(μ)与散射率(1/τ)、载流子的有效质量(m*)之间的关系[1]。

2.1 电子迁移率的影响

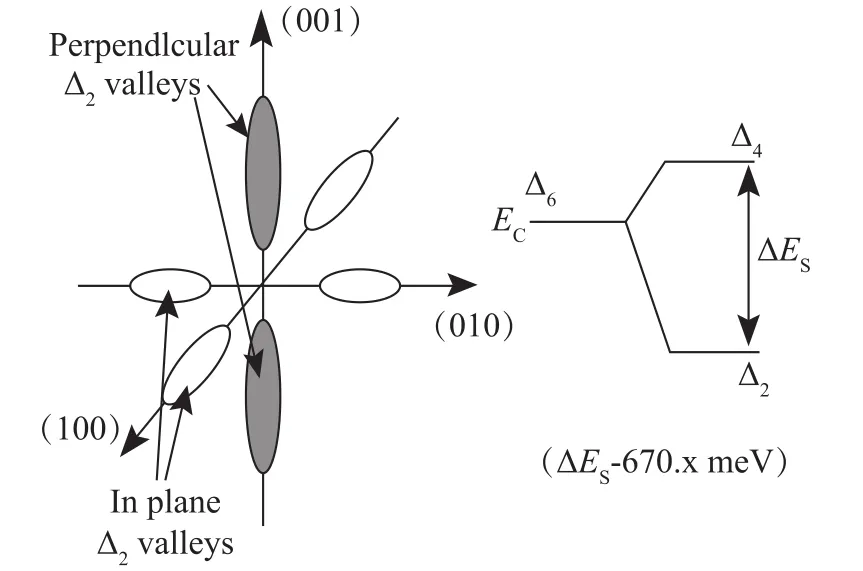

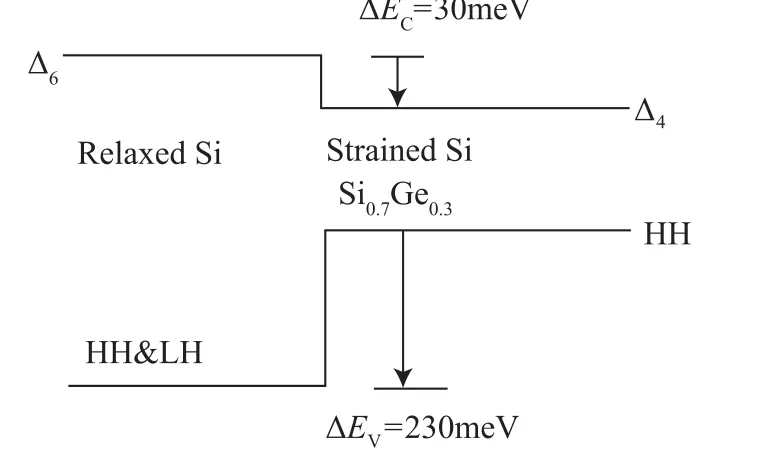

硅的导带由于应力的作用,使得其能级的分裂,由六重简并能谷分裂为两组:两个降低的能谷沿与界面垂直的轴向Δ2;四个抬高的能谷沿与界面平行的轴向Δ4,如图1所示。低能谷与高能谷之间的能级差的经验值为0.67xeV(其中x是指Ge的摩尔数)。大多数反型层电子占据两个低能谷,在于界面平行方向输运,具有较低的导带有效质量,导致低场迁移率增大。谷间声子散射率因能谷分裂而降低。由于初末态之间的能差增大,在非等能谷之间的散射率降低[1,2,22,25]。

图1 双轴张应力诱导导带能级分裂[1]

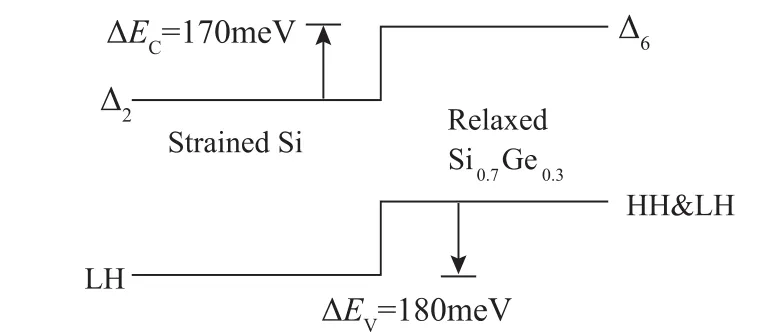

如在弛豫SiGe层上外延顶层Si,在顶层Si的厚度小于临界厚度时,硅原子与弛豫SiGe晶格常数达到匹配,则顶层中的硅原子收拉伸作用,在in-plane方向形成了双轴应变。该结构的应变硅的导带和价带均有加大的突变量,电子势阱和空穴势阱处在不同的层中,导带突变量处于应变硅中,价带突变量集中于SiGe层,形成Ⅱ型量子阱,如图2所示。Ⅱ型量子阱由于导带和价带的能带突变量都比较大,电子和空穴的迁移率都有所增强,因而应变Si/SiGe在CMOS工艺中既可做N型也可做P型器件。

图2 在弛豫Si0.7Ge0.3层上生长双轴应变硅层的能结构图

2.2 空穴迁移率的影响

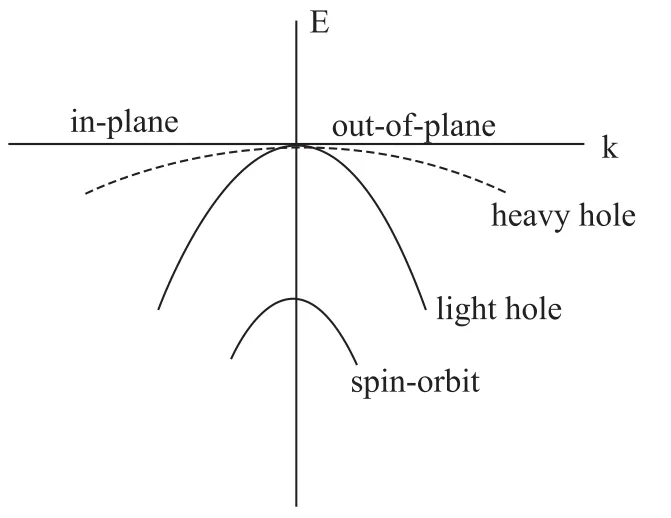

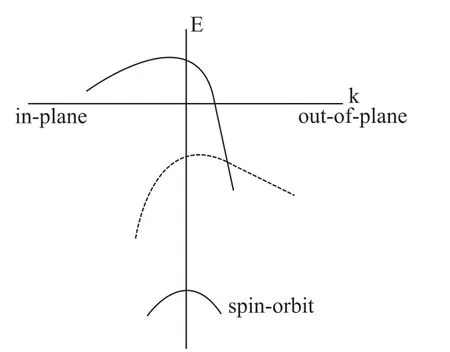

硅的价带因应力的作用,引起价带结构的畸变使得有效空穴质量降低,同时,因布里渊区中心的重空穴带与轻空穴带分离降低了带间散射[2,22,25],如图3、图4所示。价带顶轻重空穴带在Г点的能量分裂值可用下式近似表示[2]:

其中x是弛豫Si/Ge中的锗的摩尔分数。

减小平面内电导有效质量或增加平面外电导有效质量可增强载流子迁移率。当电场增加时,即应变引起能带的卷曲,使得单轴压应变引起的轻空穴带平面外电导有效质量高于重空穴的,进而单轴压应变比双轴的伸张应变更易提高空穴的迁移率[22,25,26]。

如Si1-xGex薄膜淀积在Si衬底上,薄膜在平行于衬底方向受到压应力。此时电子势阱和空穴势阱都处在Si1-xGex层中,这种能带称之为I型量子阱,如图5所示。Si1-xGex薄膜的价带突变量明显,与之相比导带突变量非常小,因此该结构适用于PMOSFET。

图3 体硅价带示意图[2]

图4 应变 Si1-xGex价带示意图[2]

图5 在弛豫硅层上生长单轴应变Si0.7Ge0.3层的能结构图

3 应变硅技术的发展

应变硅应用到MOS器件中,首要条件是应变硅材料的性能要达到器件级的标准,如表面粗糙度(RMS)、缺陷(defect density)和位错密度(TD)等。因此如何获得高质量的应变硅材料一直是研究的热点。应变硅技术主要包括两方面:

(1)全局应变,指在整个圆片都生长应变硅层,不同的沟道位置具有相同的应力大小和方向,通过引入压应力(compressive strain)或伸张应力(tensile strain),提高载流子的迁移率;

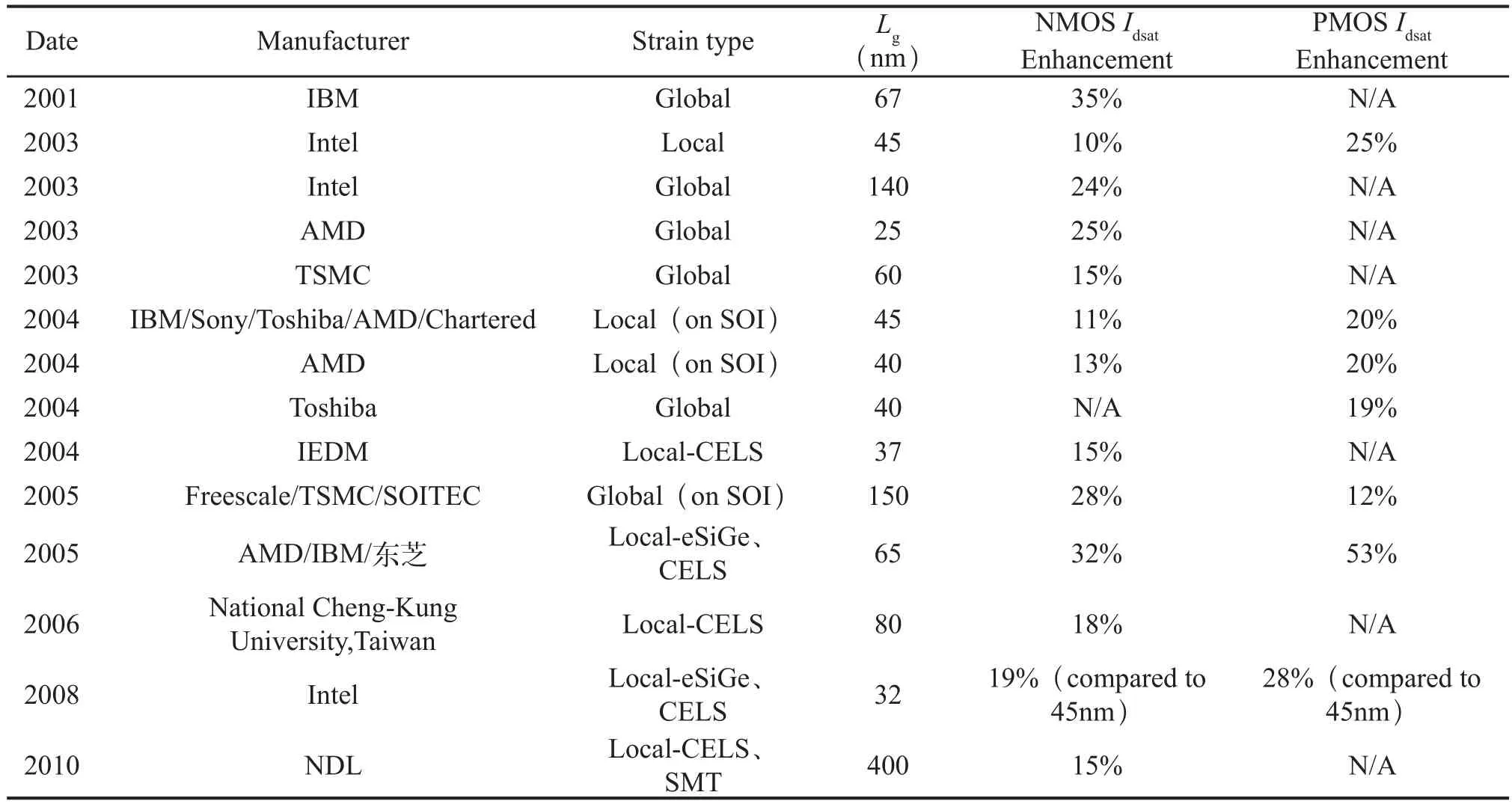

(2)局部应变,通过一定的技术仅在沟道处引入应力的方法。前者是虚拟衬底诱生双轴应变,即在MOS器件的沟道两个方向均存在应变;后者是在MOS器件的工艺制程中诱生的单轴应变。应变技术在MOS器件中的应用情况详见表1。

表1 全局应变与局部应变技术在MOSFET中的应用情况统计[18,24~30]

3.1 全局应变

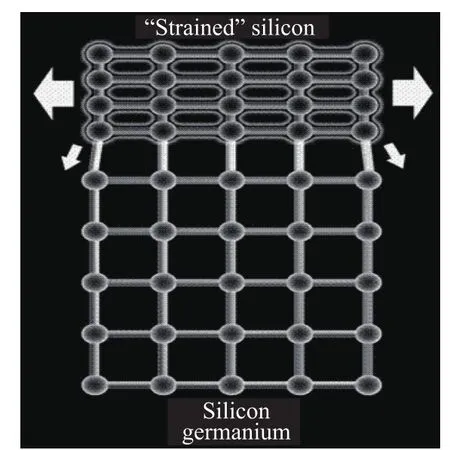

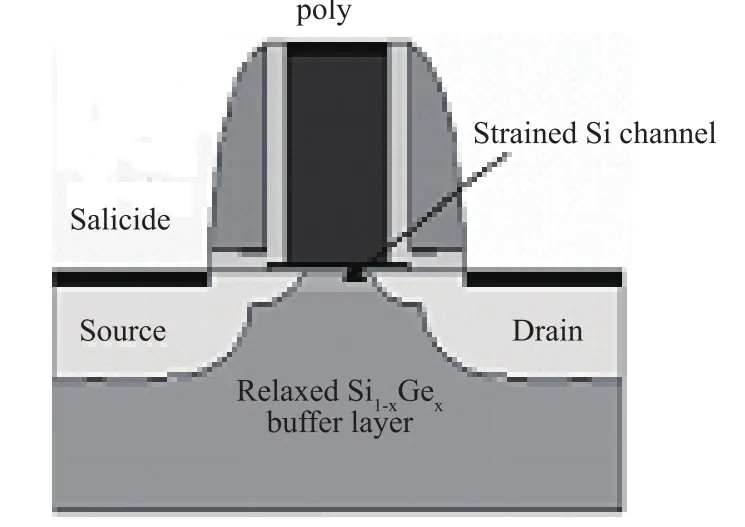

全局应变是利用材料晶格常数的差异产生的应变。Ge比Si的晶格常数大4.2%,当在Si/Ge弛豫层上外延一层硅时,硅的晶格将受四方畸变,在生长平面内诱生了双轴张应变,在垂直平面上诱生了压应变的薄单晶硅,如图6、图7所示。其外延层的厚度需要小于临界厚度,当外延层的厚度超过临界厚度时,应变所产生的能量将被消耗在与应变诱生层和衬底的匹配中,这时产生了大量的缺陷,尤其是位错会进一步降低应变的程度,从而使得载流子的迁移率降低。

应变弛豫缓冲层结构(Strained Relaxed Buffer,SRB)、绝缘层上的SiGe(SiGe On Insulator,SGOI)、绝缘层上应变硅(Strained Si On Insulator,SSOI)都属于全局应变。

3.1.1 应变弛豫缓冲层结构(SRB)

图6 应变Si/SiGe的形成

图7 在MOS器件沟道中应用示意图

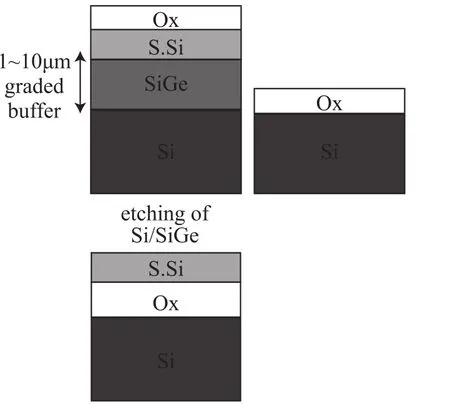

应变弛豫缓冲层结构是在硅衬底上按一定的方法生长应变弛豫的SiGe缓冲层,然后在上面生长硅帽层,Si/SiGe界面的晶格常数匹配时,硅原子受到拉伸,形成了双轴张应变。为了获得高质量的双轴应变硅,则需要优质的器件级的弛豫(relaxed layer)SiGe层作为虚拟衬底(Virtual substrate)。生长低RMS、低TD、高弛豫度(relaxation degree)、薄的弛豫层SiGe的方法主要有三种:渐变的Si1-yGey缓冲层技术(the grading SiGe buffer layer technique)、离子注入技术(ion implantation technology.)、低温硅技术(low temperature Si(LT-Si)technology)[5~15]。其中, 渐变的Si1-yGey缓冲层技术是最为常见的一种制备质量较高的SiGe虚拟衬底的方法,但外延层的厚度较厚,致使在MOS器件中的自加热效应较为突出[15,16]。离子注入技术可以获得高弛豫度、超薄的SiGe虚拟衬底,但因注入损伤引起SiGe层中的缺陷、位错密度、粗糙度较高,不易于制备质量高的弛豫层[16]。低温硅技术是制备高质量、超薄SiGe的虚拟衬底的选择,但应变的弛豫度(the degree of strain relaxation )受到膜层厚度的限制[15、17]。如果在应变硅层与弛豫层之间增加一层应变的缓变Si1-yGey缓冲层(其中,缓冲层中Ge的摩尔分数是梯度性变化的),以分担Si/SiGe异质结不匹配产生的应力,这个缓冲层也可以避免Si/SiGe界面的空穴限越问题[18]。

3.1.2 绝缘层上应变硅(SSOI)

将SOI技术与应变硅技术结合可以组合成多种复合结构,如SGOI、SSOI等。与体硅MOSFET相比,有如下的特点:

(1)应变硅的高迁移率和低掺杂浓度;

(2)低结电容;

(3)抑制短沟道效应;

(4)杂质浮动统计变化减小;

(5)与SOI器件相似的简单的绝缘和阱隔离。

其制备方法有:含Ge溶缩、融熔固化、晶圆键合与智能剥离等[21~23]。

全局应变硅技术存在的问题是SiGe衬底中Ge在热处理过程中外扩到应变硅层,同时,降低了应变度。而Ge到栅氧界面时,表面的缺陷浓度会大大增加,从而降低了MOS管的性能和可靠性。目前也有一种应变硅技术就是全晶片无Ge应变硅,S. Christiansen等采用键合技术制备了SSOI,如图8所示,首先在SiGe缓冲虚拟衬底上外延生长应变硅层,应变硅部分被热氧化,将另外一部分氧化层作为硅衬底,通过键合SiO2层,同时生长应变硅的SiGe缓冲虚拟衬底和初始Si衬底与应变硅玻璃,而中间的氧化层则成为绝缘硅的埋层[21,24]。

图8 采用Bonding技术制备SSOI示意图

3.2 局部应变

局部应变又称为工艺诱生应变,将部分工艺诱生的应变施加于MOS沟道处,提高MOS器件的性能。局部应变是单一方向的应变,即单轴应变。局部应变硅器件与MOS工艺相兼容,且工艺成本低、工艺简单。局部应变在MOS工艺中的应用主要有:源漏硅锗埋层[28]、应力帽层法[19]、浅槽隔离、金属硅化反应、应力记忆技术[18]等,其结构原理如图8所示。

3.2.1 源漏硅锗埋层(S/D Embeded SiGe-S/D eSiGe)技术

在硅衬底的S/D区域刻蚀凹槽,并在该区域外延SiGe层,利用SiGe与Si的晶格失配,提高硅的沟道区压应力,从而有助于提高空穴的迁移率,可以提升PMOS性能,但该工艺仅适用于短沟道器件。若在S/D区外延SiC层,因碳的晶格常数(0.356nm)远小于硅(0.5431nm),易对沟道区产生张应力,因此可以调节NMOS沟道区域的应力。C的原子含量在1%左右,70nm NMOS器件性能可以增加约35%[25,26]。

3.2.2 接触刻蚀停止层(Contact etch-stop liners-CESL)技术

接触刻蚀停止层技术是通过PECVD压应力的Si3N4和Thermal CVD张应力的Si3N4分别淀积在PMOS和NMOS的栅上调整沟道区域的应力。沟道应力的大小取决于Si3N4膜层的厚度。如应用较为广泛的DSL(Dual stress liner),2004年IBM[27]首次采用了DSL在45nm CMOS工艺技术,2.0Gpa张应力与2.5Gpa压应力Si3N4分别应用于NMOS与PMOS,诱导沟道产生应力1.0Gpa,使得NMOS、PMOS驱动电流分别提高了11%、20%。2008年Intel[30]在32nm MOS工艺中采用了高K金属栅极与第四代应变硅技术,NMOS与PMOS分别采用了2GPa的张应力与3.5GPa的压应力Si3N4膜淀积在栅上,同时,PMOS的S/D区域采用eSiGe(Ge%=30%)结构,沟道获得了1.2GPa~1.5GPa的应力,NMOS与PMOS的饱和驱动电流分别达到了1.55mA/μm、1.21mA/μm。

3.2.3 应力记忆技术(Stress Memoriation Technique-SMT)

SMT与CESL技术类似,但其中的栅、S/D区域上的帽层Si3N4是牺牲层,进行杂质退火后取出Si3N4,依靠残余应力(即应力记忆功能)提高器件的性能,该项技术主要应用于NMOS。

4 结论

总之, 应变硅具有迁移率高、能带结构可调的优点,且与传统的体硅工艺相兼容,已经被广泛地应用于90nm、65nm、45nm、32nm高速/高性能的集成电路工艺中。同时,应变硅技术与高K金属极栅工艺结合将是下一个技术节点(22nm、16nm)较佳的选择。因单一的应变硅技术提高载流子迁移率有限,载流子的速度已达饱和,采用单一的应变硅技术很难满足器件性能提升的要求。目前,将两种及两种以上的应变硅技术整合在CMOS工艺的过程中将是未来应变硅技术发展的一个重要方向,如CESL+S/D eSiGe、CESL+SMT+STI等。因此,应变硅是一种具有前景的新技术,必将成为高速、射频器件等首选的高迁移率材料。

[1]Rim K.Fabrication and Analysis of Deep Submicron Strained-Si N-MOSFET’s[J]. IEEE TRANSACTIONS ON ELECTRON DEVICES, 2000, 47(7)∶1406.

[2]Deepak K. N, et al. Low-f i eld hole mobility of strained Si on(100)Si1-xGexsubstrate[J]. Appl. Phys. Lett.,1994,64(19)∶2514.

[3]Muhammad N.,et al. A Design Evaluation of Strained Si-SiGe on Insulator(SSOI)Based Sub-50nm nMOSFETs[J]. JOURNAL OF SEMICONDUCTOR TECHNOLOGY AND SCIENCE, 2005, 5(2)∶136.

[4]Lee S. W.,et al. Growth of strained Si on high-quality relaxed Si1−xGexwith an intermediate Si1−yCylayer[J]. J.Vac. Sci. Technol. A, 2005, 23(4)∶1141.

[5]Xie Y H., et al. Fabrication of relaxed GeSi buffer layers on Si(100)with low threading dislocation density[J].Mater Sci Eng, 1992, 14(3)∶ 332.

[6]Liu J L., et al. A surfactant-mediated relaxed Si0.5Ge0.5graded layer with a very low threading dislocation density and smooth surface[J]. Appl Phys Lett, 1999, 75(11)∶1586.

[7]Buca D., et al. SiCion implantation for strain relaxation of pseudomorphic Si1-xG ex/Si(100)heterostructures[J]. J Appl Phys, 2009, 105(11)∶114905.

[8]Sawano K.,et al. Fabrication of high quality SiGe relaxed thin layers by ion implantation technique with Ar, Si and Ge ions[J]. Thin Solid Films, 2008, 517(1)∶ 87.

[9]Trinkaus H.,et al. Strain relaxation mechanism for hydrogen-implanted Si1-xG ex/Si(100)heterostructures[J]. Appl Phys Lett, 2000, 76(24)∶3552.

[10]Kasper E., et al. New virtual substrate concept for vertical MOS transistors[J]. Thin Solid Films, 1998, 336(1/2)∶ 319.

[11]Yang H, Fan Y. Effect of Si intermediate layer on high relaxed SiGe layer grown using low temperature Si buffer[J]. Chinese Journal of Semiconductors, 2006, 27∶144.

[12]Luo Y H.,et al. High-quality strain-relaxed SiGe fi lms grown with low temperature Si buffer[J]. J Appl Phys,2001, 89(12)∶ 8279.

[13]Chen H.,et al. Low-temperature buffer layer for growth of a low-dislocation-density SiGe layer on Si by molecular-beam epitaxy[J]. J Appl Phys, 1996, 79(2)∶1167.

[14]Linder K K.,et al. Reduction of dislocation density in mismatched SiGe/Si using a low-temperature Si buffer layer[J]. Appl Phys Lett, 1997, 70(24)∶ 3224.

[15]Yang H d.,et al.Growth of strained-Si material using low-temperature Si combined with ion implantation technology[J]. J. Semicond. 2010, 31(6)∶ 063001-4.

[16]Jenkins K A, Rim K. Measurement of the effect of selfheating in strained-silicon MOSFETs[J]. IEEE Electron Device Lett, 2002, 23(6)∶ 360.

[17]Peng C S., et al. Strain relaxation of GeSi alloy with low dislocation density grown on low-temperature Si buffers[J]. J Cryst Growth, 1999, 201∶ 530.

[18]Chih-Cheng L.,et al. Strained Silicon Technology∶Mobility Enhancement and Improved Short Channel Effect Performance by Stress Memorization Technique on nFET Devices[J]. Journal of The Electrochemical Society, 2010, 157(5)∶H497.

[19]Mohan V. D.,et al.Modeling Advanced FET Technology in a Compact Model[J]. IEEE TRANSACTIONS ON ELECTRON DEVICES, 2006, 53(9)∶1971.

[20]Tony A.,et al. Engineering strained silicon-looking back and into the future[J]. IEEE POTENTIALS, 2006,31.

[21]Taraschi G., et al. Strained Si, SiGe, and Ge oninsulator∶ review of wafer bonding fabrication techniques[J]. Solid-State Electronics,2004, 48∶1297.

[22]Lee et al. Strained Si, SiGe, and Ge channels for highmobility metal oxide semiconductor field-effect transistors[J]. J. Appl. Phys. 97, 2005, 011101∶1.

[23]Gamiz .,et al. Electron transport in strained Si inversion layers grown on SiGe-on-insulator substrates[J]. J. Appl.Phys., 2002 , 92(1)∶288.

[24]Christiansen S.H., et al. Strained silicon on insulator(SSOI)by waferbonding[J]. Materials Science in Semiconductor Processing, 2005,8∶197.

[25]Viktor S.. Strain induced effect in adwanced MOSFETs.2011,5.

[26]Maiti C.K., et al. Strained-si heterostructure fi eld effect devices[J]. Taylor & Francis,2007,295.

[27]Yang H.S., et al. Dual stress liner for high performance sub-45nm gate length SOI CMOS manufacturing[J].IEEE IEDM Tech. Dig., 2004,1075.

[28]Ghani T., et al. A 90nm high volume Manufacturing Logic Technology eaturing Novel 45nm Gate Length Strained Silicon CMOS Transistors[J]. IEEE IEDM Tech.Dig., 2003,978.

[29]Wang J. P., et al. Device Enhancement Using Process-Strained-Si for sub-100nm Nmosfet[J]. IEEE TRANSACTIONS ON ELECTRON DEVICES, 2006,53(5)∶1276.

[30]Packan P., et al. High performance 32nm logic technology featuring 2ndgeneration high-K+metal gate transisters[J]. IEEE IEDM ,2009.

The Application of Strained Silicon in the Nano CMOS Technics

LIU Guo-zhu1, YAO Fei1, WANG Shu-jie2, LIN Li1

(1.China Electronics Technology Group Corporation No.58Research Institute,Wuxi214035,China;2.Nantong Shipping College,Shipping and Ocean Engineering Depantmnet,Nantong226026,China)

Strained silicon technology, which provided with merits of high mobility, modif i able band-gap,compatible with conventional sub-silicon technics, was widely used in CMOS technics, and especially in the nano-meter node CMOS devices. In this text, the principle of carrier mobility ,which influenced by strain,was simply summarized, and the application of Global strain and Local strain in the nano CMOS technics was introduced. Meanwhile,multi-strain technics would become the trend of improvement of the nano CMOS devices’ performance in the future.

strained silicon; CMOS; global strain; local strain

TP702

A

1681-1070(2012)01-0031-06

2011-10-11

刘国柱(1980—),男,江苏盐城人,硕士研究生,工程师,现在中国电子科技集团公司第58研究所从事氧化扩散工艺研发工作,主要研究方向为电子材料及器件。