基于多处理器结构的多路话音编解码器设计

2012-07-31倪永婧

郭 巍,倪永婧

(1.中国电子科技集团公司第五十四研究所,河北石家庄050081;2.河北科技大学,河北石家庄050000)

0 引言

卫星通信的快速发展,使卫星通信业务的需求也不断增大。话音通信由于其自身的便捷性和通用性,在目前所设计的各种卫星通信系统中仍然占有很大的比重,是卫星通信应用系统的重要组成部分。但是,单路电话业务的卫星通信系统已经远远不能满足需求,现在的系统设计往往需要通话路数更多,压缩编解码效率更高,占用带宽更小的多路话音通信系统。通过采用多处理器结构,设计了一种多路话音编解码器,可以同时对多路话音呼叫进行处理,并且对话音信号进行高效压缩编码处理,满足卫通网络中多路话音通信的应用需求。

1 总体设计

在2 Mbps脉冲编码调制信号(PCM)中一共包含有32个时隙信号,每个时隙信号带宽为64 kbps,其中有30个时隙可以承载话音业务,每个时隙承载一路。多路话音编解码系统的主要功能是实现对2 Mbps PCM中多个时隙话音业务的呼叫控制,实现对64 kbps速率话音信号的压缩编解码处理,并完成数据的信道适配。

该系统通过帧定位信号和时钟信号可以对2 Mbps PCM中的各时隙信号进行定位,并实现对各个时隙PCM信号的插入和提取。PCM信号的带宽决定了该系统最多应可以实现30路话音业务的处理。此外,为了更好地适应卫通信道,有效利用卫通资源,需要对单路64 kbps的话音进行压缩编解码,系统采用8 kbps G.729编解码方式,该方式具有延时小、话音重建质量好等特性,非常适合卫通信道的传输特点。压缩后的话音数据经过信道适配,转换成同步数据发送至信道单元。

在系统的硬件设计方面,选用高级精简指令微处理器(ARM)理器作为主控处理器,负责完成话音通信系统中信令的解析以及话音呼叫控制;同时,DSP[1]处理器运算能力强,功耗低,并且可以提供视音频协处理器,所以选用DSP作为话音编解码处理器,实现对PCM数据的压缩编解码。利用高性能现场可编程门阵列(FPGA)芯片实现对系统的时序控制,完成PCM时隙的定位以及信道成解帧处理。多路话音编解码器组成框图如图1所示。

图1 多路话音编编解码器组成框图

在系统的软件设计方面,主控ARM处理器采用嵌入式LINUX操作系统,使用C语言进行程序软件设计;FPGA采用VHDL语言进行设计,在Xilinx开发环境ISE下进行编译;DSP处理器使用C语言编程,在CCS环境下进行编译。

2 功能组成

根据系统的总体设计,选用了多个处理器分别承担各个单元的工作,形成了多处理器结构的多路话音编解码器。根据系统的工作流程,该编解码器的工作主要包括以下几个部分:

呼叫控制:ARM处理器完成对话音信令的解析处理,并完成与卫通网信令的适配,实现对多路话音的呼叫控制;

PCM处理:通过FPGA芯片完成对PCM信号中各个时隙的定位,并能够实现各个时隙PCM信号的插入和提取,由FPGA实现;

话音编解码处理:提取后的PCM信号送至话音编解码DSP处理器进行编码处理;同时接收来自信道的同步数据,进行解码处理,把压缩后的话音信号再次恢复成PCM信号,并完成PCM信号的插入;

信道成解帧处理:将压缩后的编码数据进行并串转换,转换后的同步数据发送至同步接口,同时接收来自同步接口的同步数据,进行串并转换,发送至话音编解码单元。

此外,设计的多路话音编解码系统还具有以下2个功能:

①回波抵消处理:为了消除回声,多路话音编解码系统具有群路回波抵消功能,该功能通过专用芯片实现;

②监控单元:通过主控单元ARM处理器扩展的键盘接口和显示屏接口,实现对整个多路话音编解码系统的参数进行设置和查询,并实现终端参数的断电保存功能。

在系统处理的各个流程中,呼叫控制和话音压缩编解码是系统中最重要的2个部分,决定了一个系统能否稳定高效的运行。由于在该多路话音编解码系统中采用了多处理器处理形式,这样既发挥了ARM在控制方面的优势,同时又发挥了DSP在数字信号处理方面的优势。但是如何设计DSP和ARM处理器之间高速稳定的数据接口,成为了系统设计的关键。

3 关键技术

3.1 HPI接口特性分析

HPI[2]是TI公司为新一代高性能DSP上配置的与主机进行通信的片内外设。与直接存储器存取(DMA)方式不同,HPI的引脚全部为专用,它可以实现并行、高速的数据传送。

TMS320C6000系列DSP的HPI总线有32位数据总线HD[31:0],它是一个并行、双向和3态的数据总线,当数据总线不响应一个HPI读访问时,它被置于高阻态。HPI接口通过3个32位寄存器来完成外部主机和DSP之间的通信,它们是HPI数据寄存器HPID、HPI地址寄存器HPIA和HPI控制寄存器HPIC。HPID中存放的是外部主机从DSP存储空间中读取的数据,或者是外部主机向DSP存储空间中写入的数据;HPIA中存放的是外部主机访问DSP存储空间的地址;HPIC中存放的是外部主机对DSP的控制信息。其中,HRDY位是DSP输出给外部主机的准备就绪信号;HINT位是DSP向外部主机发出的中断请求;DSPINT位是外部主机向DSP发出的中断请求;HWOB是半字顺序。外部主机和DSP都可以访问HPIC,但只有外部主机可以访问HPIA和HPID。

此外,DSP的 HPI接口控制信号线还包括HCNTL、HHWIL、HR/W、HDS、HCS 及 HINT 等信号,通过这些信号线共同作用,实现对HPI接口的读写访问。

3.2 ARM与DSP间通信接口设计

在该多路话音编解码系统中,ARM处理器通过HPI接口,实现对DSP编解码后的话音数据的读写[3]。2个处理器之间的连接关系如图2所示。

图2 ARM处理器与DSP处理器连接关系

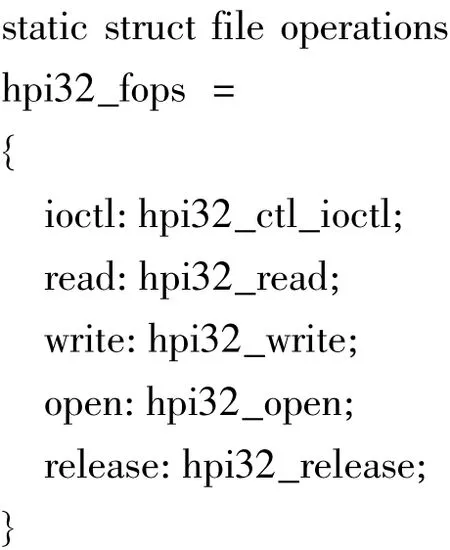

ARM处理器和DSP处理器之间的HPI接口驱动程序是数据传输设计的核心,ARM通过运行LINUX操作系统的HPI接口驱动程序完成对HPI接口的读写访问[4]。LINUX操作系统将C6000的HPI总线作为一个外部设备,虚拟成一种特殊的文件,称为设备文件,HPI驱动程序提供对这个设备的访问接口。这些接口定义在LINUX内核中,开发驱动程序就是要根据实际的硬件完成这些接口函数的功能[5]。驱动中的接口定义如下:

该结构体定义了驱动程序与用户的接口,运行于ARM上的用户应用程序可以利用这些接口实现对C6000的HPI总线读、写以及其他控制操作。

通过调用get_mapping_addr函数,(get_mapping_addr(0x0C000000,0x3000000)),可以实现地址映射,将这个物理地址向LINUX内核注册成可以直接访问的虚拟地址,并定义为VirtualAddr。

对HPI总线的读或写操作是由信号HR/W决定的,通过图2的连接对HPIA和HPID寄存器的访问可映射为对以下地址的访问:

根据系统设计需要,配置HCNTL1/HENTL0为0/1,实现当对HPID进行读写访问后,HPIA地址的自动加1。此时的HPIA地址为:

定义HPI接口的收发缓冲区位于DSP内主控可寻址的 DARAM内,字地址从0x40~0x83f共2 048个字,其中收发各1 024个字。从DSP往主控发的数据位于0x40~0x43f的缓冲区,从主控往DSP发的数据位于0x430~0x83f的缓冲区内。

话音通信过程中,当完成了信令交互之后,此时进入话音编解码通信状态,编码时,DSP定时产生中断,主控处理器ARM在收到中断之后需要在下一次中断来临之前,通过HPI接口把固定地址的数据读空;并将需要解码的数据写入对应的DSP处理器地址,最后清除中断信号,完成ARM与DSP的一次通信。

4 测试结果

多路话音编解码系统样机设计采用标准2U机箱,通过机箱内部的背板连接系统的各个单元。采用Intel公司的ARM处理器PXA270作为多路话音编解码系统的主控处理器;选用 TI公司的TMS320C6416[6]作为系统多路话音压缩编解码处理芯片;FPGA芯片采用XILINX公司的XC3S1000芯片,负责系统中的各种逻辑处理。

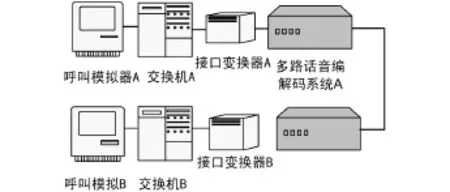

通过同步接口连接2台多路话音编解码系统,同时通过2台交换机连接呼叫模拟器,这样便组成了多路话音编解码测试系统。样机测试连接如图3所示。

图3 多路编解码系统测试框图

实际测试过程中,利用呼叫模拟装置,模拟同时发起多路电话业务呼叫,测试系统工作情况;测试结果表明,该多路话音编解码系统能够支持30路话音呼叫,并且可同时实现30路话音的G.729编解码,且话音质量清晰。

5 结束语

采用多处理器结构对系统进行设计,利用不同处理器的性能特点,高效地解决了多路话音编解码器实现过程中的各种问题;并通过HPI接口以及A/D接口,解决了不同处理器之间的数据交互问题,实现了强大的通信处理芯片与高性能数字信号处理芯片以及FPGA处理器的完美结合。此外,多路话音编解码器的实现极大地扩展了卫星通信系统中话音业务的应用。

[1]杨军,周启靖,晋宗俊,等.低端DSP芯片的语音处理算法研究[J].无线电通信技术,2011,37(1):45-46.

[2]刘乔,缪思恩.基于HPI的ARM与DSP双核通信实现[J].通信电子技术,2010(3):52 -53.

[3]刘乔,缪思恩.基于HPI的ARM与DSP双核通信实现[J].电子技术,2010(3):51 -52.

[4]李轶,张善从.基于HPI的双处理器通信接口设计[J].微计算机信息,2009,25(10):136 -138.

[5]董强,冷静,杨静.基于嵌入式双核通信HPI接口驱动的实现研究[J].科技资讯,2008(28):3 -4.

[6]张洪义,王金奎,刘永辉.实现 TMS320C6X1X HPI启动模式[J]. 无线电工程,2005,35(10):52-53.