用正交试验法优化挠性单面板精细线路的工艺

2012-07-30胡友作薛卫东黄雨薪

胡友作 薛卫东 何 为 黄雨薪

(电子科技大学微电子与固体电子学院,四川 成都 610054)

吕文驱 罗 旭 刘振华 李启军

(梅州博敏电子股份有限公司,广东 梅州 514000)

挠性印制电路板具备轻、薄、短、小、结构灵活的特点,可以同时进行静态和动态挠曲。其安装和连结的挠性特征、高密度电路的精确性、耐热性、电路终端选择的多样性以及材料和空间的有效使用等特性,使得挠性印制电路板得到了广泛的应用[1]。尤其是近几年迅速发展起来的COF封装技术[2],大大的推动了挠性印制板精细线路的制作。其中,挠性单面板是用途最多、用量最大的挠性印制版种类。

精细线路的制作是印制电路板制成能力的重要考量因素。面对竞争日益激烈的电路板行业和集成度不断提高的封装技术,精细线路的制作显得尤为重要。由于精细线路的制作受到材料和设备的很大限制[3][4],很有必要对其中各因素对线路精细度的影响进行探索。

本论文是在博敏电子股份有限公司公司原有的制成能力为70μm/70μm的设备基础上,对即将投入生产的挠性板的精细线路进行初步试验,拟用正交试验法制作理论线宽为40μm的线路时,曝光能量、显影速度和蚀刻速度等因素的影响及其优化参数。

1 实验仪器和材料

1.1 实验仪器

微蚀减铜线,自动干膜压合机,平行曝光机,DES线,线宽测量仪。

1.2 实验材料

旭化成干膜YQ-40SD,生益SF302单面有胶压延铜箔,聚酯菲林,蚀刻液,显影液,退膜液。

2 精细线路制作优化工艺

2.1 精细线路制作流程

原有的制成能力为70μm/70μm的设备的线路制作流程包括:开料、前处理、贴干膜、曝光、显影、蚀刻、退膜和IPQC工序。针对制作理论线宽为40μm的精细线路,我们采用了制作流程如图1。

图1 40μm/40μm精细线路工艺流程图

2.2 试验因素的选择

本实验选用基材是挠曲性能更好的压延铜箔,厚度为18μm。由于精细线路制作时,较薄的面铜可以减少线路的侧蚀和水沟效应,即不会出现有过多的蚀刻液聚集在比较精细的线路间而造成新旧蚀刻液互相转换等问题。为此,本实验采用减铜法先将铜箔厚度减至13μm。同时,经过了减铜后的铜面已经处于粗糙的状态,可以很好的与干膜结合,因此不用再对板面进行贴干膜前处理工序。对于干膜厚度,精细线路的制作选用分辨率较好的薄干膜较好。在精细线路的制作中,影响线间距的因素很多,比如铜箔厚度、铜箔类型、蚀刻压力、显影压力等。

由于曝光时,干膜中的感光剂会吸收相应波长的光波而发生交联聚合反应。对高密度、精细导线的成像,光源的特性会直接影响曝光的质量。曝光完毕的板在放置15分钟后进行显影,显影过程中未参加交联聚合反应的光致抗蚀剂会与显影液中的Na+作用,生成亲水性集团-COONa,从而被溶解下来。因此显影时得防止显影速度过慢而使露铜的两边膜受到显影液的腐蚀,造成导线变形失真。显影速度过快则会使显影液不能达到精细线路的线间,造成显影不净,产生大量的余胶。蚀刻工艺时是将未被抗蚀剂遮盖的铜用蚀刻液蚀刻掉,此次试验用的蚀刻液是H2SO4/H2O2。除了水池效应外,蚀刻速度精细线路制作的影响最大。所以本文重点考察对精细线路制作影响较大的曝光能量、显影速度和蚀刻速度三因素。

2.3 实验的参数水平

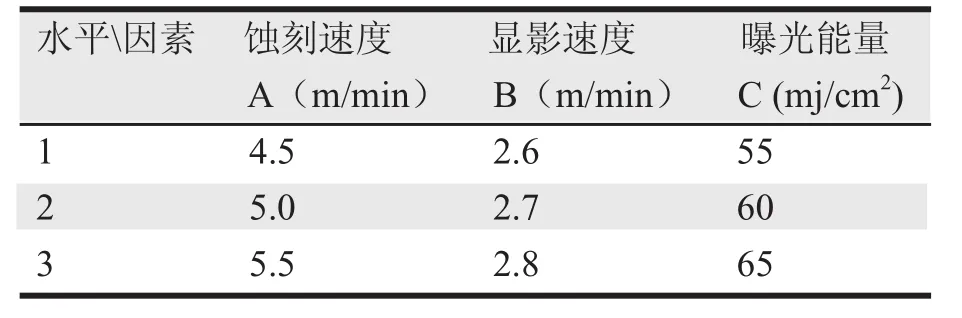

本文采用正交试验法[5]对影响线间距的因素——蚀刻速度、显影速度和曝光能量进行正交试验,每个因素选取三个水平,具体见表1。

表1 因素-水平表

3 试验结果与分析

3.1 试验步骤与安排

剪裁9张规格为150 mm×250 mm的的单面挠性板,从1号至9号分别编号,每个号对应表2中的试验号。用H2SO4/H2O2蚀刻液进行减铜,将铜箔厚度减至13μm。减铜后不再对板件进行贴膜前处理,直接用自动贴膜机进行贴膜。在保证曝光机真空度达到90%以上后,用聚酯菲林进行曝光。放置15分钟后调整相应的显影速度进行显影。显影后的板用线宽仪进行线路检测。然后进行蚀刻、退膜工艺,用线宽仪进行第二次线路检测,分析数据。

3.2 试验结果与分析

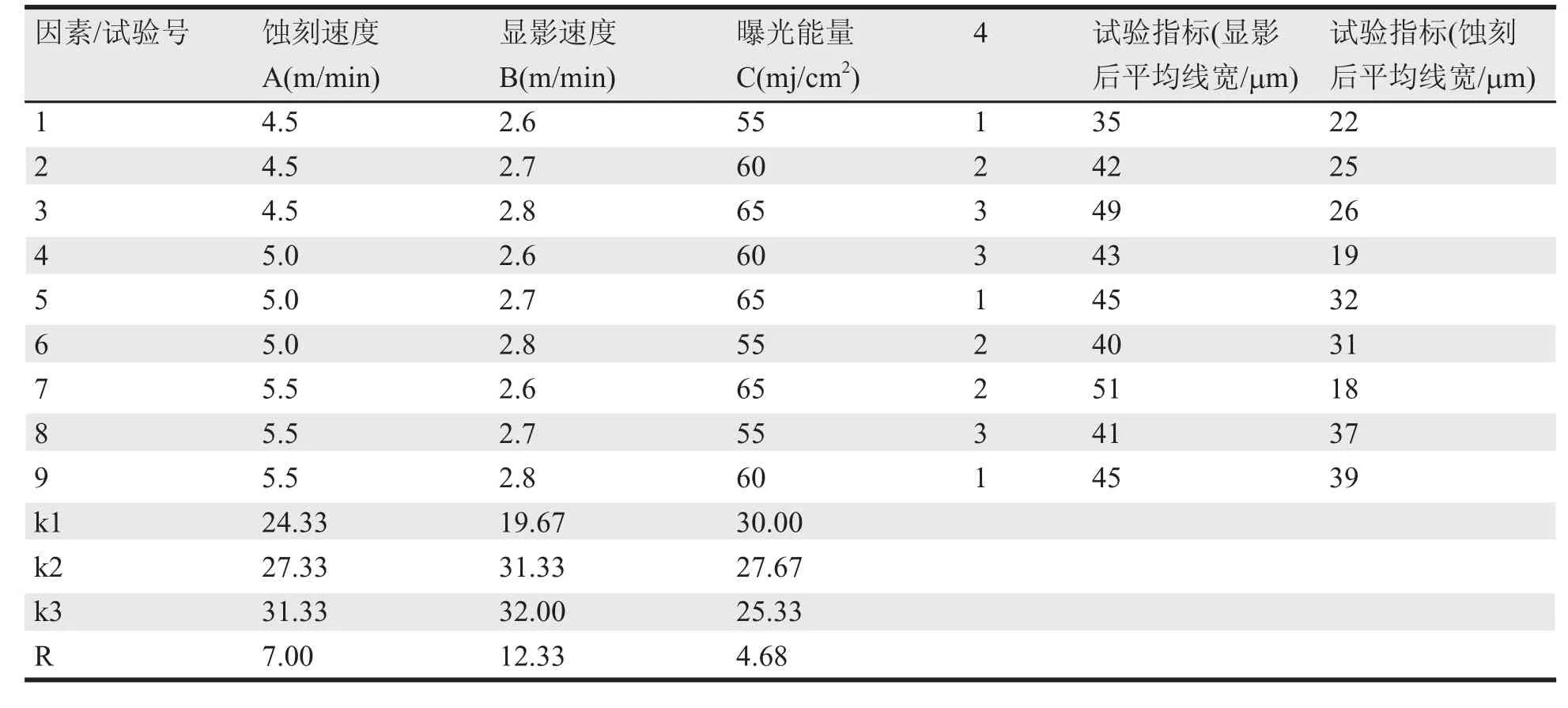

精细线路的制作中,每个因素都会对线路的最终成型起着一定的作用。其中显影后的线路质量能够很好的反应出曝光和显影工艺对线路的影响。试验在设定指标时选用了由两因素三水平进行全面试验得到的显影后线宽,独立对显影和曝光两个工艺进行研究。这样以来,正交试验不仅能够优化出适合精细线路的的指标、因素。还能进一步说明在不同阶段,不同因素、水平所起的作用。

由表2可知,试验6、8在显影后的线宽最接近理论值,但是线路都有不同程度的干膜起翘和显影不净的问题。9号试验线间距仍然在误差范围内,由图3可以直观的看到试验6、8和9号的两种试验指标下的线路形状。其中9号试验在显影后线路笔直,没有干膜起翘或者曝光过度而产生余胶等现象。而6号试验的线路边缘露的两边受到了显影液的攻击造成干膜起翘,从对应的蚀刻结果可知过度显影造成了干膜附着力的下降,容易造成过度蚀刻。9号试验在蚀刻后线间距达到理论值,线路形状良好,无严重侧蚀等问题。

表2 试验安排及其结果

试验结果由全面试验法得到的显影后线宽和正交试验法得到的蚀刻后线宽组成,其中只由曝光能量和显影速度组成的全面试验法较精确的得出在曝光能量为60 mj/cm2,显影速度为2.8 m/min时得到的线路最接近理论值,形状最好。

图2 6、8和9号试验的试验指标对比图

由蚀刻后线宽的试验指标的极差分析可知,各因素对精细线路的影响顺序是B>A>C。其指标-因素如图3所示。按照实际线宽与理论线宽的差值不大于20%的原则,线宽值在32μm ~ 48μm时为最佳值。由试验结果可得出最佳的试验组合是A1B3C2。即5.5 m/min的蚀刻速度、2.8 m/min的显影速度和60 mj/cm2的曝光能量。由试验可以发现显影速度对精细线路影响最大。在显影后线路较笔直,无余胶残留和干膜起翘的线路,在蚀刻后得到的线路线间距最接近理论值,并且线路无严重的侧蚀。相反在显影时已经有过显的线路在蚀刻后,即使选用较大的蚀刻速度也会出现果实可的现象,原因是过显影导致干膜附着力下降,在蚀刻过程中,蚀刻液很容易蚀刻到干膜覆盖着的线路。因此,在制备精细线路的过程中应当控制好显影的参数。

图3 精细线路试验指标-因素图

5 结论

本文通过在正交试验中安排全面试验的试验结果来进一步探讨了精细线路制作工艺的参数优化。通过9次试验得到了两个试验指标,由显影后的线宽得出,当曝光能量过大时会使得线路过度曝光,从而即使选用较小的显影速度也会有余胶停留在线间。曝光能量过小的话,因为光致抗蚀剂没有得到完全的反应,所以在显影速度很大时也会有有线路被冲掉。反之,在曝光能量适当时,显影速度过快或过慢都会引起线路的变形。由此可知,精细线路制作的每一步都该确保参数的正确。由蚀刻后的线宽可知,在曝光和显影都选用最佳的参数值时,用较快的蚀刻速度对精细线路的制作更有利一些。由正交试验得出试验的最佳工艺参数是A1B3C2,影响精细线路的主要因素是显影速度。

[1]Joseph Fjelstad, Flexible Circuit Technology[M]. BR Publishing, Inc, 2006.

[2]刘尊奇, 张胜涛. RTR(Roll to Roll)方式制作25μm/25μm COF精细线路的参数优化[J]. 印制电路信息,2009, NO9, p41~45.

[3]Fuhan liu,Venky Sundaram.Ultra-Fine photoresisit image formation for next generation high-density PWB substrate.International microelectronics and packaging society.2000,NO3, p339~345.

[4]何为. 优化试验设计法及其在化学中的应用[M]. 电子科技大学出版社, 2004.

[5]张怀武, 何为, 胡文成, 唐先忠. 现代印制电路原理与工艺[M]. 机械工业出版社, 2006.