三值绝热多米诺加法器开关级设计

2012-07-25汪鹏君杨乾坤郑雪松

汪鹏君 杨乾坤 郑雪松

(宁波大学电路与系统研究所 宁波 315211)

1 引言

当前数字电路系统主要采用二值逻辑实现,其单根信号线能传输的逻辑值只有0和1两种,电路的空间和时间利用率较低。采用多值逻辑可以大大减少电路输入变量数,提高每根连线携带的信息量,从而减小芯片的面积,增强数据处理能力[1-3]。多米诺电路由于其在电路面积和速度上的优势,广泛应用于各种高性能电路中[4,5],因此将多值逻辑与多米诺电路相结合,能够进一步减小电路面积,提高电路的信息密度,降低电路成本[6]。

加法运算是最基本的算术运算,理论上减法、乘法、除法、地址计算等都可以用加法实现[7]。因此,加法器既是数字系统的关键部件也是应用最为广泛的部件之一,加法器的功耗很大程度上决定着整个数字系统的功耗。然而,传统加法器由于电荷是从电源到地一次性的消耗掉,造成了极大的浪费;而采用交流脉冲电源的绝热加法器[8]能够充分回收电路节点中存储的电荷,有效降低电路的功耗。鉴于此,本文将多值逻辑、绝热逻辑与多米诺电路应用到加法器的设计中,以开关-信号理论为指导,提出一种新颖低功耗三值加法器设计方案。该方案首先利用开关-信号理论推导出一位三值绝热多米诺加法器开关级结构式;然后通过单元电路的级联得到四位三值绝热多米诺加法器;最后,经 Spice软件模拟证明,该方案逻辑功能正确,低功耗特性明显,且结构简单,与基于DTCTGAL电路设计的三值加法器[8]相比,每位加法器电路的晶体管数量减少约47%;与四位常规多米诺三值加法器相比,能耗节省约61%。

2 开关-信号理论

根据开关信号理论[9],在多值逻辑电路中引入开关变量与信号变量及与之对应的开关代数与信号代数,为多值电路的设计提供可靠的理论依据。

在开关代数中,开关变量α,β的取值T和F分别表示晶体管的导通和关断,有与(·)、或(+)、非(-)3种基本运算;在信号代数中,信号变量x,y的取值为0,1,…,m-1,用来表示多值电路的m种电压信号,有取小(∩)、取大(∪)及文字运算(ixi)等基本运算。

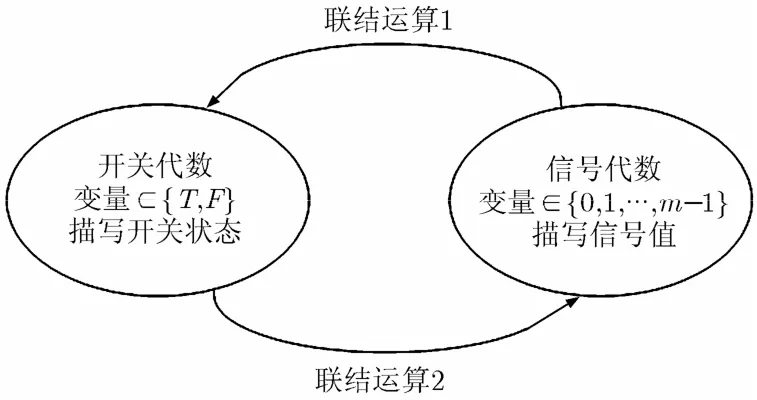

开关代数与信号代数并不是相互独立的,而是互有联系、相互作用的,它们之间的关系如图1所示,联结运算1用来描写信号控制元件开关状态的物理过程,联结运算2描写元件的开关状态控制信号的传输与形成的物理过程。

图1 开关-信号代数系统

其中,联结运算1主要有高阈比较运算和低阈比较运算。

高阈比较运算:

低阈比较运算:

根据式(1)与式(2)的定义,可证明阈比较运算在实际电路开关级设计中有如下性质:

联结运算2主要有传输运算和并运算:

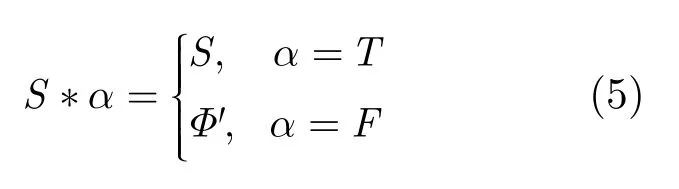

传输运算:

并运算:

式(5)中S为传输源,Φ'为高阻状态,*为传输运算;式(6)中传输运算“*”优先级高于并运算“#”,且为防止短路电流的出现,当S1≠S2时不允许α1和α2同时为T(导通)。

根据式(5)与式(6)的定义可知,传输运算与并运算有如下性质:

串联控制律:

并联控制律:

分配律:

通过上述关系式可知,CMOS电路中的电压开关可用于控制对输出电压信号的接地短路或接源短路,且可直接控制对输出电压信号的传输。

3 三值绝热多米诺加法器设计

3.1 一位三值绝热多米诺加法器设计

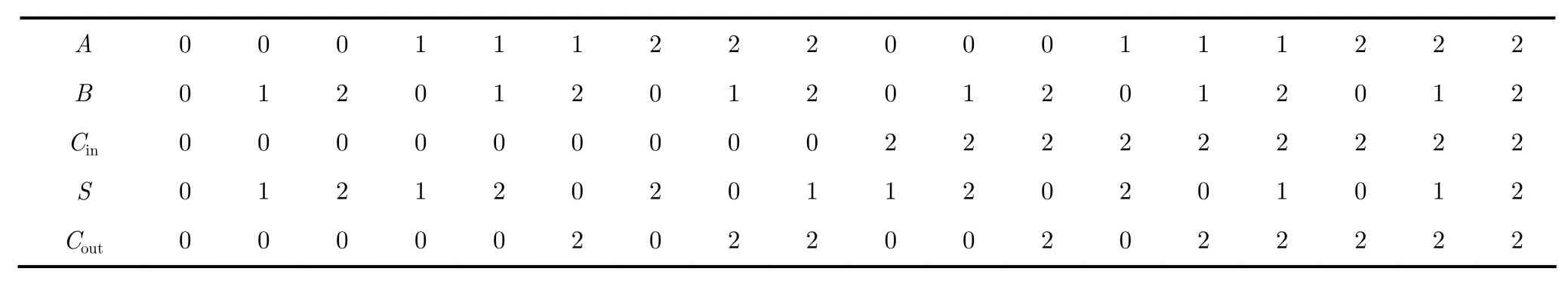

三值加法器真值表如表1所示,其中A为加数,B为被加数,Cin为来自低位的进位,S为本位和,Cout为进位。

同理可得本位和信号S的开关级结构式及电路,但与进位信号Cout不同,本位和信号S有0, 1,2三种逻辑值,因此需要不同的电路分别控制逻辑1信号和逻辑2信号的产生。令Y1,Y2分别是逻辑1信号和逻辑2信号的控制信号,则其开关级结构式如下:

表1 三值加法器真值表

图2 进位信号Cout产生电路

利用控制信号Y1,Y2可以控制逻辑1信号和逻辑2信号的产生,从而得到三值加法器的本位和信号S,本位和信号S产生电路开关级结构式如下:

由三值绝热多米诺文字运算电路、进位信号产生电路和本位和信号产生电路便可以构成一位三值绝热多米诺加法器,其电路结构图、电路符号及时钟波形如图6所示。图6(a)中电路符号为“L”的电路是三值绝热多米诺文字运算电路。

图3 控制信号Y1, Y2产生电路

图4 本位和信号S输出电路

图5 本位和信号S电路符号及时钟波形

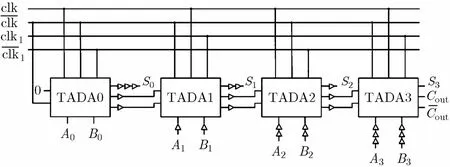

3.2 四位三值绝热多米诺加法器设计

图6 一位三值绝热多米诺加法器

图7 四位三值绝热多米诺加法器

4 计算机模拟

图8 四位三值绝热多米诺加法器模拟波形

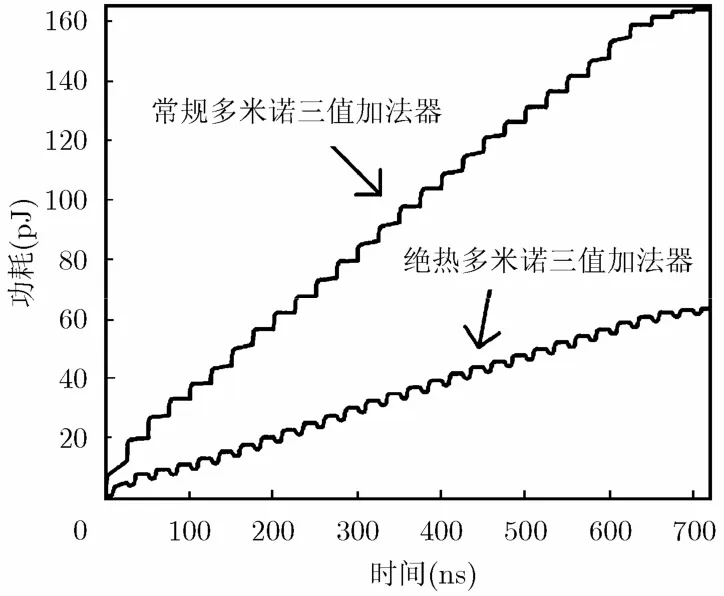

在相同参数下,将绝热多米诺三值加法器与采用直流电源的常规多米诺三值加法器进行瞬态能耗比较,如图9所示。图中绝热多米诺三值加法器瞬态能耗曲线的凹底表示能量被回收至功率时钟,从而有效地降低电路功耗。经分析,该绝热三值加法器功耗节省约61%,证明所设计电路低功耗特性明显。此外,该三值加法器由于采用了多米诺电路,因此具有结构简单的优点,与基于DTCTGAL电路设计的三值加法器[8]相比,每位加法器电路的晶体管数量减少约47%,降低了电路的成本。

图9 瞬态能耗比较图

5 结束语

本文利用开关-信号理论,提出一种新颖的低功耗三值加法器的开关级设计方案。该方案采用绝热多米诺电路进行设计,使用功率时钟供电,回收节点电容上的电荷,实现能量的重复利用,从而降低了电路的功耗,并且具有结构简单、成本低的优点。利用该三值加法器单元可以构成更多位数的三值加法器,推动三值数字系统的实用化进程。

[1]Keshavarzian P and Navi K. Universal ternary logic circuit design through carbon nanotube technology[J].International Journal of Nanotechnology, 2009, 6(10/11): 942-953.

[2]Lin Mi, Lu Wei-feng, and Sun Ling-ling. Design of ternary D flip-flop with pre-set and pre-reset functions based on resonant tunneling diode literal circuit[J].Journal of Zhejiang University-Science C, 2011, 12(6): 507-514.

[3]Moaiyeri MH, Doostaregan A, and Navi K. Design of energy-efficient and robust ternary circuits for nanotechnology[J].IET Circuits,Devices&Systems, 2011,5(4): 285-296.

[4]Kursun V and Liu Zhi-yu. Domino logic circuit techniques for suppressing subthreshold and gate oxide leakage[P]. US Patent: 7855578, 2010.

[5]汪金辉, 宫娜, 耿淑琴, 等. 45 nm 工艺pn混合下拉网络多米诺异或门设计[J]. 半导体学报, 2008, 29(12): 2443-2447.

Wang Jin-hui, Gong Na, Geng Shu-qin,et al.. Design of pn mixed pull-down network Domino XOR gate in 45 nm technology[J].Journal of Semiconductors, 2008, 29(12):2443-2447.

[6]李学初, 高清运, 陈浩琼, 等. CMOS集成时钟恢复电路设计[J]. 电子与信息学报, 2007, 29(6): 1496-1499.

Li Xue-chu, Gao Qing-yun, Chen Hao-qiong,et al.. The design of monolithic CMOS clock recovery circuit[J].Journal of Electronics&Information Technology, 2007, 29(6):1496-1499.

[7]Navi K, Maeen M, Foroutan V,et al.. A novel low-power full-adder cell for low voltage[J].Integration,the VLSI Journal, 2009, 42(4): 457-467.

[8]汪鹏君, 李昆鹏. 基于电路三要素理论的三值绝热加法器设计[J]. 电子学报, 2011, 39(5): 1037-1041.

Wang Peng-jun and Li Kun-peng. Design of ternary adiabatic adder based on theory of three essential circuit elements[J].Acta Electronica Sinica, 2011, 39(5): 1037-1041.

[9]杭国强, 陆慧娟. 新型电流型CMOS三值施密特电路设计[J].浙江大学学报(工学版), 2006, 40(7): 1141-1145.

Hang Guo-qiang, Lu Hui-juan. Novel current-mode CMOS ternary Schmitt trigger[J].Journal of Zhejiang University(Engineering Science), 2006, 40(7): 1141-1145.

[10]汪鹏君, 曾小旁. 具有预计算功能的新型绝热数值比较器设计[J]. 电子与信息学报, 2010, 32(1): 214-218.

Wang Peng-jun and Zeng Xiao-pang. Design of new adiabatic digital comparator with pre-computational function[J].Journal of Electronics&Information Technology, 2010, 32(1):214-218.

[11]杨乾坤, 汪鹏君, 郑雪松. 三值绝热多米诺文字运算电路开关级设计[J]. 电路与系统学报, 2012, 17(4): 36-40.

Yang Qian-kun, Wang Peng-jun, and Zheng Xue-song. Design of ternary adiabatic Domino literal operation circuit on switch-level[J].Journal of Circuits and Systems, 2012, 17(4):36-40.