CMOS模拟集成电路版图设计

2012-07-25解放,罗闯

解 放,罗 闯

(中国电子科技集团公司第四十七研究所,沈阳110032)

1 引言

现代CMOS工艺所实现的系统越来越复杂,工作速度越来越快,且工作电压越来越低。虽然缩小器件的尺寸节省了芯片面积,降低了功耗,提高了本征速度,但由此引入的不同模块间的串扰以及版图设计中的非理想性,严重限制了系统的工作速度和精度,所以版图设计是模拟电路设计的一个重要方面。

建立模拟电路版图单元,有两个原则:使芯片面积减至最小和将寄生器件对电路性能的影响降至最低。文中主要介绍模拟电路版图布局中叉指晶体管、对称性等,简要说明电阻、电容的版图实现,以及互连线的实现。

2 采用折叠方法的CMOS单元电路

在实际的MOS电路中有寄生电阻和电容。这类寄生参数主要由栅极形状决定。由于栅极的面积由电路设计所决定,因此建立版图单元不可能减小器件的栅电容,但是可通过调整器件的集合形状以减小另一些寄生电容,如:pn结电容。对于模拟集成电路,由于节点电容的大小对电路的动态性能有很大影响,因此采用并联晶体管结构后,MOS管在同样宽长比的情况下,由于采用了共用源漏区的结构,大大减小了源漏区的总面积,因此减小了节点电容,同时减小了MOS器件的源极和漏极的PN结电容,有利于改善电路的动态特性。

图1 折叠结构减小漏源pn结电容

根据经验,采用折叠栅极的MOS管,每一个指状晶体管宽度的选取要保证该晶体管的栅电阻小于其跨导的倒数。在低噪声应用中,栅的阻值应是1/gm的1/5到1/10。并联MOS管的个数也就是叉指个数,由器件的沟道宽度W和每个叉指所对应的小尺寸MOS管的沟道宽度决定。小尺寸MOS管的宽长比除了要考虑单个器件的性能优化外,还必须考虑全部并联器件所占用的面积以及版图平面布局的要求和工艺离散性的影响。

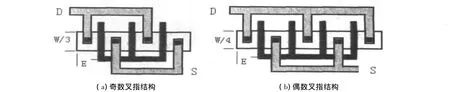

当采用叉指结构时,不同叉指数对电路的性能影响不同,下面以3叉指和4叉指器件结构为例说明奇偶数个叉指的异同点。如图2所示。

图2 叉指结构的MOS晶体管

奇数叉指的器件结构,源漏区个数相等面积相等,即具有相同的源极电容和漏极电容。对于偶数叉指的器件结构,源漏区个数是不相等的,两者之间相差一个有源区。所以源极与漏极的总面积不相同,则对应的电容也不相同,在版图设计时就必须考虑哪一极对电容比较敏感,进而减小相应极的面积,面积越小电容越小。

由以上分析可知,在设计叉指晶体管时,一般应尽可能采用奇数叉指。

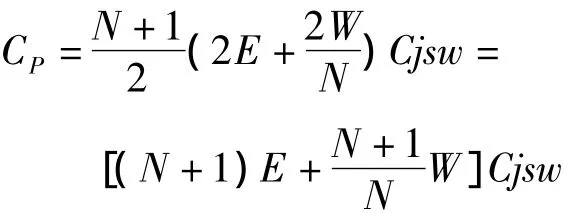

采用以上方法把一个晶体管分成了多个并联指状晶体管,虽然具有减小栅电阻的优点,但明显增大了源漏区的周边电容。对于奇数个折叠时(叉指数为N),源漏区周边电容:

E为漏区长度,W为宽度变量,Cjsw为单位长度侧壁电容。

由上式发现:若MOS管的W一定,要使源漏区周边分布电容Cp减小,就必须使 N、E远小于 W值。但实际中,有时这种原则会和降低栅噪声比等矛盾,需要根据实际应用采用相应的方法。

3 MOS管的误差和失配

由于所采用的工艺与材料特性和寄生效应等方面的原因,完全相同的器件在制作完成后电特性并不完全相同。因此,在个体器件和匹配器件的版图设计中必须充分考虑失配和误差的问题,通过版图设计避免或减小失配和误差。

以图3(a)中的差分对为例,图3(b)采用了不同方向的两个MOS管,容易由离子注入各项异性的几何失真造成失配。图3(d)所示的版图采用的是共源结构,当存在注入倾角产生的阴影时,一个位于漏区,一个位于源区,使两个MOS管失配。图3(c)则对称性较好。

图3 MOS差分对的电路图和版图布局形式

在实际版图中,通常也会用图3(d),在两边加上虚拟管,以增强对称性。如图4所示。

图4 增加虚拟管以提高对称性

在CMOS模拟电路中走线的方向也很重要,如图5(a)所示,M1旁有一条无关的金属线通过,这会降低对称性,引起M1和M2之间更大的失配,为了减小这种环境的影响,可在M2旁对称性的放置一条相同的金属线(甚至可以悬空),如图5(b)所示。

为了避免MOS管同方向的失配效应,如图6所示,可以采取交叉互补的原则,将每个MOS管拆成偶数个MOS管,然后交叉放置,实现“同心布局”。这样就可以实现M1和M2之间的匹配。但考虑到引线因素,布线会更复杂,布线对称性的难度也会更大,因此只有在高精度的运放输入端才会采用这种 形式。

图5 保持对称轴两边相同环境

图6 同心布局版图

4 电阻匹配与电容匹配

多晶电阻的匹配度是几何尺寸的函数。针对MOS器件版图设计的大多数规则也适用于电阻。长宽比例严格定义的电阻必须由相同的单位电阻通过串联或并联构成(具有相同走向)。采用比例电阻的结构进行设计时,电路的电特性主要与比例精度有关,而与单个电阻的绝对值精度呈弱函数关系。在版图设计上,这些比例电阻常采用矩阵连接结构,以减小比例误差。

对于精度高的电路,电容器的版图必须遵循以上针对晶体管和电阻所提出的原则。电容的误差主要来自面积误差和介质层厚度误差。所以与比例电阻类似,当每个小电容因工艺产生误差后,电容的比例仍能保持不变。

5 消除耦合的布线设计

信号线之间的电容可以形成耦合效应。以下两种情况会有电容形成:

(1)两信号线在不同层交叠,形成交叠电容。

(2)两信号线在同层平行临近,形成平行电容。

可以采用减小导体间交叠面积、并行长度的方法来减小交叠电容和平行电容;还可以在两平行导体之间加一个接地或固定电位的导体来屏蔽其间的串扰。

电源线上的电阻效应也会造成耦合,使电压不稳、形成噪声,可尽量缩短或加宽电源线以减小电阻。

6 结束语

以上对CMOS模拟电路版图设计中应注意的问题做出了简要介绍。在实际电路设计中仍有许多细节需要注意,包括建库、参数化设计等。设计人员根据具体情况综合考虑各种因素,以达到电路的优化。

[1] Dan Clein.CMOS IC LAYOUT concepts、methodologies and tools technical contributor[M].gregg schimokura,2000.

[2] 李玉山,来新泉.电子系统集成设计技术[M].北京:电子工业出版社,2002.

[3] 吴建辉.CMOS模拟集成电路分析与设计[M].北京:电子工业出版社,2004.