基于DMR标准的TPC信道编解码设计

2012-07-25权进国陈海飞林孝康

权进国,陈海飞,林孝康

(清华大学深圳研究生院现代通信实验室,深圳518055)

1 引言

DMR(Digital Private Radio)标准是欧洲电信标准协会在2006年颁布的数字对讲机标准。DMR标准采用了多种信道编码对不同的帧进行编码。在语音、数据和控制帧中,控制帧负责通话的建立、连接和终止,因而控制帧的信道编码显得尤为重要。控制帧的信道编码类型中一种很重要的编码就是Turbo乘积码。

目前市场上流通的DMR标准芯片大多由欧美公司把持,他们凭借自身的资本优势和技术优势,形成了大量的专利,正是这些技术专利壁垒大大抬高了芯片的成本。所以研发具有自主知识产权的价格低廉、性能优良的专用芯片对我国数字集群通信的发展有着重要意义。在分析DMR标准信道编码算法的基础上,设计了一种基于DMR标准的TPC信道编解码器,并且通过了仿真与验证。

2 TPC简介

1994年,Pyndiah等人[1]在 Chase算法的基础上提出了一种线性分组码的软输入软输出迭代译码算法,并将它应用于乘积码译码中,获得了很好的编码增益。其性能与Turbo卷积码较为相近。基于Chase算法的TPC迭代译码算法是一种通过缩小码字搜索范围的次最优译码算法。在译码时,将码元的对数似然比(Log-Likelihood Ratio,LLR)作为译码器的软输出,并将软输出信息减去软输入信息,作为下次迭代的外信息。通过这种方式不断修正码元的软信息,增大其可靠度,获得较好的译码性能。

以二维乘积码为例来讲述TPC的构成。设分组码:C1(n1,k1,d1)和 C2(n2,k2,d2)。其中 n 表示编码长度,k表示信息比特长度,d表示最小汉明距离。二维乘积码P=C1⊗C2的构造方式如图1所示。

图1 二维TPC的构造

3 编码器设计

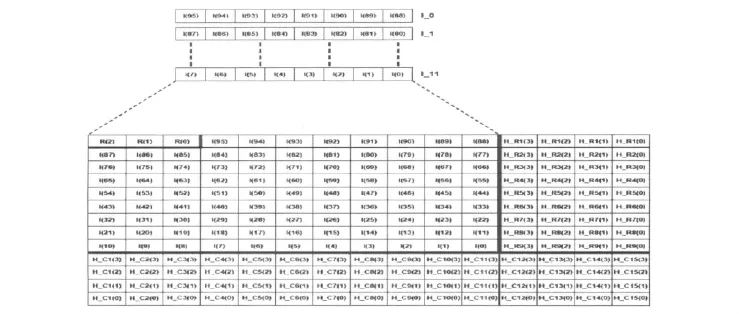

发送的序列首先经过一个交织器,打乱原始序列的顺序,这样可以有效抵抗信道上的瞬时干扰。经过交织的序列排成一个K=K9×11的信息矩阵,送入TPC编码器。DMR规定TPC编码器的行编码为C2=Hamming(15,11,3),列编码为 C1=Hamming(13,9,3)。生成的编码矩阵为 N=N13×15。编码矩阵如图2所示。

图2 TPC(196,96)

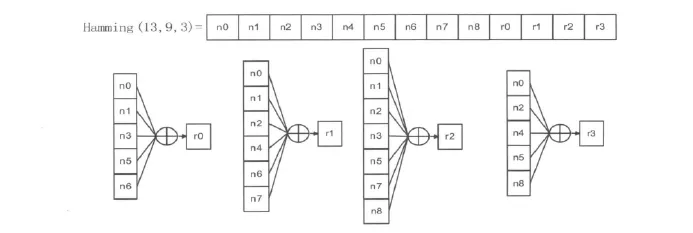

3.1 Hamming(13,9,3)与 Hamming(15,11,3)编码器的设计

DMR信道编码器的核心模块是汉明码编码器的设计,DMR 规定行编码 C1=Hamming(15,11,3),列编码 C2=Hamming(13,9,3)。生成多项式:G(x)=x4+x+1=238。根据生成矩阵设计汉明码编码器,以 Hamming(13,9,3)为例,编码器的实现框图如图3所示。

图3 Hamming(13,9,3)编码

3.2 编码器整体结构

发送的序列首先经过一个交织器,打乱原始序列的顺序,这样可以有效抵抗信道上的瞬时干扰。经过交织的序列排成一个K9*13的信息矩阵,送入TPC编码器。DMR规定TPC编码器的行编码为Hamming(15,11,3)方案,列编码为 Hamming(13,9,3)方案。行编码和列编码是顺序执行的,先后关系不影响最终的编码输出。图4中TPC编码矩阵右下角为校验的校验,可以证明校验的校验与行/列编码的顺序没有关系。在编码器的最后执行串转并操作,将编码矩阵中的数据转化为比特序列送入调制器。编码器的整体结构如图4所示。

图4 编码器整体结构

4 译码器的设计

译码器执行的是与编码器相反的过程,为了降低译码器的误码率,采用软译码方案。从解调器接收到的软信息序列,按照发送时的并转串顺序恢复TPC编码矩阵 R13×15。TPC软译码采用经典的Chase-Pyndiah迭代译码方案。经过TPC软译码输出的信息码字再经过解交织得到原始的信息序列。译码整体结构如图5所示。

图5 译码器结构

Turbo乘积码是一种串行级联码,所以采用软判决迭代译码能提升Turbo乘积码的性能。最常用的就是Chase译码迭代算法。Chase算法是一种软输入硬输出的译码算法,其输出为硬判决信息,1998年Pyndiah[2]针对Turbo乘积码提出一种基于修正的Chase译码算法的迭代译码算法。迭代译码结构由行、列译码器串行级联而成,结构如图6所示。

图6 SISO迭代译码器

每一次迭代译码输入外信息W[m],经过软译码单元计算输出外信息W[m+1]。如图2所示,在单元译码器中α[m]表示第m次迭代时的加权因子,β[m]表示第m次迭代时的可靠度因子。它们的值都是通过经验获得,在迭代初始阶段信噪比较大时,α[m]一般取值较小,主要由于抑制了外信息W[m]的作用。在迭代后期,信噪比较小时,其值可以逐渐增大。β[m]主要用于控制软输出信息输出峰值范围。

迭代译码器中行/列译码器单元为汉明码译码器。汉明译码器首先将软信息r做硬判决得到H,根据H的译码信息在码字空间找到一组备选码字C,在码字C中找到距离软信息r最近的码字作为译码输出D。并用D与备选码字C的距离来计算外信息W[m],作为下一次迭代译码的输入。

5 结束语

提出基于DMR标准的Turbo乘积码编解码器整体方案,整个信道编解码是用Verilog HDL实现的,利用Modelsim SE 6.0进行仿真,综合工具使用Xilinx ISE 10.1软件,FPGA平台选用Xilinx Spartan 3 XC3S1500[3]。为了验证模块功能的正确性,将测试序列同时送给硬件模块和Matlab程序仿真,结果两者输出一致,说明模块功能正确。

根据DMR标准信道编码算法的原理设计了基于FPGA的信道编解码系统,系统用Verilog HDL实现并通过了FPGA的综合验证。最后验证结果表明该系统在占用较少硬件资源的同时,设计的结果符合DMR标准要求,能够应用到整个DMR标准的SoC实现中。该设计对DMR标准的ASIC芯片的研发也具有一定的指导意义。

[1] PYNDIAH R,GLAVIEUX A,PICARTA,et al.Near optimum de-coding of product codes[C].IEEE GLOBECOM.NewYork:IEEE,1994.

[2] Pyndiah R.Near-Optimum Decoding of Product Codes:Block Turbo Codes[J].IEEE Trans.on Communications,1998,48(8):1003-1010.

[3] 曹志刚,钱亚生.现代通信原理[M].北京:清华大学出版社,2001.

[4] 王新梅,肖国镇.纠错码-原理与方法[M].西安:西安电子科技大学出版社,1991.

[5] 张忠培,史治平,王传丹.现代编码理论与应用[M].北京:国防工业出版社,2007.

[6] Chase D.A Class of Algorithms for Decoding Block Codes with Channel Measurement Information[J].IEEE Trans.Inform.Theory,1972,18(1):170-182.

[7] Hirst Simon A,Honary Bahram,Markarian Garik.Fast Chase Algorithm with an Application in Turbo Decoding[J].IEEE Trans.on Communications,2001,49(10):1693-1699.