一种并行异步FIFO控制算法设计

2012-07-25刘凤伟

刘凤伟

(昆明船舶设备试验研究中心,昆明650051)

1 引言

在电子设计系统中,常常需要对各种数据进行接收、存储和发送。例如在数据采集系统中,需要通过高速AD、微处理器和一些接口电路实现数据的采集[1]。但是由于不同电路/系统之间的工作时钟速度不同,通常会给数据的传输带来困难,而利用FIFO电路实现不同时钟域数据的接收、存储和发送具有接口简单、读写方便的优点,使用异步FIFO是有效解决在两个不同时钟系统之间快速而方便地传输实时数据的方法[2]。在此提出了一种FIFO控制算法,具有工作速度高、可靠性好、设计简单灵活的优点,具有广泛的应用前景。

2 FIFO控制算法

FIFO控制算法,即是一种先入先出的存储器控制算法,其使用一个双端口存储器存放数据,数据发送方在一端写入数据,接收方在另一端读出数据,良好的FIFO控制算法能够非常好的协调两个时钟域的读/写工作,满足高时钟频率的要求。在FIFO设计中,有软件FIFO和硬件FIFO,常用的硬件FIFO由专用的ASIC芯片组成,提供外部接口,可以很方便的实现数据控制,例如IDT公司的7200系列异步双口FIFO存储器[3]。根据FIFO的工作时钟,可将FIFO分为同步FIFO和异步FIFO,同步FIFO是指读/写时钟是同一个时钟,在时钟沿来临时同时对存储器进行读/写操作,异步FIFO是指读/写时钟不是同一个时钟,而是相互独立的,在时钟沿来临时分别对存储器进行读/写操作[4]。

FIFO控制算法包括两部分:写FIFO算法和读FIFO算法。以下将详细分别介绍这两种算法。为了更好地理解这两种算法,首先定义与这两种算法相关的控制参数,其中包括:Flag:标志位;CW Enable:写使能;CREnable:读使能;CWNum:当前能够读取数据的个数;CRNum:当前能够写入数据的个数;CurWNum:当前写指针相对于首地址的位置;CurRNum:当前读指针相对于首地址的位置;WFull:写存储器满标志;REmpty:读存储器空标志;Len:存储器深度;DAT[Len]:定义的存储器空间。

在对FIFO操作前,需要首先初始化系统。包括初始化FIFO的控制参数和存储器。初始化FIFO的控制参数:Flag=0;CWEnable=1;CREnable=1;CWNum=0;CRNum=0;CurWNum=0;CurRNum=0;WFull=0;REmpty=0;初始化存储器:存储器深度:Len;存储器的存储空间:DAT[Len]。

2.1 写FIFO控制算法

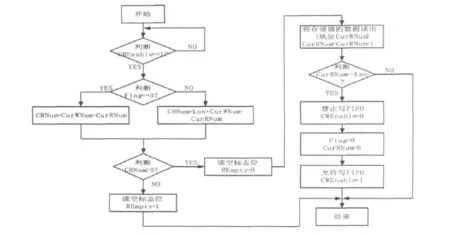

写FIFO的控制算法:如图1所示,首先,判断写使能CWEnable是否等于1,等于1说明此时可以进行写操作,不等于1,则说明此时不能进行写操作,则退出。然后根据标志位Flag的状态,计算出此时可以写入数据的总个数CWNum;然后判断CWNum是否大于0。如果不大于0,则说明此时存储器不能写入数据,此时置WFull为1,表示存储器已经写满,然后结束写FIFO操作,如果大于0,则说明此时存储器可以写入数据;紧接着把数据写入地址为CurWNum的存储器中;其次判断CurWNum是否等于Len,如果不等于Len则说明还没有写到存储器的顶端,然后结束写FIFO操作,如果等于Len则说明此时已经写到了存储器的顶端,此时需要禁止标志位CREnable使其等于0(禁止读FIFO操作),然后改写标志位Flag为1和CurWNum为0,紧接着释放读标志位CREnable等于1;最后结束写FIFO操作。

图1 写FIFO的流程图

2.2 读FIFO控制算法

读FIFO的控制算法流程:如图2所示,首先判断读使能CREnable是否等于1,等于1说明此时可以进行读操作,不等于1则说明此时不能进行读操作,则退出。然后根据标志位Flag的状态,计算出此时可以读出数据的总个数CRNum;然后判断CRNum是否大于0,如果不大于0,则说明此时不能从存储器读取数据,此时置REmpty为1,表示存储器已经读空,然后结束读FIFO操作。如果大于0,则说明此时可以从存储器读取数据;紧接着从地址为CurRNum的存储器中读取数据;其次判断CurRNum是否等于Len,如果不等于Len,则说明还没有读到存储器的顶端,然后结束读FIFO操作,如果等于Len,则说明此时已经读取到了存储器的顶端,此时需要禁止写标志位CWEnable使其等于0(禁止写FIFO操作),然后改写标志位Flag为0和CurRNum为0,紧接着释放写标志位CWEnable等于1,最后结束读FIFO操作。

3 测试系统设计与结果分析

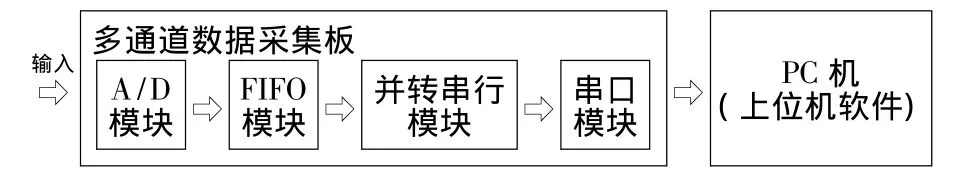

在第二节中,分别详细介绍了写FIFO的控制算法和读FIFO的控制算法。为了验证该控制算法的系统性能和指标,根据系统需求,搭建了硬件测试平台,硬件包括:多通道数据采集板、PC机、USBRS232转接器、示波器和万用表;系统软件:Microsoft Visual C++6.0开发的专用上位机软件,测试系统框图如图3所示。

图2 读FIFO的流程图

图3 测试系统原理框图

测试结果表明,运用该FIFO控制算法的多通道数据采集板性能稳定可靠。该FIFO控制算法设计结构简单、性能稳定可靠,适用于多种FIFO运用场合,对更高性能的数据采集系统设计具有非常重要的意义。

[1] 高礼忠.FIFO在高速数据采集系统中应用[J].电子测量技术,2005(1):51.

[2] 魏欣,王勇.一种高效的异步FIFO设计方法[J].仪器仪表用户,2009,16(1):102.

[3] 戴志涛.PCI总线双向FIFO缓冲并行通信的实现[J].微处理机,2002,(3):53-55,64..

[4] 李辉,王晖.基于VHDL的异步FIFO设计[J].现代电子技术,2011,34(14):154.