基于FPGA的步进电动机加减速控制器

2012-07-23杜启亮田联房

张 滨,杜启亮,田联房

(华南理工大学,广东广州510641)

0引 言

步进电动机由于具有运动精确、易于控制、起停快、连续运行无累积误差和能够接收数字信号等特点,被广泛应用于数控机床、自动化仪表、机器人等控制系统中。其中,步进电动机常用于快速精确定位系统中,但在启动和停止的过程中,若步进脉冲变化太快,转子会由于惯性过大产生起停失步和起停冲击大等问题,因此对步进电动机起停阶段的加速度进行规划,产生合理的步进电动机驱动频率以减少冲击具有很强的实际意义。

目前国内外关于步进电动机加减速控制的算法主要有三种[1]:(1)梯形曲线算法。(2)指数曲线算法。(3)抛物线算法。三种算法各有各自的特点,适合不同的应用场合。利用FPGA设计控制器不仅可以简化设计过程,而且可以降低整个系统的成本和体积,提高系统的可靠性。本文针对二相双四拍步进电动机,按照模块化的设计思想,设计了系统各模块,为了便于抛物线算法的硬件实现,本文将此算法做了适当的修改,并在单片Altera飓风一代FPGA中完成了各模块的设计与布局布线,完成了控制系统的整体调试,实现了步进电动机的加减速控制系统的设计。

1加速度控制算法分析

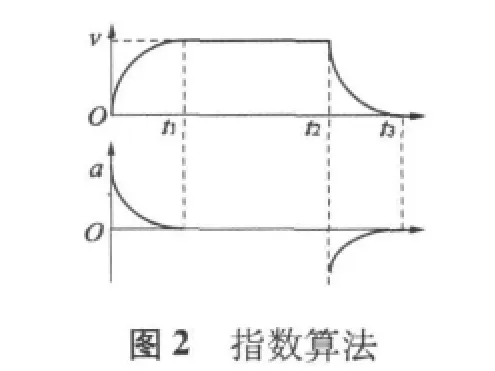

应用于步进电动机的加速度控制算法是以速度曲线的形状命名的,主要的控制算法包括梯形算法、指数算法和抛物线算法。梯形算法包括加速度正恒定阶段、加速度零阶段和加速度负恒定阶段。此方法计算简单,节省资源,但是三个阶段不能光滑过渡,这会对电机的运行质量和机械结构造成不利的影响。如图1所示。指数算法的加速度表现为指数特征。此算法适合系统的固有规律,适合对加减速要求较高的场合。如图2所示。

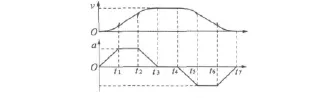

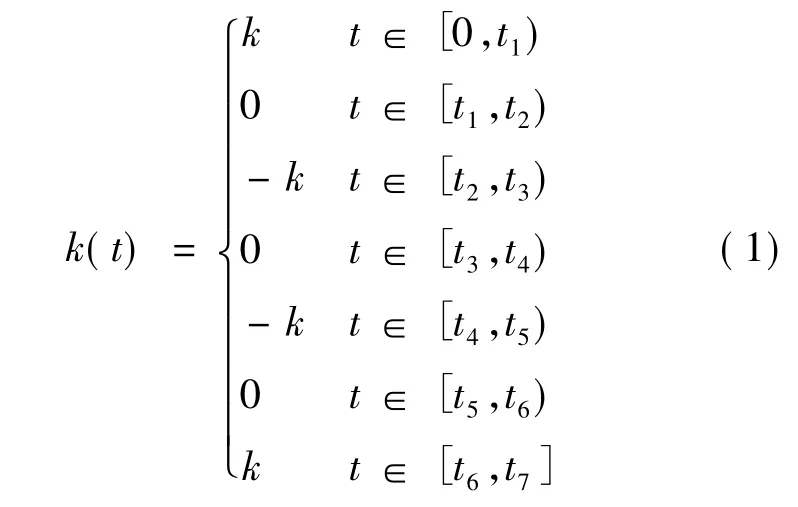

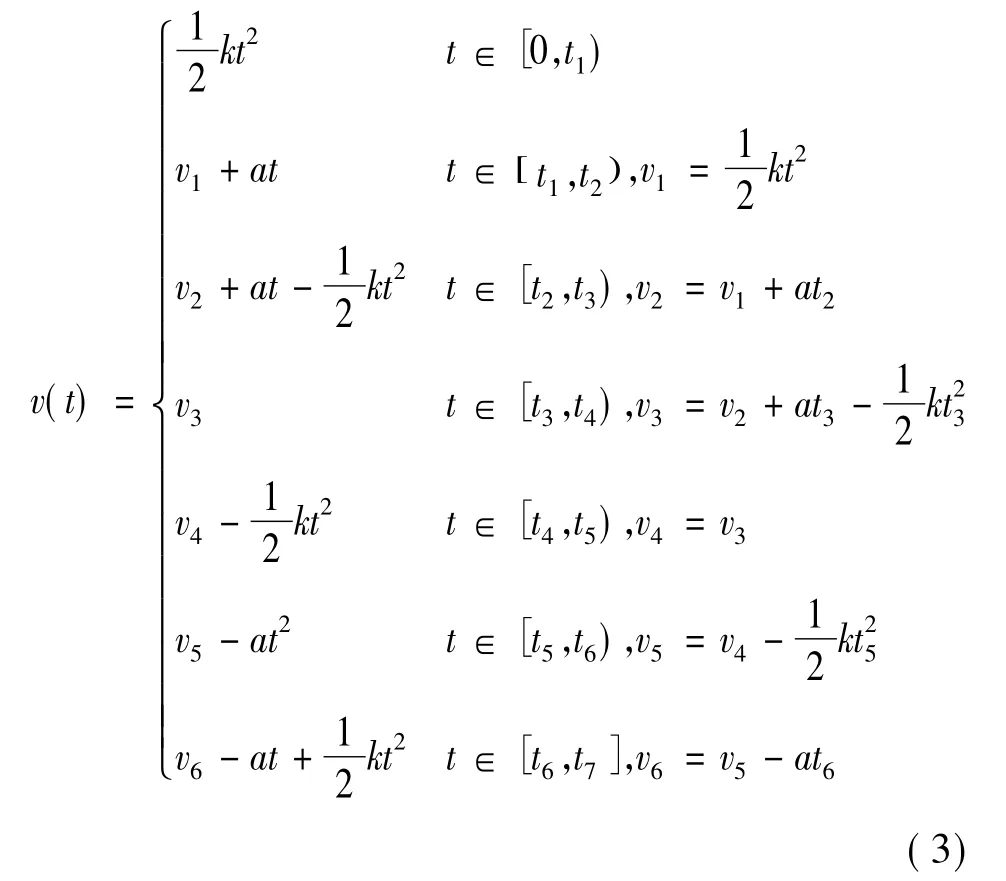

抛物线算法包括加加速运动阶段、加速运动阶段、减加速运动阶段、匀速运动阶段、加减速运动阶段、减速运动阶段和减减速运动阶段[2]。如图3所示。由此可以看出加速度能够平稳地过渡,能够平稳地实现加速和减速。

图3 抛物线算法

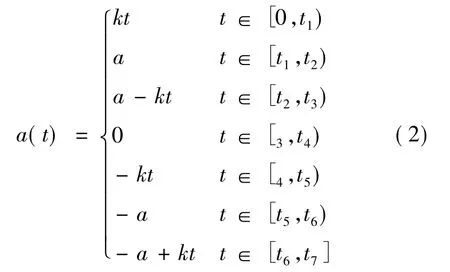

此算法的变加速度随时间的变化规律如下:

加速度相对时间的变化规律:

对加速度进行积分,即可得到相应的速度相对时间的变化规律:

再对速度进行积分,即可得到位移相对时间的变化规律。作为加减速控制系统,接收的是步进电动机最终的位移,输出的是步进电动机驱动芯片的逻辑脉冲,也就是位移随时间的变化规律。但是不同位移要完全都转换成上述七个加减速阶段,必须要经过复杂的数学运算和逻辑推理,此部分如果在FPGA中实现,需要的代价是非常大的。

因此,本文假设[0,t3]和[t4,t7]是固定步进数的调整阶段,大多数情况下步进电动机都要经过这两个阶段的调整,只是匀速阶段的步进数不同而已(即图3中的时间段[t3,t4]不同)。但对于总步进数小于调整阶段步进数的情况,则需省去中间的某些运行阶段,由此可得以下四种情况:(1)无匀速运行阶段,即去掉图3的[t3,t4]时间段,如图4(a)所示;(2)无匀速运行阶段,仅运行部分减加速运动阶段和部分加减速运动阶段,即去掉全部的[t3,t4]时间段,部分[t2,t3]时间段和部分[t4,t5]时间段,如图4(b)所示;(3)无匀速运行阶段,无减加速运行阶段和加减速运行阶段,即省去全部的[t2,t3]、[t3,t4]和[t5,t6]时间段,如图 4(c)所示;(4)仅有加加速运行阶段和减减速运行阶段,如图4(d)所示。

图4 其他调整曲线

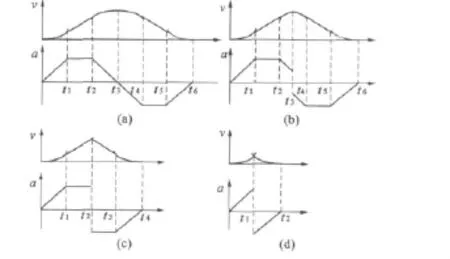

2 FPGA运动控制系统结构

整体控制结构包括SPI通讯模块、步进计数模块、地址产生模块、ROM模块、脉冲计数模块和步进逻辑发生模块。SPI通讯模块解析通讯协议以完成通讯数据的传送。步进计数模块对步进电动机的步进数实时统计。数据存储模块存储步进电动机每个步进所需要的时间间隔。脉冲计数模块则具体对系统频率进行计数,计数结束后产生信号以驱动步进逻辑发生模块。步进逻辑发生模块产生步进电动机驱动芯片所需要的驱动逻辑。各部分之间的关系如图6所示。

图5 整体控制框图

2.1 SPI通讯模块

此模块解析SPI通讯协议,控制单元在spi_cs为低电平时,在spi_clk的上升沿对spi_data信号进行采样,采集过程中将数据放入临时寄存器,结束之后再将数据存入指定的寄存器中。此模块设计两个寄存器的目的是存取前后两次步进电动机的目标位移,这样此系统接收的是步进电动机的最终位移而不是相对位移。此控制系统设计的寄存器位宽为16位,即可以存取0~65 535之间的数据,能够满足一般系统的要求。控制框图如图6所示。

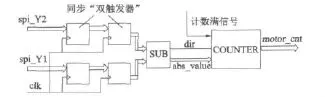

2.2步进计数模块

此模块接收SPI通讯模块发送的数据,根据接收到的数据计算出要行走的步进数。因为在加减速的过程中,步进间隔是不同的,所以此模块需要脉冲计数模块的计数满信号作为反馈信号。另外值得注意的是SPI通讯模块和步进计数模块属于不同时钟域,为了避免亚稳态产生,此处采用双跳技术[3]来解决此问题。此模块框图如图7所示。

图7 步进计数模块框图

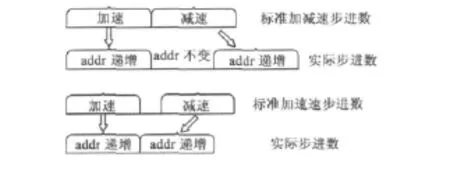

2.3地址产生模块

此模块要根据步进绝对值和当前步进电动机的计数值产生ROM地址。如果实际的步进数大于加减速调整阶段的步进数,则会存在加速度为零、速度不变的时刻,那么在此阶段每一步的步进间隔是相同的,ROM中的数据也是相同的,所以在ADDR就不会发生变化。如果实际的步进数小于加减速调整阶段的步进数,则根据大小省去中间的运行阶段,由此可得addr的变化符合以下规律。

图8 addr变化规律

2.4 ROM 模块

此模块存储的是每一步的时间间隔,对应的是时间对位移的关系。此处我们设定标准的七段抛物线的时间段是相同的,加速与减速阶段是对称的,则ROM存储的时间间隔也是对称的,因此此处只需要计算其中一段即可。根据式(3),积分可得到时间对位移的关系,由于步进电动机的每一步都是相同的,所以我们需要根据上述关系得到相同位移下的时间间隔。首先假设步进电动机的步进距离为Δs,则从零开始依次计算出每个步进距离所需要的时间Δt1,Δt2,…,Δtn,再根据相邻两个 ROM 中的数据是对应成比例的,即:

同时,ROM中的数据对应着步进时间,即:

这样如果我们已知匀速时每个步进所需要的时间ΔTn和系统频率 f,由式(5)可得 Xn,再根据式(4)和 Δt1,Δt2,…,Δtn,即可得到 X1,X2,…,Xn-1。

2.5脉冲计数模块

此模块根据对ROM发送的数据进行计数,如果计数结束,则表示步进电动机需要行进一步,同时发出计数满信号以指示其他模块。

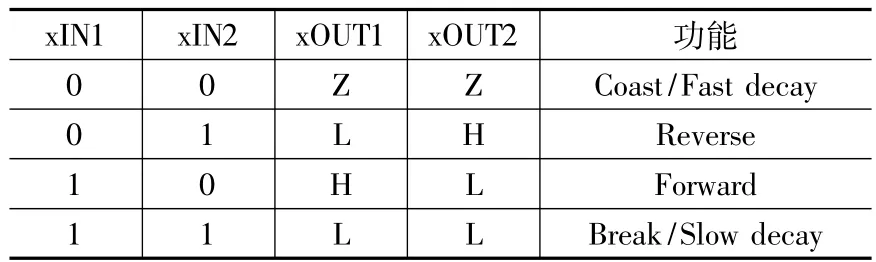

2.6步进电动机逻辑发生模块

本文电机的控制方式为二相双四拍。步进电动机的两相绕组为:A(+)、B(-)、C(+)、D(-),AB为一相,CD为一相。驱动方式为AC-BC-BDAD。选择 TI的步进电动机驱动芯片DRV8833[4],此芯片包括两个H桥,每个H桥控制一相,如果AB相连接第一个桥,CD桥连接第二个桥,且每个H桥输入与输出之间的对应关系如表1所示。则可以得到H桥的输入(AIN1 AIN2 BIN1 BIN2)为:1010、0110、0101、1001。另外当电机处于空闲状态时,设置输入为1111,使电机处于刹车状态。

表1 H桥逻辑表

所以步进电动机逻辑发生模块在电机正转时,输出为1010-0110-0101-1001-1010-…;电机反转时,输出为1010-1001-0101-0110-1010-…。空闲时输出1111。

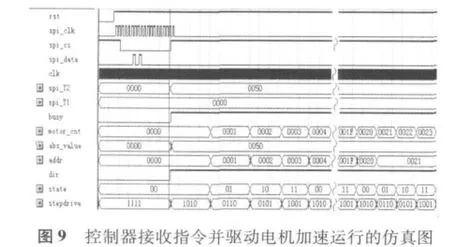

3 FPGA仿真及实验结果

由仿真图可以看出,系统复位之后,FPGA通过SPI通讯模块接收到十六进制数据0X50,并且存储在spi_Y2寄存器中。接收结束之后,步进计数模块中的motor_cnt寄存器开始对步进电动机进行计数,地址产生模块根据motor_cnt和abs_value产生相应的地址,此地址连接 ROM,最后脉冲计数模块对ROM发送的数据进行计数,计数结束之后产生计数满信号,最后驱动步进逻辑发生模块及其他模块。从stepdrive可以看出,系统空闲时产生1111,系统工作时产生1010-0110-0101-1001-1010-…。同时每一步的时间间隔是由脉冲计数模块对ROM中的数据计数得到的,从大变小变化,表明步进电动机的速度在变快。

经过若干步之后,addr的数据不再发生变化,这属于前面提到的地址产生模块的第一种情况,即步进电动机进入匀速运行阶段。

最后步进电动机在接近步进终点时,步进时间间隔逐渐变大,即步进电动机速度逐渐变小,最后停止。第一次运行结束之后,FPGA通过SPI通讯接口重新接收到新的数据0X40,并且存储在spi_Y2寄存器中,同时将以前的数据存储在spi_Y1寄存器中。由于系统采用的是绝对计数方式,所以在接收结束之后,abs_value变为0X10,dir信号变为低电平,表示方向为负,同时stepdrive产生1010-1001-0101-0110-1010-…。

经过若干步之后,addr的数据由0X0008突变为0X0038,这属于前面提到的地址产生模块的第二种情况,即步进数较小,运行过程中无中间调整阶段。

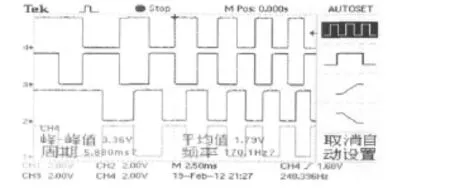

图11为示波器测量结果,由图可以看出FPGA依次输出1111-1010-0110-0101-1001-1010-…,表示驱动逻辑为电机正转,并且周期递减,表示电机正处于加速运行阶段。

图11 示波器测量结果

4结 语

基于FPGA的步进电动机控制系统能够实现标准的抛物线加减速算法和修改后的加减速算法。实现了对步进电动机起动和停止阶段的加减速控制,有效避免了步进电动机由于惯性产生的起停失步和起停冲击大等问题,大大提高了步进电动机的运行性能。

[1] 王玉琳,王强.步进电机的速度调节方法[J].电机与控制应用,2006,33(1):53-64.

[2] 王勇,王伟,杨文涛.步进电机升降速曲线控制系统设计及其应用[J].控制工程,2008,15(5):576-579.

[3] Steve Kilts.高级FPGA设计:结构、实现和优化[M].北京:机械工业出版社,2009.68-70.