载人航天器大功率智能配电单元电磁兼容性设计

2012-07-11周新顺王宇鹏

周新顺,王 力,王宇鹏

(北京卫星制造厂,北京 100190)

0 引言

大功率智能配电单元(以下简称配电单元)是载人航天器能源系统的核心单机产品,将一次电源输出的电能进行汇流和电压变换后,为卫星平台及载荷设备提供稳定、可靠的电能,功率高达2.2 kW。配电单元采取标准化、模块化和通用化的设计思想,主要由配电模块、DC/DC变换模块和数据采集与通信模块组成。配电模块实现整器负载配电的加断电时序控制;DC/DC变换模块将一次母线电压转化为负载所需的二次母线电压;数据采集与通信模块完成各种状态自动采集、处理与通信。各功能模块协调工作,最终实现整器负载用电的统一配置管理和控制。配电单元内部包括一次母线(100 V高压)和二次母线(28 V低压)2种母线,模拟电路和数字电路共存,电磁环境恶劣。解决好配电单元电磁自兼容以及与外界兼容问题,满足型号电磁兼容性要求是配电单元的设计难点。

1 配电单元电磁兼容性要求

载人航天器研制工作根据不同分系统或设备所处的环境、不同设备的特点,制定了电磁兼容性设计规范,明确了电磁兼容性要求。航天器各个设备均应满足相应的电磁兼容性指标,以确保整器在各个阶段和各种工作模式下均能稳定可靠工作[1]。

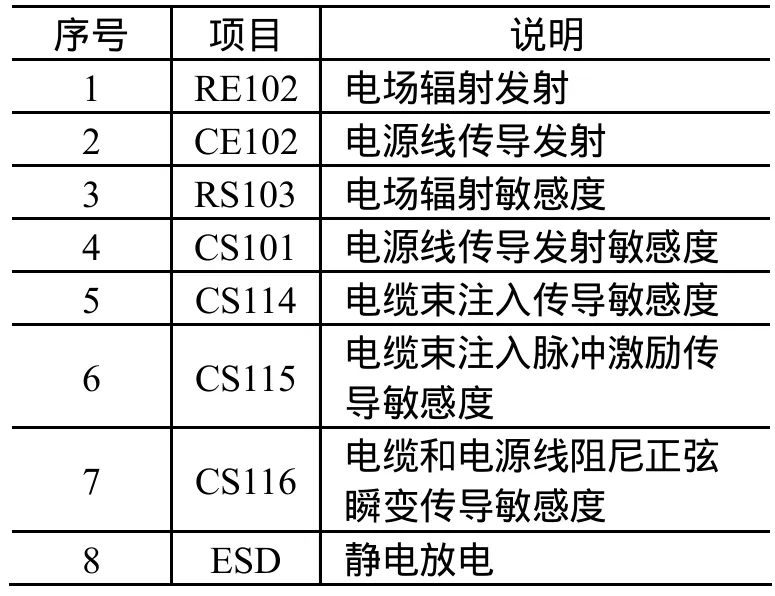

电磁兼容性要求主要包括干扰发射和敏感度2大类,其中又包含若干子项目。配电单元需要满足的电磁兼容性指标有8个,具体见表1。其中CE102和 RE102为干扰发射项目,规定了对外干扰的最大限值;其他为敏感度项目,规定了需要具备的承受外界干扰的最低能力。配电单元具有高电压、大功率的特点,因此电磁干扰发射为其电磁兼容性设计的重点。本文主要论述配电单元采取的抑制干扰发射的相关技术和措施。

表1 电磁兼容测试项目Table 1 Electromagnetic compatibility testing items

2 配电单元电磁兼容性设计

电磁兼容性设计的基本方法是指标分配和功能分块设计。即将电磁兼容性指标要求分解为整机级、模块级、电路级和元器件级,按照各级要实现的功能要求和电磁兼容性指标要求,逐级进行设计,并采取一定的防护措施。在对配电单元的配电模块、DC/DC变换模块和数据采集与通信模块分别进行电磁兼容性设计后,再进行整机级的电磁兼容优化。

2.1 配电模块电磁兼容性设计

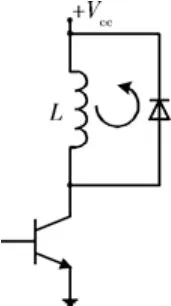

配电模块中包含有继电器、表贴电阻和电容等元器件,稳态工作(继电器不动作)时不存在电磁干扰源。但在继电器开通和关断的瞬间,由于继电器中线圈的感应特性,在线圈两端会产生较大的反电动势电压尖峰,包含了大量的高频频谱成分,从而成为电磁干扰源[2]。

抑制继电器线圈激励信号所产生的反电动势通常有2种方式:一是在继电器线圈两端并联二极管,抑制反电动势的效果好,但是线圈能量衰减的速度慢;二是在继电器线圈两端并联二极管串联电阻,与第一种方式相比,抑制反电动势的效果稍差(抑制效果取决于电阻阻值),但绕组能量衰减的速度快。通常情况下,对于单稳态的电磁继电器,应采用第二种方式,以缩短继电器的响应时间;对于双稳态的磁保持继电器,绕组能量衰减的速度对继电器的响应时间没有影响,可以选用第一种方式。由于配电模块中的继电器均为磁保持继电器,所以本文采用第一种方式对继电器产生的瞬态干扰进行抑制。

当继电器触点动作时,线圈电流会在线圈和二极管形成的环路中流动。为了减小电流环路的辐射发射,应尽量减小继电器线圈与并联二极管形成的环路面积,如图1所示。

图1 继电器动作时形成的电流环路Fig. 1 The current loop of relay switching

2.2 DC/DC变换模块电磁兼容性设计

2.2.1 电磁干扰分析

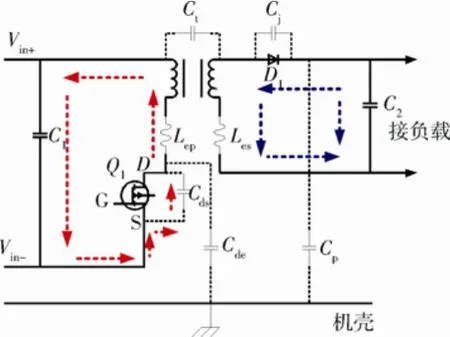

DC/DC变换模块由多个DC/DC变换器组成。鉴于DC/DC变换器中半导体器件周期性通断的开关工作方式,DC/DC变换器属于重要的电磁干扰源。同时,配电单元中有多个DC/DC变换器的并联工作,存在发射干扰叠加的机理。

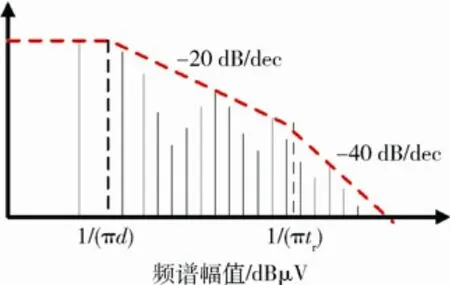

DC/DC变换器的电磁干扰主要是由功率半导体器件开关动作导致的电压和电流变化率(dV/dt和dI/dt)所产生[3]。图2为DC/DC变换器的高频等效模型。由图 2可以看出,MOSFET开关管、整流二极管以及变压器存在寄生电容和电感。正是这些非理想的寄生效应,为传导干扰提供了路径。DC/DC变换器中传导干扰主要有2类:一是功率半导体开关器件动作的开关谐波分量,其频谱如图3所示;二是寄生效应产生的高频振荡导致高频干扰。高频振荡产生的干扰电流如图2中虚线箭头所示。干扰电流按其传导路径的不同,可分为差模电流和共模电流2种。线间的干扰电流为差模干扰电流,线地之间的干扰电流为共模干扰电流,可分别采用差模滤波和共模滤波措施进行抑制。

图2 DC/DC变换器的高频等效模型Fig. 2 High-frequency equivalent model of DC/DC converter

图3 开关频率频谱图Fig. 3 Switching frequency spectrum

2.2.2 吸收电路设计

吸收电路能够降低电路中开关管和整流器件的电压或电流变化率,以抑制干扰源的电磁干扰强度,其基本原理就是开关管关断时为其提供旁路,吸收积蓄在寄生分布参数中的能量,从而抑制干扰的强度[4]。

DC/DC变换器中吸收电路由电容和电阻串联构成,再与整流二极管并联。电容作为二极管关断时存储在二极管结电容中电荷的放电电路,平滑二极管电流和电压波形,进而减少高频分量。另外,尽量缩短吸收电路中的器件引线,并使吸收电路尽量靠近整流二极管,可有效减小整流二极管和吸收电路形成的环路面积,以降低辐射发射。

2.2.3 滤波设计

DC/DC变换器同时存在差模干扰电流和共模干扰电流。差模干扰取决于DC/DC变换器的固有工作模式,主要存在于1 MHz以下频段;共模干扰主要存在于1 MHz以上频段。功率开关管和整流二极管相对于机壳的寄生电容(图2中Cde和Cp)与其两端电压快速变化(即大的 dV/dt)的共同作用,会产生通过机壳以开关频率为基频的共模噪声电流。

DC/DC变换器滤波设计是抑制电磁传导发射干扰的重要方法。DC/DC变换器滤波电路由差模滤波电路和共模滤波电路组成,分别对差模干扰电流和共模干扰电流进行抑制。滤波措施不仅能够减小DC/DC变换器的电源线传导发射(CE102),同时还会改善其传导敏感度(CS101)、辐射发射(RE102)、电缆束注入传导敏感度和静电放电等电磁兼容性能[5]。

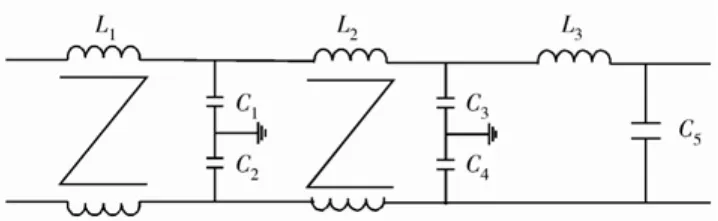

由于配电单元中DC/DC变换器的电压较高、功率较大,共设计了两级共模滤波和一级差模滤波电路,如图4所示。L1和L2为共模滤波电感,C1~C4为共模滤波电容;L3为差模滤波电感,C5为差模滤波电容。在确定了DC/DC变换器的相关性能指标、开关频率和占空比等参数后,通过计算和仿真,可确定滤波电感和电容的具体数值。

图4 DC/DC变换器滤波电路Fig. 4 Filter circuit of DC/DC converter

2.3 数据采集与通信模块电磁兼容性设计

数据采集与通信模块主要为数字电路。对于数字器件的脉冲波形,上升时间决定了其高频分量的多少,上升时间越短,高频分量频带越宽[6]。这些高频谐波分量会通过印刷电路板(PCB)上印制线条的天线效应向外辐射噪声。同时,电压波形固有的电压变化率通过寄生电容的共同作用,产生共模传导发射干扰。相对于DC/DC变换模块,数据采集与通信模块的干扰要小很多。

2.3.1 元器件合理选用

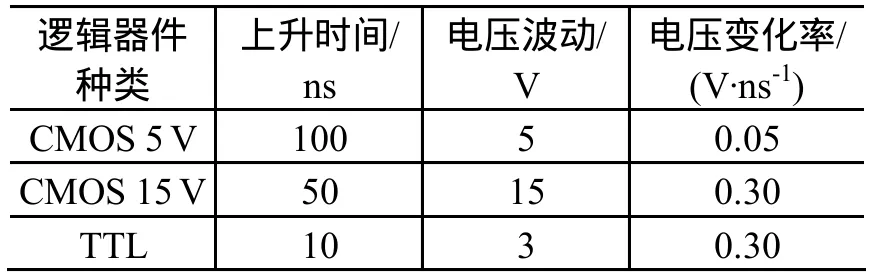

在满足功能要求的前提下,数据采集与通信模块尽量选用上升时间长的器件,其中关键元器件为数字电路集成芯片。表2列出了各类数字电路器件的上升时间和电压变化率等性能参数。

表2 不同数字器件的上升时间和电压变化率Table 2 Rising time and voltage regulation of differentdigital devices

由表2可以看出,CMOS 5 V逻辑器件的上升时间最长、电压变化率最小。数据采集与通信模块的最高工作频率不超过1 MHz,信号周期大于1 μs,而CMOS 5 V逻辑器件的上升时间为100 ns,既能满足电路性能要求,又能最大限度地限制高频谐波分量,因此大部分逻辑器件选用CMOS 5 V系列。

2.3.2 PCB设计

通过采取以下措施进行 PCB设计[7],可以改善配电单元各模块以及整机的电磁兼容性。

1)分隔低电平模拟电路和数字电路,最大限度降低数字部分与模拟部分之间的相互干扰。

2)模拟电路与数字电路分区布设。模拟电路部分主要包括 A/D转换器、模拟开关、运算放大器和基准电压源等;数字电路部分主要包括单片机及其外围电路、存储器和看门狗电路等。

3)将高速组件布设在距离接插件最近的区域,低速组件布设在远离接插件的区域,以减小线路阻抗和高速信号的环路面积。

4)按照走线长度最短且使环路面积最小的原则进行PCB布局,以将辐射发射和辐射敏感程度降至最低。缩短线路长度还能降低天线效应,抑制PCB对外发射或接收电磁干扰。

5)在靠近芯片的电源管脚处使用去耦电容消除瞬态过程对电路的影响。

6)分别布设专用回线或分配多个回线,减小回线阻抗和电流,以降低各回线感应的干扰电压。

2.4 整机电磁兼容性设计

在完成配电单元 3个功能模块的电磁兼容性设计后,进一步进行整机的电磁兼容优化。主要包括2个方面:一是3个功能模块在整机中的合理布局,二是整机的机壳屏蔽设计。

由于 DC/DC变换模块是配电单元的主要干扰源,所以将其设置于配电单元的底座上,并通过盖板将其封闭在一个独立的空间中,以阻断其对外的干扰途径,抑制其辐射发射。配电模块和数据采集与通信模块分板独立设计,并尽量加大两者之间的间隔,可降低配电模块对数据采集与通信模块的干扰。

屏蔽设计重点是考虑对辐射干扰的屏蔽,即确保结合面的搭接效果和减小缝隙。整机结构电磁兼容性设计的主要目标是改善其对外辐射发射(RE102)电磁兼容性能[8]。配电单元采取了下述措施来保证其良好的屏蔽效能:

1)箱体外表面无开孔和缝隙;

2)箱体各板搭接面和对外插座安装面未进行黑色阳极氧化处理,以确保搭接面之间的搭接效果;

3)机箱各连接面采取凹凸槽结构阻断电磁辐射通道。

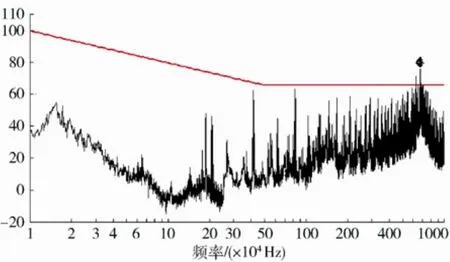

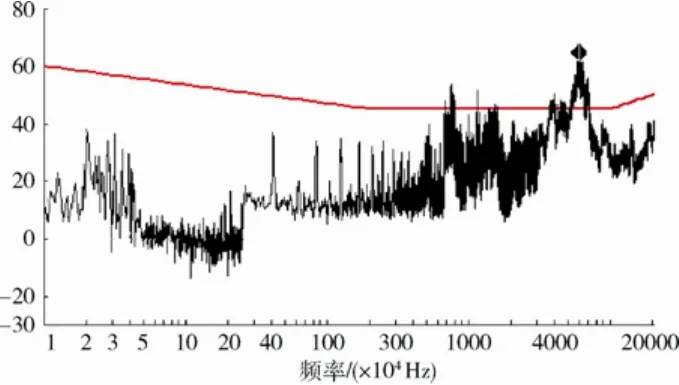

3 配电单元测试分析及改进措施

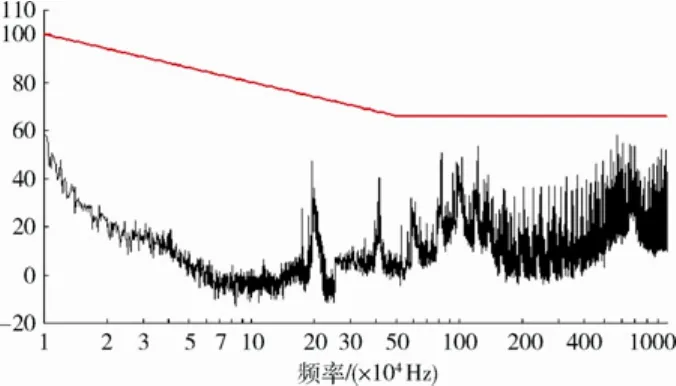

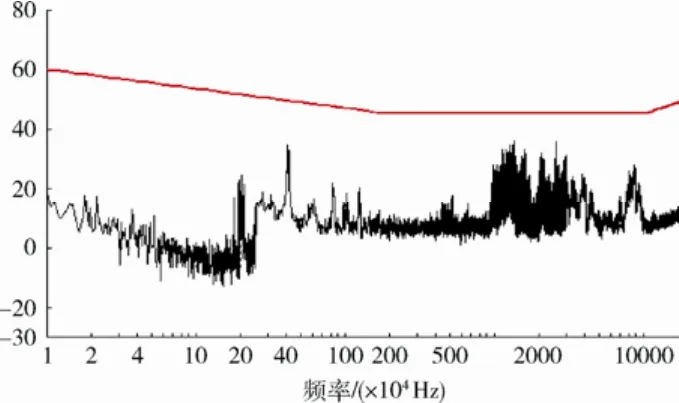

载人航天器电子产品发射类 CE102测试频段为10 kHz~10 MHz,RE102测试频段为10 kHz~1 GHz。图5和图6分别为配电单元的CE102和RE102(10 kHz~200 MHz)测试图。从测试结果可知,配电单元的这2项测试出现局部超标现象。分析其原因,发现配电单元的CE102和RE102测试结果与DC/DC变换器的CE102和RE102测试结果趋势相同,配电单元幅值较高点或超标点均为DC/DC变换器开关频率(200 kHz)的倍频点。这表明虽然单个DC/DC变换器能够满足电磁兼容性要求,但配电单元内部多台不同功率等级、不同输出电压的DC/DC变换器并联工作时,不同开关频率及其谐波存在干扰叠加效果,导致配电单元的电磁兼容性指标出现局部超标现象。

为了改善配电单元的电磁兼容性能,在多台DC/DC变换器并联输入的最前端加入一个共模电感(因超标点频率较高,故为共模干扰)。经测试,该共模电感在7 MHz和60 MHz处分别具有54.12 dB和46.25 dB的衰减量,满足设计需求。经过优化改进后的配电单元的CE102和RE102测试结果分别见图7和图8,整个频段均未超过限值并具有较大裕度。

图5 CE102测试图Fig. 5 CE102 test pattern

图6 RE102测试图Fig. 6 RE102 test pattern

图7 改进后CE102测试图Fig. 7 Improved CE102 test pattern

图8 改进后RE102测试图Fig. 8 Improved RE102 test pattern

4 结束语

航天器智能配电单元的电磁兼容性设计涉及高压大功率电路拓扑、低压模拟和数字电路、磁性器件以及结构等相关专业知识,并且寄生效应及其参数对电磁兼容性影响较大。通过采取分层设计方法,并经过初步设计、测试、分析、设计优化、再测试的循环迭代过程,有效解决了智能配电单元复杂的电磁兼容问题,满足载人航天器的电磁兼容性要求。通过智能配电单元的研制,还积累了宝贵的电磁兼容性设计工程经验,为后续航天器电子产品的电磁兼容性设计打下了坚实基础。

(

)

[1]陈淑风. 航天器电磁兼容技术[M]. 北京: 中国科学技术出版社, 2007: 27-28

[2]侯智烨. 继电器电磁干扰的分析及抑制[J]. 广播电视信息, 2009(8): 79-81

Hou Zhiye . Analysis and inhibition of relay electromagnetic interference[J]. Radio & Television Inforcation, 2009(8):79-81

[3]Caponet M C, Profumo F, Jacobs J, et al. Solutions to minimize conducted EMI in power electronic circuits[C]//Sixteenth Annual IEEE, 2001, 1(4-8): 220-224

[4]王雪华, 张伟, 杜青, 等. 燃料电池车用大功率DC/DC变换器电磁兼容性研究[J]. 电子机械工程, 2002, 18(1):22-29

Wang Xuehua, Zhang Wei, Du Qing, et al. Research on EMC of high power DC/DC converter for fuel cell electric vehicles[J]. Electro-Mechanical Engineering,2002, 18(1): 22-29

[5]王少宁, 张俊峰. 航天器DC-DC模块电源电磁兼容设计[J]. 安全与电磁兼容, 2007(4): 62-64

Wang Shaoning, Zhang Junfeng. Design of EMC for spacecraft DC-DC module supply[J]. Safety & EMC,2007(4): 62-64

[6]Clayton R P. Introduction to electromagnetic compatibility[M].John Wiley & Sons, 2006: 117-118

[7]潘宇倩, 白东炜. 电磁干扰的产生及PCB设计中的抑制方案[J]. 航天器环境工程, 2007, 16(3): 125-129

Pan Yuqian, Bai Dongwei. Cause of EMI and restraining scheme in PCB design[J]. Spacecraft Environment Engineering, 2007, 16(3): 125-129

[8]曾斌. 关于航天电子设备结构的EMC设计[J]. 电子机械工程 , 2002, 18(1): 56-58

Zeng Bin. On EMC design of spaceflight electronic equipment structure[J]. Electro-Mechanical Engineering,2002, 18(1): 56-58