改进的电容式微加速度计中电路噪声模型

2012-06-23刘云涛王颖邵雷

刘云涛,王颖,邵雷

(哈尔滨工程大学信息与通信工程学院,黑龙江哈尔滨150001)

加速度计是一种可以将加速度物理信号转化成能够测量的电信号的仪器,具有μg水平的高精度加速度计被广泛应用于导航、制导、空间微重力测量以及自动化工业中[1].随着微机电系统(MEMS)技术的发展,以及硅微加速度计的商业和军事价值的提高,电容式微加速度计成为微机电系统领域和微传感器领域内研究热点.

电容式微加速度计是由机械的敏感结构和电学的接口电路构成.由于在敏感结构与接口电路之间存在大量寄生电容的敏感结构所输出非常微弱的信号,对传感器设计提出了巨大的挑战,因此噪声特性成为高性能微加速度计系统设计的关键所在.随着敏感结构加工工艺的改进,电路的噪声性能已经成为影响系统精度的重要因素[2].

噪声模型是加速度传感器设计的基础,精确的噪声模型可以准确预测系统性能,并对电路优化提供巨大的帮助.1999年加州大学伯克利分校的M.Lemkin等[3]分析了电容式微加速度计中的电路噪声源,并建立了电路噪声模型.但该模型中忽略了开关电容电路中开关热噪声的影响,且没有分析相关双采样电路对输出噪声的影响.2006年密歇根大学的H.Kulah等[4]建立电容式微加速度计中的各电路噪声源模型,但在该分析中忽略了各噪声源间的相互影响.本文将针对现有电路噪声研究中的不足,详细分析各种电路噪声源,并将电路作为一个整体,建立更精确的电路噪声模型.

1 电路噪声源分析

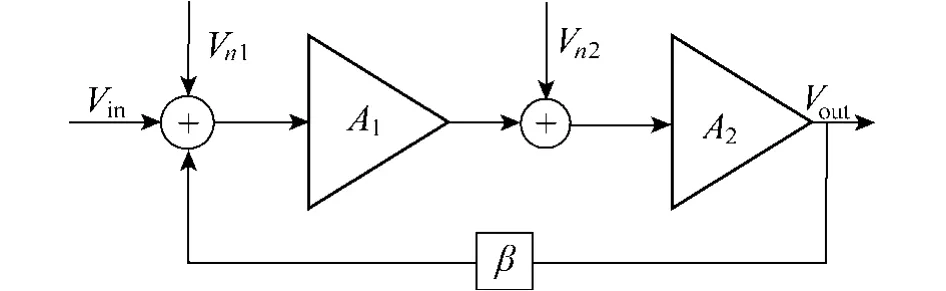

图1所示为考虑多级噪声注入的闭环系统,其中A1和A2分别表示第1级和第2级增益,Vn1和Vn2表示第1级和第2级的噪声注入,β为反馈因子,系统输出为

图1 闭环系统噪声分析Fig.1 Noise analysis of closed-loop system

由式(1)可以看出,如果A1足够大,Vn2可以忽略.由于微加速度计接口电路是由前级电荷积分器和后级放大、解调等部分组成,而前级电荷积分器具有非常高的增益,因此,接口电路前端的电荷积分器是系统的主要电路噪声源.

电荷积分器中的运算放大器包括3种噪声:热噪声、闪烁噪声(1/f噪声)、运放失调.热噪声是由于导体中电子随机运动引起的导体两端电压波动而产生的,热噪声与绝对温度成正比,属于白噪声.1/f噪声是由于MOS晶体管的栅氧化层和硅衬底界面处的悬挂键随机捕获电荷载流子而产生的.除了热噪声和1/f噪声,运放失调也是影响输出精度的主要原因,运算放大器的失调电压会被电荷积分器及后续放大电路进行放大,导致输出严重偏离,并且该电压会随温度和时间而变化,这在高精度加速度计中是不允许的.

热噪声均匀分布在整个频带内,属于宽带信号,而1/f噪声、失调和输入信号属于窄带低频信号,因此在低频情况下,1/f噪声和运放失调是电路中的主要噪声源.

在电路设计中,开关电容电路往往以CMOS传输门或伪管开关作为开关,可以有效地抑制电荷注入和时钟溃通的影响,但是该开关的非零导通电阻会产生宽带热噪声[5].

敏感结构与接口电路之间的连接会产生寄生电阻和寄生电容.该寄生电阻会引入热噪声,寄生电阻与敏感结构到前级运放之间的连接方式有关.对于采用体硅工艺和CMOS标准工艺制作的双片集成微加速度计,是通过金属线或者硅铝丝压焊来连接,该寄生电阻也可以不用考虑.由于通过设计可以使电荷积分器对寄生电容不敏感,因此也可以忽略寄生电容的影响[6-7].

微加速度计工作时,2个频率相同、相位相反的高频驱动信号分别加载在2个固定极板上,产生与输入加速度信号成正比的电荷,并通过电荷积分将电荷转化为电压.电荷积分器的输出可以表示为

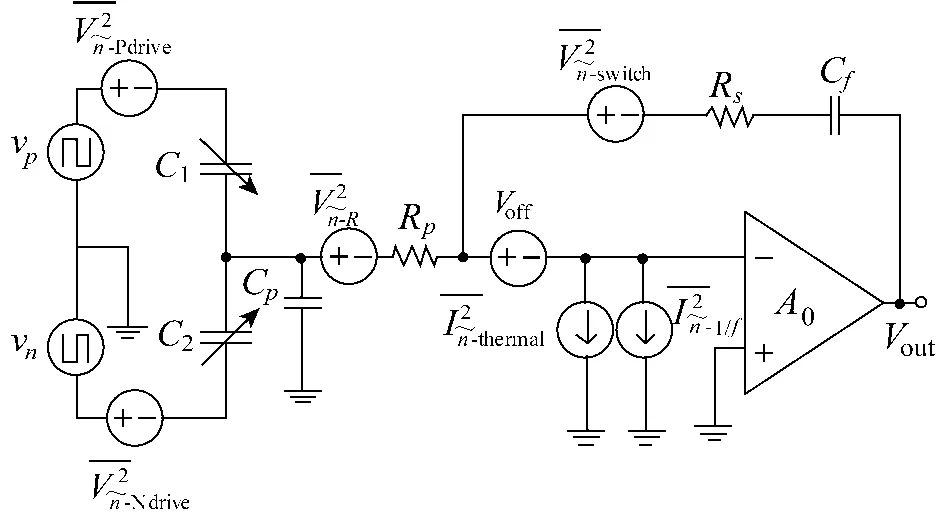

式中:VR为产生驱动信号的参考电压,因此参考电压源的噪声直接作用在电荷积分器输出上,成为电路的一个重要噪声源.图2表示出电容式微加速度计中的主要电路噪声源,其中表示运放热噪声表示运放的1/f噪声,Voff表示运放失调,为开关热噪声为寄生电阻热噪声,和为高频驱动信号噪声.

图2 电路噪声源Fig.2 Electronic noises source

包括热噪声和1/f噪声的运放输入参考噪声谱[8],可以表示为

式中:S0表示白噪声功率谱;fk为转角频率,即白噪声和1/f噪声相等时对应的频率.在CMOS器件中,转角频率在1~100 kHz之间,这意味着不考虑噪声折叠情况下,在传感器带宽内1/f噪声占主要成分.

对于低频1/f噪声和运放失调可以通过斩波稳定(CHS)和相关双采样技术(CDS)予以消除[9].CHS方法主要应用于连续时间处理电路,对于离散时间的数据采样系统,CDS是最为广泛使用的消除低频噪声的电学方法[10].相关双采样就是对信号进行间隔很近的采样,然后对采样的结果进行相减运算的过程.然而CDS在抑制运放失调和1/f噪声同时,也引起了热噪声混叠.

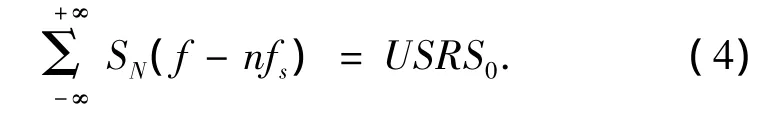

由于热噪声属于宽带白噪声,采样频率会远低于热噪声带宽,假设热噪声带宽为BWth,采样频率为fs,定义2BWth/fs=USR为欠采样率,因此采样过程中会在采样频率的整数倍附近产生噪声混叠,各个混叠部分噪声叠加,导致输出热噪声功率谱为USRS0.该噪声折叠过程表示为

从总的热噪声功率谱中减去基带噪声就可以得到折叠所产生的噪声功率谱:

具有一阶低通特性的白噪声,其功率谱可表示为

式中:fc为运放的单位增益带宽.因此热噪声带宽BWth为

将式(8)代入式(5)中,折叠产生的热噪声功率谱为

尽管1/f噪声为窄带噪声,仍然会在该噪声尾部产生混叠,混叠产生的1/f噪声功率谱为

由式(9)和(10)可见,采样所造成的热噪声折叠与fc/fs成正比,而1/f噪声折叠与fc/fs成对数关系,所以热噪声折叠远大于1/f噪声折叠.

由以上分析可知,相关双采样消除了低频1/f噪声和运放失调影响,但同时引起热噪声和1/f噪声折叠,所产生的折叠热噪声为初始热噪声的πfc/fs倍,并且在折叠噪声成分中,热噪声占主要部分.因此,在电荷积分器中运放的噪声可以简化为噪声折叠后的热噪声.

图3为所设计的电荷积分器噪声的Hspice工具仿真结果,设计参数:fs=256 kHz,fc=44.3 MHz.运放热噪声为17.54 nV/Hz1/2,由仿真结果可见,在频率小于10 kHz部分,CDS大大降低了电荷积分器的1/f噪声,当频率高于37.8 kHz后,由于采样过程中引起的噪声折叠导致此时带有CDS的电路噪声高于没有CDS的电路噪声.

图3 电荷积分器噪声Hspice仿真结果Fig.3 Simulated result of charge integrator noise with Hspice

2 电路噪声模型建立

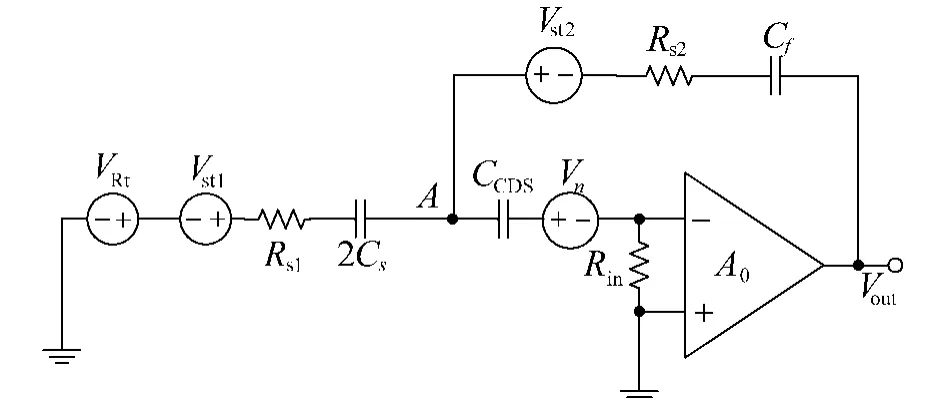

图4表示电荷积分器在放大状态下的噪声模型,Vst为表示CMOS开关导通电阻的热噪声电压,VRt为参考电压源噪声,Vn为运算放大器输入参考热噪声,Rs表示开关导通电阻,Rin表示运放输入阻抗,Cs为敏感结构电容,Cf为反馈电容,A0为运放直流增益.

图4 电荷积分器在放大模式下的噪声模型Fig.4 Noise model of charge integrator with amplifing mode

在节点A根据基尔霍夫定理,具有如下表达式:

又因为

将式(13)代入式(11)中得到

由于运放的直流增益和输入阻抗非常高,Vout(s)可以简化为

处于放大状态的电荷积分器放大倍数A可以表示为

因此电荷积分器的输入参考电噪声为

输入参考噪声的功率谱密度(PSD)为

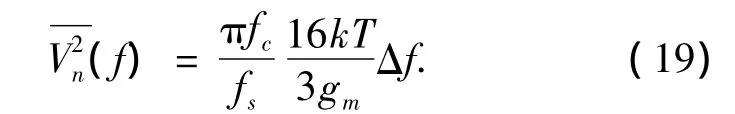

对于一个设计良好的低噪声运放,其输入参考热噪声主要由输入晶体管决定,考虑相关双采样引起的噪声折叠,该噪声可以由式(19)表示,这里的gm为输入晶体管的跨导.

CMOS开关热噪声为

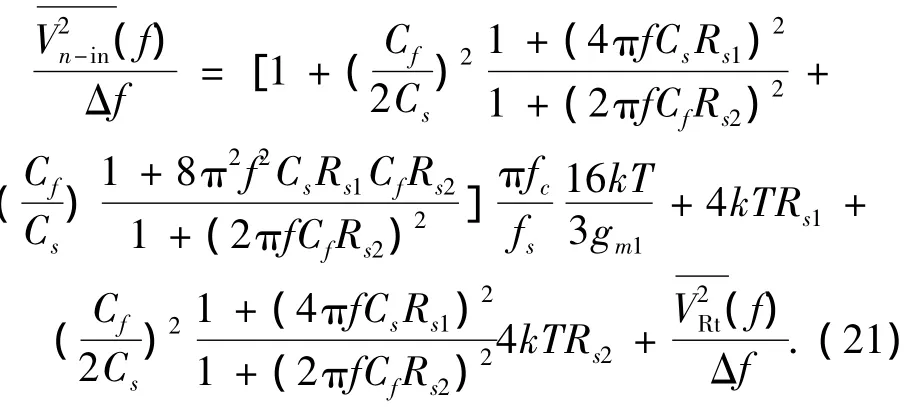

将式(19)和(20)代入式(18)中,可得电荷积分器的输入参考噪声为

如果Cf=2Cs,Rs1=Rs2,上式可以简化为

由式(21)和(22)可知,电路噪声主要依赖于采样频率,以及Cf与Cs的比例,所以提高采样频率,降低Cf/Cs可以降低电路噪声,但同时增加了电路设计难度,甚至在提高绝对噪声的同时降低信噪比.

3 结果与讨论

图5为所建立的电路噪声模型与仿真结果对比,仿真过程中取与式(22)相同的条件:fc=44.3 MHz,Rs=950 W,Cf=2Cs=5 pF,gm=161 μS,参考电压源噪声取10 nV/Hz1/2.由图3可知,虽然CDS可以大大降低1/f噪声,但是不能够完全消除,随频率升高噪声仍有小幅下降,当频率达到100 Hz后,噪声下降极为缓慢,可认为此时噪声不再随频率而变,因此以下所有的仿真结果均取频率为100 Hz处的噪声.由图5可见,依据所建立电路噪声公式计算结果与仿真结果非常接近,由于模型建立过程中忽略了1/f噪声折叠和寄生电容影响,因此理论计算结果略低于仿真结果.

图5 电路噪声模型与仿真结果对比Fig.5 Comparation of electronic noise model with simulated result

采用0.5 μm两层金属两层多晶n阱CMOS工艺对所设计的接口ASIC进行了流片,芯片如图6所示,芯片面积为4.6 mm ×3.7 mm.

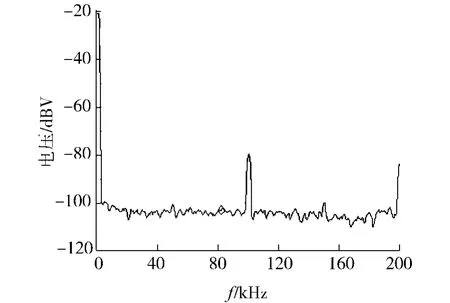

为了验证所建立的电路噪声模型,对该芯片的电路噪声进行了测量,在电路的输入端接一个低噪声的电容器,电容另一端接地,取值与前级电荷积分器的积分电容相同.后级放大倍数设定为-1,采用HP35670A动态信号分析仪对电路中采样保持输出节点做频谱分析,由于在此测试状态下,输入到采样保持输出节点的增益为1,因此所测结果即为电路的输入参考噪声.图7为输出的测试结果.测试结果表明,芯片的电路噪声为-103.07 dBV/Hz1/2,等效于7 μV/Hz1/2,在相同的参数条件下,根据所建立的电路噪声式(21)计算结果为5 μV/Hz1/2,由此可见,所建立的电路噪声模型能够准确的预测电路噪声水平.

图7 输出电路噪声频谱Fig.7 Spectrum of output electronic noise

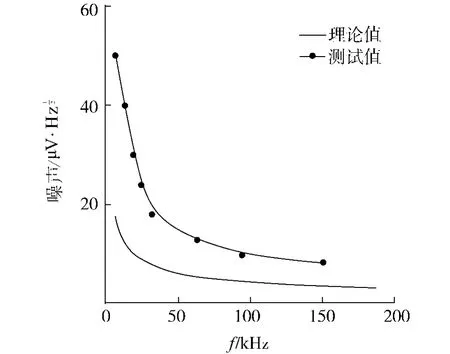

为了测试电路噪声与采样频率的关系,将电路连接为时钟信号外部产生方式,利用信号发生器提供初始时钟信号.电路噪声与采样频率关系测试结果如图8所示,同时在该图中也描绘出式(21)理论预测曲线,尽管测试结果与理论预测存在一定的差距,但测试结果与理论曲线具有相同的趋势,即随着采样频率的提高,电路噪声不断降低.

图8 电路噪声与采样频率关系Fig.8 Relationship between electronic noise and sampling frequency

为了更全面地分析系统的电路噪声,将研制的ASIC芯片与加速度计敏感结构组合在一起,制成微加速度传感器,如图9所示,并对该加速度计进行开环噪声测试.在1 g状态下,对传感器的输出进行频谱分析,输出结果如图10所示,结果显示开环模式下,系统的噪声密度为-95.02 dBV/Hz1/2,等效于15 μV/Hz1/2,由于系统灵敏度为 1.22 V/g,因此噪声密度为 12 μg/Hz1/2.

图9 双片集成的微加速度传感器Fig.9 Two chip integrated micromachined accelerometer

图10 开环模式输出频谱Fig.10 Spectrum of output with open-loop mode

与单芯片测试结果相比,此时输出噪声增加了8 μV/Hz1/2,这是由2部分噪声导致机械噪声和驱动信号噪声.所使用的敏感结构机械噪声约为2 μg/Hz1/2,等效于 2.5 μV/Hz1/2,所以驱动信号噪声约为6 μV/Hz1/2.由于在本课题中驱动信号是通过开关电源产生的,所以驱动信号噪声一部分为电源噪声,另一部分为开关热噪声.经测试,电源噪声在-160 dBV/Hz1/2水平,远低于输出噪声,因此所增加的电路噪声来自于开关热噪声.由此可知,在高精度微加速度计系统中,开关热噪声对系统的输出精度起至关重要的作用.

4 结束语

在详细分析电容式微加速度计中的电路噪声源的基础上,建立了等效输入电路噪声模型,根据所建模型可知,电路噪声主要依赖于采样频率以及反馈电容和敏感电容的比值.仿真和测试结果显示,所建立的噪声模型能够准确的预测电路噪声水平,另外,产生的高频驱动信号开关热噪声对系统的电路噪声水平具有重要影响作用.

[1]LEE W F,CHAN P K.A capacitive-based accelerometer IC using injection-nulling switch technique[J].IEEE Transactions on circuits and systems,2008,55(4):980-989.

[2]ALTONEN L,HALONEN K.Continuous-time interface for a micromachined capacitive accelerometer with NEA of 4 μg and bandwidth of 300 Hz[J].Sensors and Actuators,2009,154:46-56.

[3]LEMKIN M,BOSER B E.A three-axis micromachined accelerometer with a CMOS position-sense interface and digital offset-trim electronics[J].IEEE J of Solid-State Circuits,1999,34(4):456-468.

[4]KULAH H,CHAE J,YAZDI N,et al.Noise analysis and characterization of a sigma-delta capacitive microaccelerometer[J].IEEE Solid-State Circuits,2006,41(2):352-361.

[5]OLIAEI O.Thermal noise analysis of multi-input SC-integrators for delta-sigma modulator design[C]//Proceeding of IEEE Int Symp Circuits and Systems.Geneva,Switzerland,2000:425-428.

[6]LIU Yunao,LIU Xiaowei,CHEN Weiping,et al.Design and noise analysis of a sigma-delta capacitive micromachined accelerometer[J].Journal of Semiconductor,2010,31(5):0550061-0550066.

[7]刘云涛,姜一鸣,尹亮.四阶Sigma-Delta微加速度计系统设计与分析[J].哈尔滨工业大学学报,2011,43(7):38-41.

LIU Yuntao,JIANG Yiming,YIN Liang.System design and analysis of fourth-order sigma-delta micromachined accelerometer[J].Journal of Harbin Institute of Technology,2011,43(7):38-41.

[8]WONG S L,SALAMA T.A switched differential Op-Amp with low offset and reduced 1/f noise[J].IEEE Trans on Circuits and Systems,1986,33(11):1119-1127.

[9]LEE T H,CHO G,KIM H J.Analysis of 1/f noise in CMOS preamplifier with CDS circuit[J].IEEE Trans on Nuclear Science,2002,49(4):1819-1823.

[10]HYNECEK J.CDS noise reduction of partially reset charge-detection nodes[J].IEEE Trans on Circuits and Systems,2002,49(3):276-280.