一种C波段小步进捷变频频率综合器的设计

2012-06-23由法宝张春荣余铁军

由法宝 张春荣 余铁军

(西安电子工程研究所 西安 710100)

1 引言

频率综合器作为现代电子系统的心脏,是决定电子系统性能的关键设备。随着现代军事、国防及无线通信事业的发展,雷达、电子对抗、制导武器、移动通信和电子测量仪器等电子系统对频率综合器提出了越来越高的要求。世界各国都非常重视频率综合器的研究与应用,精细步进、超低相噪、高纯频谱、快速捷变和高输出频段的频率综合器已经成为频率综合器发展的主要趋势。

小数分频锁相环是近年来迅速崛起的一项新技术,它具有宽带、低相位噪声、高分辨率等优点。随着全数字Σ-Δ调制器技术的日益成熟,大大地抑制了量化噪声,改善了杂散指标,使得小数分频锁相环的工程应用成为可能。

2 系统主要指标与方案

2.1 系统主要指标

体积:50×90×16mm3

输出频率:6.7~7.3 GHz

频率步进:1 MHz(或更小)

相位噪声:≤-90 dBc/Hz@1kHz

杂散抑制:≤-70 dBc

输出功率:≥10 dBm

捷变时间:≤1 μs

2.2 系统方案与器件选型

由以上指标分析,该系统体积小、频率步进小、相位杂散指标高并要求频率捷变,要满足所有指标要求有一定的难度。

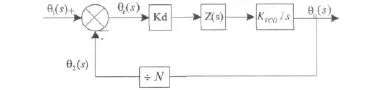

本设计采用双小数分频锁相环“乒乓”工作的方案,系统方案如图1所示,主要由功分器、小数分频锁相环、单刀双掷开关组成。100MHz低相位噪声恒温晶振参考信号经功分器进入两个锁相环作为鉴相基准信号,通过FPGA控制锁相环的锁定频率和单刀双掷开关的切换来实现捷变频微波信号的输出。

图1 乒乓锁相环方案框图

在器件选型上根据技术指标要求,综合考虑成本、体积等因素,选择了集成度高、体积小、功能强大的芯片。

鉴相器选用美国Hittite公司的HMC700LP4,它可以工作在小数模式、整数模式和简单的FSK调制模式。相噪基底为-221/-226 dBc/Hz(小数/整数),工作频率达高达8GHz,集成有14位前置分频器、16位整数分频器、24位小数分频器、鉴相器和电荷泵组成,最高参考频率为225MHz,频率分辨率达赫兹级,串口控制速率达50MHz,并且采用CSP技术大大缩短了环路的锁定时间。

VCO选用美国Hittite公司的HMC507LP5,输出频率为6.65-7.65GHz,输出功率为13.5dBm,二分频输出为3.325-3.825GHz,相位噪声为-115dBc/Hz@100kHz,+5V供电。

单刀双掷开关采用微波PIN管实现,体积小、隔离度高,开关速度快(可以达到50ns),加上FPGA控制电路的延时频率切换时间小于1μs。

3 系统性能指标分析与环路参数设计

3.1 相位噪声与杂散分析

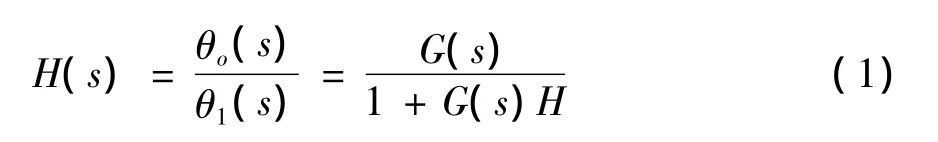

锁相环的线性相位模型如图2所示。

图2 锁相环线性相位模型

闭环传递函数:

开环传递函数:

误差传递函数:

其中:G(s)=KdKVCOZ(s)/s为前向传递函数,H=1/N为后向传递函数。

为分析问题方便,现对环路带宽ωc和相位裕量φp定义如下:

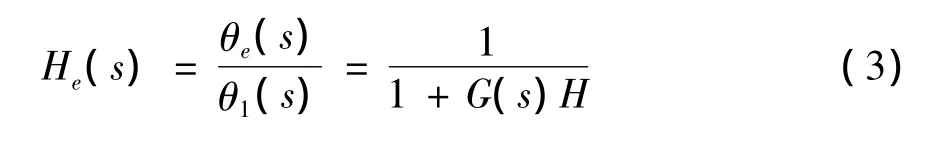

利用上边的定义分析可得:

由闭环反馈理论分析可知,锁相环对参考晶振、分频器、鉴相器附加的相位噪声呈低通特性,以上噪声源统称为带内噪声,而对压控振荡器附加的相位噪声呈高通特性,为了兼顾这一对矛盾,选择环路带宽fc在两噪声源谱线的交叉点附近总是比较接近于最佳状态的。

工程分析中,鉴相器产生的相位噪声一般按下式简单估算:

相位噪声=(1Hz归一化噪声基底)+10log(鉴相频率)+20log(N)

本方案中,小数模式下锁相环的鉴相基底为-221dBc,以50MHz为参考,输出7GHz估算,带内噪声基底约为-100dBc,满足设计指标要求。

系统杂散主要来自于鉴相频率杂散、锁相环隔离杂散和Σ-Δ调制杂散。由于鉴相频率为50MHz,远大于环路滤波器带宽,因此鉴相参考杂散能够被很好的抑制,两个锁相环之间的隔离泄漏杂散可以通过合理的电磁兼容设计来抑制,本设计的难点是如何有效抑制Σ-Δ调制杂散,由于Σ-Δ调制杂散分布在小数频率分量的各次谐波上,小步进应用下整数边界频点处一阶杂散离环路带宽很近,如何对其进行有效的抑制是环路滤波器设计的重点和难度。

3.2 环路参数设计

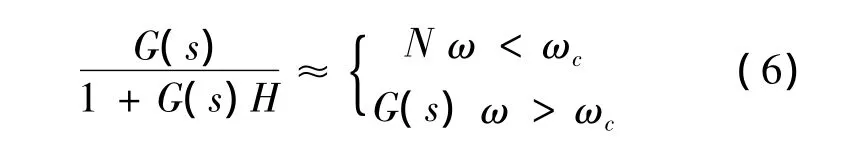

本设计为了满足高杂散指标的要求,对带外小数Σ-Δ调制杂散的抑制是环路滤波器设计的关键,环路带宽的选取必须在锁定时间、相位噪声和带外抑制之间折中。一般的三阶环路滤波器已经无法满足设计要求,本设计选用的环路结构如图3所示,在三阶环路的基础上增加一级LC滤波,图中运算放大器AD797的作用有二:一是加强隔离,二是提高VCO的控制电压。R4、R5为比例电阻,取R4=120Ω,R5=180Ω。滤波器的传递函数为:

图3 环路滤波器结构

开环传递函数为:

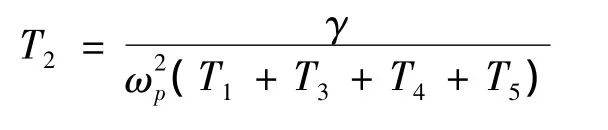

其中,T31,T41,T51定义为极点比率,该环路实际上是六阶环路,无法计算准确求解所有元器件的值,本设计以极值相位裕量设计法为指导,近似计算如下:

开环相位裕量定义如下:

对上式求导,略去高此项,近似求解得:

由于是近似解,引入优化因子γ,初次设计取1即可。

令开环增益在环路带宽处为1可求得A0。

为进一步分析问题的方便,令T31=T41=T51,求得元器件的值如下:

在以上环路滤波器参数计算的基础上,合理设定环路带宽、相位裕量、带外抑制等指标,应用ADS软件进行参数的优化仿真,最终得到的环路参数值如下:

仿真表明,环路带宽为100kHz,相位裕量为46°,闭环带外抑制在1MHz处达到60dB,这对带外杂散和Σ-Δ调制器引入的高通噪声将有较好的抑制效果。

4 硬件实现与指标测试

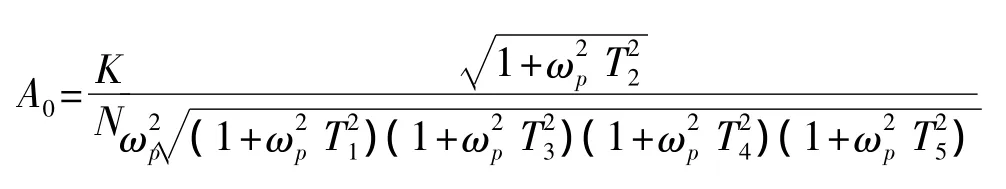

为了提高隔离度,双锁相环采用分腔设计,开关与锁相环通过SMA连接进一步提高隔离,电源与FPGA控制信号通过15芯矩形连接器引入,整个锁相电路如图4所示。

图4 锁相环实物外形图

该锁相电路既有高频电路又有低频电路,对电路进行电磁兼容设计是十分必要的,数字电和模拟电要分开布局,高频电路采用多点接地,印制板采用大面积接地设计。加强对电源的去耦滤波,电源走线尽量粗而短,通过在电源与地之间跨接不同容值的电容来滤除电源中的高频分量和低频分量,在靠近芯片管脚的地方放置0.1μF和10pF的滤波电容。

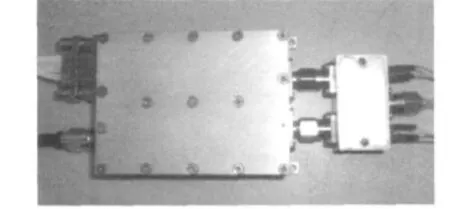

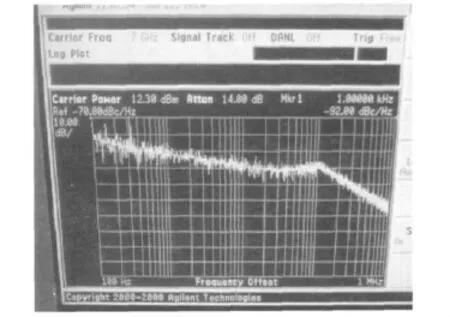

指标测量选用安捷伦公司的频谱分析仪E4447A,以1MHz为步进,相位噪声可以达到 -90dBc/Hz@1kHz,杂散在最差频点处优于70dBc(整数边界杂散),如图5和图6所示。两个锁相环的隔离度大于80dB,跳频时间取决于开关的切换速度,远远小于1μs。各项指标均达到设计指标要求。

图5 相位噪声测试

图6 杂散指标测试

5 结束语

本设计采用高性能的小数分频锁相环芯片,通过乒乓工作方式实现了一种小步进、低相噪、低杂散的微波频率综合器的工程设计,各项指标均达到设计要求。如果排除VCO二分频电路对小数调制器杂散分量的搬移作用,1MHz步进情况下杂散指标将优于80dBc。本设计是对小数分频锁相环工程应用的有益探索,对今后的工程设计具有重要的参考价值。

[1]Dean Banerjee.PLL Performance Simulation and Design[J].USA National Semiconductor,2003.

[2] 张春荣.雷达捷变频频率综合器技术及跳频时间测量[J].火控雷达技术,2004(12):42-45.

[3]张春荣.电子设备电磁兼容设计研究[J].火控雷达技术,2007(6):10-15.

[4] 刘光祜.锁相跳频源极值相位裕量设计法[J].电子科技大学学报,2001(12):551-554.

[5]吴恩德,王志华等.分数N频率综合器的杂散分析[J].清华大学学报,2004:958-961.

[6]岳金山.分数分频锁相环频率合成器的研究[D].成都:电子科技大学,2005.