并行测试技术及在军事通信系统测试中的应用研究*

2012-06-07陈二虎

刘 磊 陈二虎

(1.海军91551部队 九江 332000)(2.海军工程大学电子工程学院 武汉 430033)

1 引言

在军事通信系统测试中,传统的测试方法主要是串行测试,一次只能测试一个被测件(Unit Under Test,UUT),测试中价格昂贵的测试设备的平均闲置时间占到整个测试时间的50%以上[1]。

并行测试是近年来自动测试领域兴起的一种先进的测试技术和方法。并行测试技术属于下一代测试技术范畴,是支撑NxTestATS的新技术之一。它根植于并行处理技术,其宏观表现为,在并行测试程序的控制下对多个UUT同时测试[2]。相比传统顺序测试技术,它通过对系统资源的优化利用可以大幅度提高测试系统的吞吐量,提高测试资源利用率,降低整个武器装备测试成本(测试成本包括测试时间)[1~4]。因此,研究并行测试技术对我军测试技术的发展和提高武器装备后勤保障以及战时的快速维护保障能力具有重要意义。

2 并行测试的概念

并行测试技术是把并行处理技术引进到自动测试领域中所形成的一种先进的测试技术和方法,指ATS在同一时间内完成多项测试任务,完成多个UUT的测试。核心是可以同时对多个被测对象进行测试。对各个UUT的测试过程是独立并行的。

3 并行测试技术的实现方式

3.1 多个UUT的并行测试实现方式

复制多套设备完成并行测试:提供几套相同的测试设备,每个UUT对应一套测试设备,在同一时间内在测试主控机的控制下独立进行测试,如图1所示。这种并行测试实现方式简单可靠,缺点是测试成本会随着测试设备的增加而成倍增加。

图1 多套设备实现多UUT并行测试结构

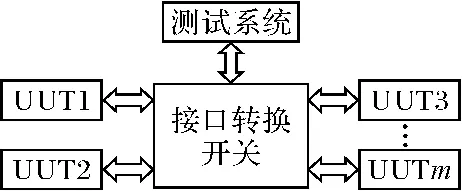

通过接口转换开关实现并行测试:通过接口转换开关将不同的UUT连接到一套测试系统上进行测试,如图2所示。具体实现过程:首先将第一个UUT进行测试,在处理器对测试信号进行分析时,接口开关断开第一个UUT,连接第二个UUT进行测试,依次类推到多个UUT。这种方法使测试系统长时间处于忙碌状态,减少闲置时间,提高了系统的吞吐量,缺点是并行度不高,并不是真正的并行测试。

图2 接口转换开关实现多UUT并行测试结构

多个测试交替进行的并行测试:由于处理器速度远远高于I/O设备和测量仪的速度,所以可以将多个测试在时间上形成交错来进行。在这种实现方式中,开始测试执行时就并行执行所有测试任务,当某项测试所需资源被占用时,处理器并不等待而是直接跳过执行下一项测试,待完成后再返回执行未完成的测试。这种方式要求每项测试是独立的,否则容易产生多个测试在同一时刻相互等待对方释放测试资源,从而产生资源竞争,导致系统死锁。

3.2 单个UUT的并行测试实现方式

单个UUT上的并行测试主要是通过采用多通道测试方式来实现,在UUT内部同时对多个参数进行测试,它要求不同参数测试之间的激励和响应互不影响。主要有两种实现方式:交迭等待并行测试和分组并行测试。

1)交迭等待并行测试:这种方式是UUT在到达目标状态的过程中进行参数的测试。首先,要分析清楚不同激励之间的关系,确定不同项测试的激励和测量不会互相影响。其次,为避免测试不能完成,要求每项测试不允许中断,只有一项测试完成后才能响应UUT到达指定状态的中断。严格意义上,这种方式并不是真正的并行测试,只是利用测试设备等待UUT到达指定状态的等待时间段内对满足测试条件的参数进行测试。

表1 通过交迭等待实现单个UUT并行测试

2)分组并行测试:同步或异步地运行两个或多个测量程序,分别在不同的线程内完成对多个参数的测量。将具有相同的测试要求的被测量分到同一组中,这样在并行运行的时候不会互相影响。分组在测试需求分析时完成。

表2 通过任务分组实现单UUT的并行测试

4 并行测试的体系结构

对应并行测试实现方式可将并行测试系统划分为多处理器并行测试结构和单处理器并行测试结构两类基本架构形式。

4.1 多处理器并行测试结构

由于执行并行测试的处理器之间的关系不同又可分为分布式和从处理器结构。

·分布式结构:每台计算机均可独立高效地执行测试任务,测试任务被动态地分配到各个计算机上,网络操作系统管理本地测试进程的运行,向网络申请资源,协调各计算机之间的通信和资源共享。分布式结构是真正意义上的并行测试结构。但是,分布式并行测试结构增加了配套的如网络设备、测试仪器等硬件资源,导致测试成本上升。

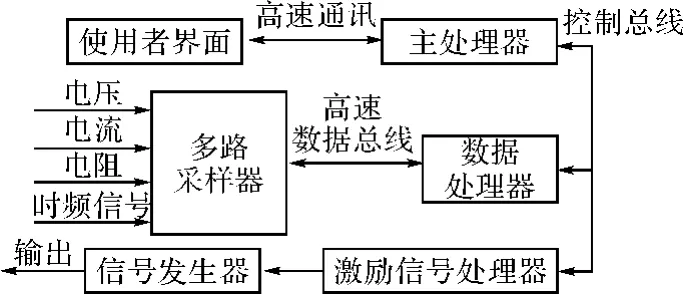

·从处理器结构:在从处理器结构中,系统具有两个以上处理器协同工作,从处理器在系统中处于从属地位,功能单一,性能较低,分担主处理器的部分工作,减少主处理器的工作量,提高测试效率。图3是Agilent公司开发的一种从处理器结构测试系统。它将一块数据处理芯片(DSP)嵌入到测试系统中和CPU并行工作,分担CPU的数据计算处理任务,减轻CPU的工作负担,从而提高系统速度,减少了测试时间。

图3 从处理器结构

4.2 单处理器结构

单处理器结构通过把处理器的不同处理时间片段分配给不同的测试任务,主要通过软件设计上的多线程和多进程结构来实现。

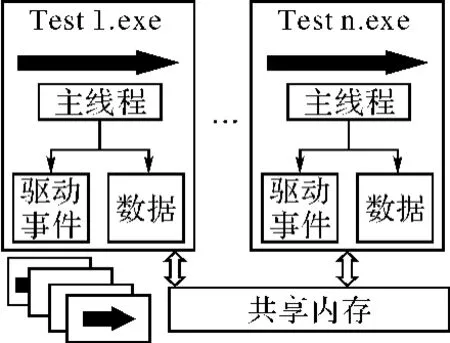

在多进程结构中,处理器将不同的测试任务分配到不同的进程中,通过进程的切换来实现并行测试。操作系统隔离每个进程的内存地址空间,防止因一个测试进程故障导致整个系统发生崩溃,这样造成了仪器设备和数据共享变得困难、效率低。

在多线程结构中,一个进程中多个线程同时执行测试任务,所有的测试任务看做一个进程,处理器将测试任务分配给不同的线程,通过线程的切换实行并行测试。所有线程都属于同一个进程,能更好地共享测试资源和数据,而且多线程之间的切换相对于多进程之间的切换,内存开销要小的多,是一种合适的并行测试软件结构。

图4 多进程结构示意图

图5 多线程结构示意图

5 并行测试在军事通信系统中的应用

传统通信系统测试中,组成通信系统的各个设备基本上采用串行的测试方式。测试设备在对故障设备进行测试时往往是按照顺序进行测试,且要等待故障设备到达指定状态,导致处理器和测试设备平均大部分时间处于空闲状态,测试时间长,测试效率不高。

5.1 通信系统并行测试基本结构

随着通信技术的发展和通信系统的日趋复杂化,测试变得更加复杂。如果还是采用传统串行测试方式,将不能满足现代战争对战场快速维修保障的要求。因此,将并行测试技术应用到军事通信系统测试领域是通信测试技术发展的必然要求,也是实现对军事通信场外快速测试,实现战时快速保障的一个可行的技术路线。通信系统并行测试的基本结构如图6所示。

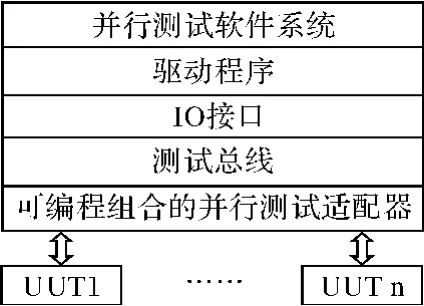

通信并行测试系统,主要由并行自动测试设备、被测单元和可编程并行测试适配器相互连接,以及相应的测试软件系统组成。其中,软件系统作为整个测试系统的最高层,主要在测试过程中,根据具体测试任务的不同,按照一定的调度算法,实时地对测试任务进行最优化并行调度;基于总线的自动测试系统通过可编程组合的并行测试适配器,与被测试对象通信设备相连接,在测试系统的控制下,按照一定的算法,通过适配器的开关切换、多通道测试等方式,实现并行测试。

5.2 通信系统并行测试关键技术

在通信设备测试中应用并行测试技术,使得自动测试系统能在同一时间内完成多项测试任务。这就需要对被测试任务和拥有的测试资源进行合理的调度,否则在测试中会出现由于不同任务占用同一资源而导致的死锁现象。因此,实现通信设备的并行测试,主要需要考虑以下几点。

1)任务的并行调度[7]

系统要完成m个测试任务t1,t2,…tm,有n个测试资源r1,r2,…rn分配给相应的测试任务,每个任务具有一系列资源组合的选择。对于每一种可供选择的测试资源组合,需要明确处理该任务所需占用该组测试资源的时间。记为:ti={(Ri1,Ti1),(Ri2,Ti2),…(Rik,Tik)}。其中,每一个Rij称为测试资源模式。Tij为在该种资源模式下完成测试任务ti所需的测试时间。在这样的情况下给出一个任务调度序列,使得系统完成这些任务的时间跨度最小,并满足一下约束:

(1)每个测试任务需要的测试资源给定;

(2)每个测试资源在任意时刻只能处于一种状态;

(3)每个测试任务执行的时间是有限的,且不可中断,测试任务完成后,立即释放占用的所有测试资源。

因此,测试任务的并行调度的最终目标是,找到使完成所有测试任务所需要的时间Tend最短的测试任务组合。

2)死锁预防

死锁是指多任务在并行运行中为了竞争有限的资源而陷入了一个僵局。一个任务锁定了另一个任务所需要的资源,而另一个任务又锁定了这个任务所需要的资源,两个任务都在等待对方释放资源,这就形成了一个死循环。所以,在并行测试系统设计中要合理的分配测试资源给被测任务,在并行测试系统组建之前必须考虑死锁现象。

3)通信设备并行测试系统的组建原则

图6 通信并行测试系统结构图

通信系统的地面自动化测试系统组建中,由于被测试的对象繁多,而且有些测试对象的参数之间相关性很强,在选择并行测试系统结构时往往倾向于几种并行测试结构的混合使用。如首先建立多处理器系统的并行测试结构,然后在每个分系统中再建立多进程结构,每个进程中又是多线程结构,当然这些组合都必须权衡整个测试系统的组建成本和系统的复杂度问题。

5.3 军事通信系统并行测试的意义

军事通信系统组成设备多且复杂,迅速判断其质量状况的好坏在通信系统定期保障和战时保障中具有重要意义,尤其是在分秒必争的战时保障中,每一个环节的效率都对整个作战指挥系统起到不可估量的作用。

由于检测设备的技术水平不断发展,设备的使用操作人员需要经过一定的专业培训,具备一定的专业基础,通常要定编、定岗。因此,实现单位时间内多台通信设备的并行测试对部队作战效能的提高、维护保障费用的降低具有关键作用。

6 结语

并行测试技术已经成为近年来自动化测试领域的热点课题。这是一项崭新的技术,还有许多基础性理论问题有待探讨,本文对并行测试的实现方法、基本结构以及在军事通信系统中的应用的一些关键技术进行了一个基本的描述。并行测试技术是在ATS进一步减少测试时间、降低测试成本的发展趋势下兴起的一项新技术,将其应用到通信设备的自动化测试中是实现未来战场通信设备快速测试的一个可行的技术路线。

[1]McDonnell R.Benefits of Parallel Testing [EB/OL].http://www.ni.com/Developer zone,2002.

[2]肖明清,朱小平.并行测试技术综述[J].空军工程大学学报(自然科学版),2005,6(3):22-25.

[3]Wiliam A Ross.The Impact of Next Generation Test Technology on Aviation Maintenance[C]//AUTOTESTCON proceedings.IEEE,2003:2-9.

[4]McDonnell R.Parallel Test Architectures for Reducing the Cost to Test[EB/OL].http://www.ni.com/Developer zone,2004.

[5]李华,许化龙.并行测试技术及在导弹测试中的应用研究[J].计算机测量与控制,2009,17(11):2216-2219.

[6]刘琪,孟庆虎.并行测试技术及在空空导弹检测中的应用浅析[J].计测技术,2010,30(1):8-10.

[7]王磊,肖明清.多核并行测试系统研究[J].西安交通大学学报,2008,42(6):683-684.

[8]William A Ross.统一美国国防部的自动测试系统标准[S].美国海军航空系统系统司令部PMA260D办公室.

[9]J.LAnderson Jr.High Performance Missile Testing[C]//AUTOTESTCON proceedings.IEEE,2003:19-27.

[10]陈希林,胡诗国.Ai7技术及在并行测试改造中的应用研究[J].电测与仪表,2007,44(1):48-51.