信号到达检测技术的FPGA设计实现

2012-01-19郭永

郭 永

(广州海格通信集团股份有限公司超短波部,广东广州 510663)

信号到达检测技术的FPGA设计实现

郭 永

(广州海格通信集团股份有限公司超短波部,广东广州 510663)

介绍了数字通信中的信号到达检测技术,已在Xilinx FPGA芯片上实现,并且应用于某高速数据传输系统。通过人为加入噪声测试、实际应用环境测试等不同手段测试表明,文中介绍的信号到达检测模块,能够满足系统的虚检概率和漏检概率指标要求。

信号检测;FPGA;数字通信

信号到达检测模块是数字接收系统的重要组成部分,用于正确指示有用信号到达,以保证系统在误码率较高的情况下有较高的正确接收概率,同时保证在噪声环境下有较低的虚警概率。

由于信号到达检测模块的运算量大,实时性要求高,所以通常在FPGA(Field Programmable Gate Array)芯片上实现,文中介绍了一种快速实现的方案,并且已经在Xilinx FPGA平台上验证

1 原理介绍

信号到达检测通常通过检测接收信号中包含的特殊信息来判断,为便于接收方使用相关的方式处理接收到的信号,发送方需要在真正有效的数据前添加特殊信息,设计中选用具有良好相关性的m序列作为PN码,如图1所示。

图1 数据帧结构

初始同步时,发送端将PN序列放在有用数据之前,作为信号的同步头;在接收端通过接收信号与已知PN序列进行相关运算,如果信号未到达,则PN码与噪声序列进行相关,得到的相关值较小;信号序列到达时,单径条件下,只有准确的接收位置,得到的相关值最大,而在多径条件下,在准确接收位置附近可达到最大的相关值,所以,可以通过设定一个阀值,初步判断信号是否已经达到。综上所述,好的信号达到检测算法,不仅在低信噪比条件下能准确检测出信号,且须具有较强的抗捕获能力,其关键点在于构建一组特殊的性能优良的PN码伪随机序列。

具体的算法判断标准主要体现在两个指标上,一是虚检概率,即数据信息未到达却被误认为已经到达的概率;另一个是漏检概率,即数据信息已经到达却误判断为未到达的概率。目标是通过使用多种算法的结合,保证虚检概率和漏检概率都尽可能低,为后端的信号处理达到预期的目标留出足够的余量。一次检测虚检概率和漏检概率分别设为pe和qe。假设一个检测消耗时间 T,则平均虚警时间为T/pe,LT时间内无虚警的概率为(1-pe)L;如果同步序列长为LT;则漏检概率为,所以pe要尽量小,qe可以略大点,通过多次检测,使得很小,在系统中,目标,则平均虚警时间为416 天;L=。假设检测算法由M个独立的算法组成,每个算法的虚警概率和漏检概率分别为pi、qi,则

本方案信号检测算法由相关/延迟相关判决法和PN判决法两个独立的算法构成,相关/延迟相关判决法是截取256个同步跳符号与后续256个同步跳符号进行共轭相乘并累加后取模得出一个值;同时窗口2自身模的平方的累加,如果信号到达,那么这两个结果应该基本相当。否则,噪声的能量与延迟相关值应该相差较大;PN判决法是取后窗口2本地的PN序列做循环相关累加,相关峰值与相隔32点的相关峰值进行对比,应该结果足够大。以上两个条件均要同时满足。对于第二门限的计算,可采用FFT与IFFT运算技巧,利用频域的乘法来取代时域卷积运算,从而可以大大减少运算量。

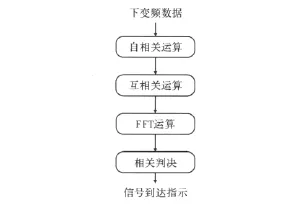

2 程序结构设计

信号到达检测模块的输入为收通路的下变频数据,由自相关运算、互相关运算、FFT运算和相关判决4个模块构成,输出信号到达检测指示信号,如图2所示。

图2 信号到达检测模块结构图

各个模块功能如下:

自相关模块,用于计算当前相关运算窗口的自相关值。

互相关模块,用于计算当前窗口与后续窗口之间的互相关值。

FFT运算模块,用于进行FFT运算与IFFT运算处理。

相关判决模块,根据自相关值,互相关值的运算结果进行判断是否检测到同步信号到达,并且有虚警保护设计。

3 实现方案

设计选用 Xilinx公司的 Virtex6系列 FPGA XC6VLX130T,Virtex6系列是Xilinx公司2009年推出的高端器件,带有丰富的逻辑资源,尤其有大量的乘法器和片内存储器,适用于复杂数字信号处理,资源如图 3所示[1]。

图3 Virtex6系列器件资源图

设计采用码长为255的PN码,FPGA的外部时钟为20 MHz,通过PLL进行5倍频变成100 MHz作为内部工作时钟,用于FPGA内部的高速处理。

为构造两个检测运算窗口,FPGA通过两级FIFO进行数据缓冲,如图4所示。

图4 FIFO结构示意图

下变频数据经过两级FIFO缓冲之后,FIFO中存储的数据就相当于两个运算窗口;自相关运算可以通过窗口2的数据进行运算完成;互相关运算可以通过窗口1和窗口2的数据进行运算完成。

相关运算本质上就是两个信号的卷积运算,其中自相关运算是指接收信号和自身的卷积运算,互相关运算是指接收信号和本地已知信号的卷积运算[2];根据傅里叶变换的原理,时域的卷积等价于频域的相乘;以256长度的PN码为例,时域的卷积需要作256次乘累加运算,但如果变换到频域,只需作2次傅里叶变换和1次乘法运算,可以节省大量的处理时间和硬件乘法器资源;实际上,傅里叶变换可以通过FFT模块快速实现,所以设计中的相关运算采用FFT运算实现。

4 程序设计仿真

设计使用Verilog硬件描述语言进行开发,系统关键变量如下:

clk100M:系统使用的全局时钟,速率100 MHz;

ddc_I:下变频数据输入的实部;

ddc_Q:下变频数据输入的虚部;

corr_self:自相关值计算输出;

corr_cross:互相关值计算输出;

pos_out:相关峰位置指示;

sdf:信号到达检测指示。

FPGA设计可以通过仿真软件进行先期验证以提高开发效率,仿真通过后再下载到FPGA芯片上进行验证。设计使用Mentor公司的Modelsim进行仿真,程序的整体设计仿真结果如图5所示。

图5 仿真结果图

下变频数据由同步跳和数据跳构成,可以看到,在接收到同步跳之后,sdf信号会出现高脉冲指示信号,在其他位置并不会出现这个高脉冲指示信号,同时还会给出相关峰出现的位置,从而达到信号到达检测的目的。

5 结束语

介绍了数字通信中采用的信号到达检测技术相关原理,并给出了在FPGA中实现的方案以及相关技巧。设计已经在Xilinx FPGA芯片上实现,并且应用于某高速数据传输系统上。通过人为加入噪声测试,实际应用环境测试等不同手段测试表明:介绍的信号到达检测模块满足系统的虚检概率和漏检概率指标要求,在实际应用中有一定的参考价值。

[1]Motorola.Virtex -6 Family Overview,Xilinx DS150[M].USA:Xilinx,2009.

[2]张玲玲,张怡,唐成凯.基于VHDL语言的扩频相关器设计与实现[J].航空计算技术,2008,38(5):103 -106.

[3]杜天艳,赵不贿.Petri网硬件实现简化方法研究[J].计算机仿真,2004(1):73-75.

[4]范海波.基于FPGA的线性卷积的实时实现[J].电子科技,2010,23(5):62 -66.

[5]魏西峰.全国步数字频率测量方法的研究[J].现代电子技术,2005(12):109 -110,113.

[6]雷能芳.基于DSP Builder数字信号处理器的FPGA设计[J].电子设计工程,2010(11):134 -136.

[7]杨宏,李国辉,刘立新.基于FPGA的CORDIC算法的实现[J].西安邮电学院学报,2008(1):81-83.

Design of Signal Arrival Detection Based on FPGA

GUO Yong

(Department of Ultrashort Waves,Guangzhou Haige Communications Group Incorporated Company,Guangzhou 510663,China)

The signal reaches the detection technology in digital communications.It has been implemented on a Xilinx FPGA chip and applied in a high-speed data transmission system.Different testing methods such as the artificial addition of noise and testing in practical applications show that the signal reaches the detection module and can fully meet the indicator of the virtual probability and missing probability.

signal detection;FPGA;digital communicatications

TN911.23

A

1007-7820(2012)08-041-03

2012-02-20

郭永(1979—),男,工程师。研究方向:高速数据传输。