通信系统中数字上变频技术的研究与设计

2012-03-17凌云志

铁 奎, 张 慷, 凌云志

(1.中国电子科技集团公司第四十一研究所 安徽 蚌埠 233006;2.中国电信上海公司 上海 200041)

通信系统中基带信号上变频的方式包括[1-2]模拟调制和数字调制,模拟调制中的基带和载波信号都是模拟信号。随着软件无线电技术的发展以及大规模集成电路和DSP的广泛应用,对通信系统中基带到中频的变换采用数字化处理,就能通过可编程器件的可编程性对载波频率、信号带宽、调制格式、信道编码等进行控制,实现不同的通信功能要求。运用这一思想对数字上变频器(DUC)进行研究与设计,对基带信号进行[3]成形滤波、内插、混频等处理,根据不同系统的要求,采用不同的编程代码来完成相应的功能,具有较强的可编辑性及灵活性。

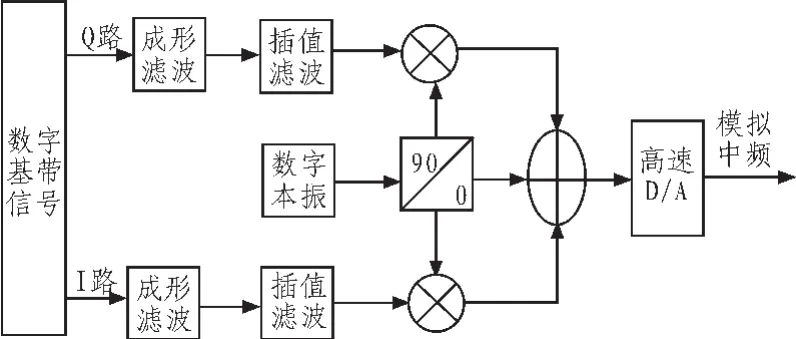

图1 数字上变频器原理Fig.1 Principle of digital up conversion

1 数字上变频技术的理论基础

数字上变频器的基本工作原理如图1所示,将基带信号通过脉冲成形滤波器进行带宽限制和消除码间干扰(ISI),然后通过插值滤波器提高采样率,最后与正交载波进行数字混频、合路到中频信号。

利用数字上变频技术可以完成矢量电压信号虚部和实部的叠加。设I路信号为A,Q路信号为B,数字本振(NCO)输出的基准信号样本为sin(ωcnT),输出与基准相位信号正交的样本为,则数字上混频之后的信号为:

由上可知,利用数字上变频技术可以替代传统模拟调制器的作用,实现实部和虚部的中频叠加。

数字上变频器的核心器件是插值滤波器和正交混频器。插值滤波器通过在原始的采样点之间重复样点然后经过半带滤波器或积分梳状滤波器 (CIC)滤波来提高信号的采样率,在频域内产生的镜像频谱,需要通过重建滤波器滤出。半带滤波器具有带内频响好的特点,由于是FIR结构并且每次滤波只能提高一倍的采样率,对于实现插值率较大的情况,设计复杂、浪费资源;CIC滤波器具有结构简单、插值率任意可变等优点,但带内频响不好;设计时可以考虑当插值率小时直接采用半带,插值率大时先经过半带提高采样率,然后再CIC滤波。因此插值器可以采用半带滤波和CIC滤波级联的结构。正交混频器可以用数字振荡器(NCO)、移位寄存器和乘法器设计。

2 半带插值滤波器的研究

FIR的全称叫有限冲击响应是数字滤波器的一种,其有着固定的硬件结构,主要由一些延时器、乘法器和加法器等组成,其频响的调整由滤波因子来控制。滤波因子的物理意义是滤波器频响在时域上的反映。FIR滤波器的硬件结构主要实现的是滤波因子与数字信号在时域上的卷积运算,在数学上时域的卷积就等于频域的乘积,这也就是FIR滤波的原理。只要将半带滤波因子导入FIR中,就可实现半带插值滤波器。半带滤波因子可以用函数计算或MATLAB仿真得到。

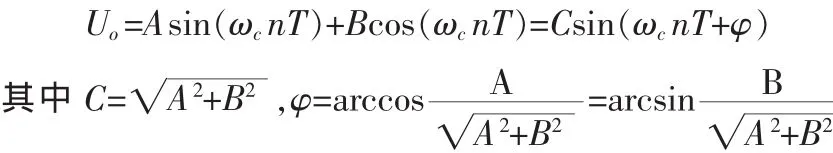

半带滤波器是一种FIR滤波器,它的冲击响应除了中心点不为零之外,在其他的偶数点全为零,所以用半带滤波器来实现插值滤波时,只需要一半的计算量,有很高的计算效率,可以节省硬件资源的开销。半带滤波器表达式为[4]:

由 z=ejω,也可以写为:

带内纹波和带外纹波相等,即δp=δs半带滤波器频谱特性如图2所示。

图2 半带滤波器频率响应Fig.2 Frequence response of half band filter

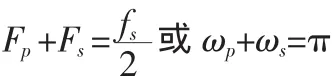

3 数字正交混频器的设计

数字正交混频器设计如图3所示,主要完成IQ矢量调制的功能,考虑到本振的正交性设计,可以将采样率设置为中频载波的 4×n 倍,n=1,2,3 ..., 这样两路相对有n个时钟延迟即可保证载波的正交性。信号频域的加性叠加在数学上可以表示为时域的乘法,因此混频器可以用乘法器替代。数字本振可以利用循环输出固定存储的采样点来表示。混频之后的合路器用加法器替代即可。乘法器、加法器都会造成数据位数的扩展,但D/A转换位数有限,因此需要对数据位数截短后输出。由于输入到正交混频器信号大小的不确定性,为了保证D/A输出后的信号有最大的动态范围,因此需要数据位数的截取段位能够动态调整。

图3 数字正交混频器设计Fig.3 Design of digital quadraturemixer

在实际电路的设计中,首先考虑的是中频频率及信号带宽,若中频信号频率为FC,信道带宽为B,那么采样率可设定为:

波形存储器中的样点数为4n个,正交相位本振相对基准相位本振延迟n个时钟周期。输入的基带信号的采样率为FS,经过插值率M=FS/Fb的半带滤波后,采样率与本振相同,基带信号与本振逐点相乘混频后再经过加法器合路即完成正交调制的过程。

4 仿真结果及分析

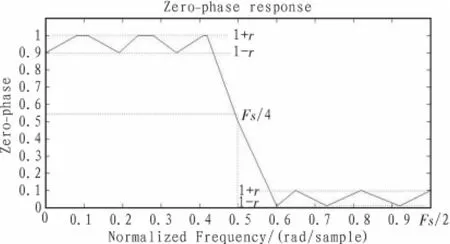

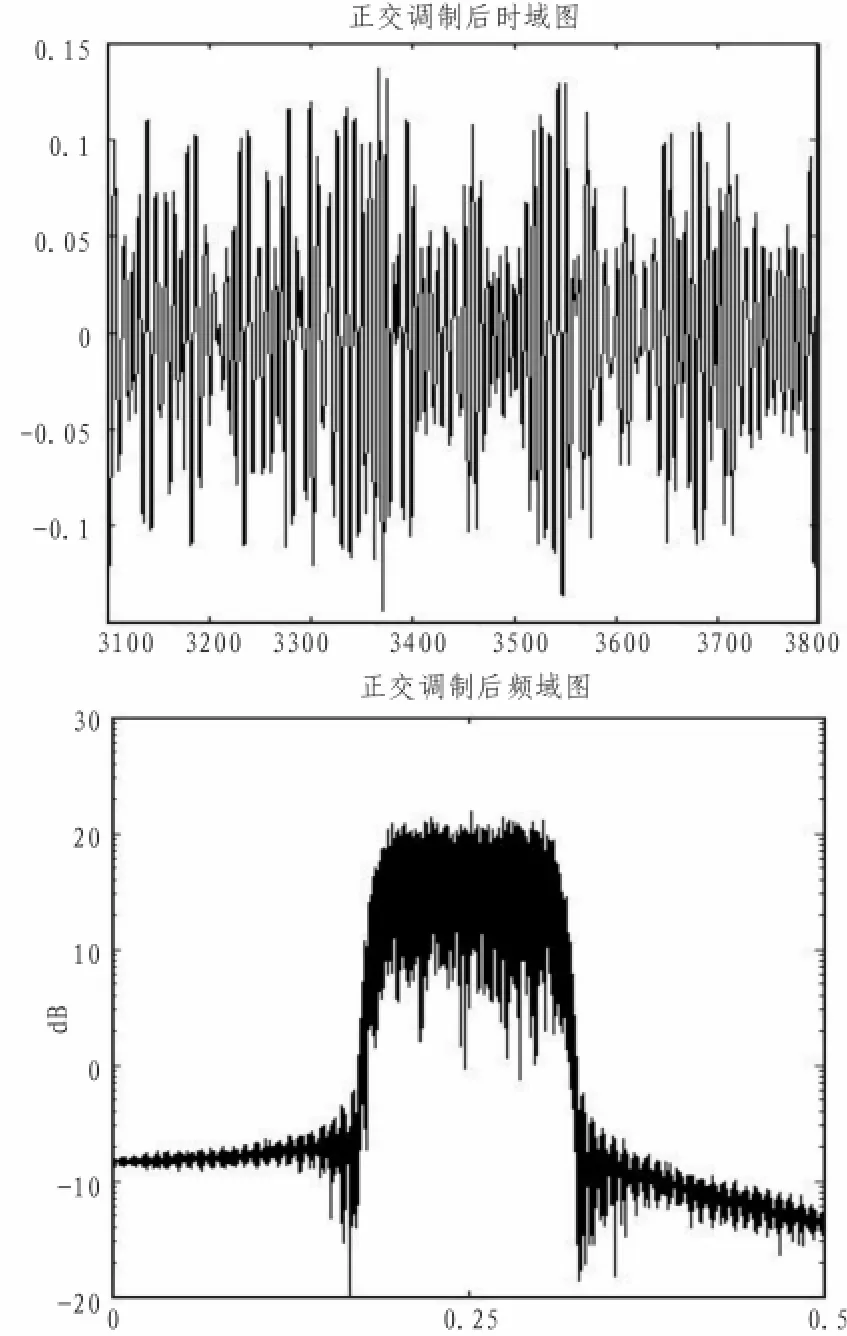

图4 正交调制后信号的时频仿真Fig.4 Time and spectrum simulation of quadraturemodulated signal

为了分析数字上变频技术的性能,采用MATLAB进行QPSK调制的仿真试验。仿真分析模型的主要步骤为:1)原始数据流用Randint函数产生随机二进制序列,长度为10000;2)根据QPSK星座图将数据流映射成对应的I、Q路幅度值,对应关系为 00(1,1);01(-1,1);10(-1,-1);11(1,-1)。 3)映射后的I、Q幅度值经过升余弦成形滤波进行符号间干扰和带宽限制,然后再通过半带滤波提高采样率,此时采样率变为码元速率的16倍,若采样率设为2,则I路基带信号带宽则为1/16。4)数字本振用函数 sin(nπ/4),n=1,2…8; 取 8 个点作为基本相位本振;延迟两个时钟周期的数据作为正交相位的本振,此时本振频率为1/4,将I路信号与基本相位本振逐点相乘,Q路信号与正交相位本振相乘,得到两路信号后再合路相加即完成数字正交调制,图4是正交调制后信号的时频仿真图,信号带宽为1/8。

5 结束语

数字上变频技术采用完全的数字化处理,无论是混频、移相、求和都可以精确的控制有利于调试及实验,可以避免模拟信号引入的噪声及幅度误差。并且数字信号处理过程中可以对数据流的任何阶段进行仿真和图形化显示便于排查问题。在实际设计过程中还可以增加校准电路对后端模拟通道的频响、群时延等误差进行预补偿,目前通信系统中基带信号正交调制到中频信号大都优先采用数字上变频技术。

[1]冯煦,钟卫.基于DDS的多调制功能正弦信号发生器[J].国外电子测量技术,2010,29(1):39-41.

FENG Xu,ZHONG Wei.Sinusoidal signal generator of multiple modulation function based on DDS[J].Foreign Electronic Measurement Technology,2010,29(1):39-41.

[2]段疑康.基于FPGA的伪随机序列发生器设计[J].电子元器件应用,2010,12(2):49-52.

DUAN Yi-kang.Design of paseudorandom sequence generator based on FPGA[J].Electronic Componet Application,2010,12(2):49-52.

[3]王方.基带成形滤波器的设计[J].无线电通信技术,2000(26):5-7.

WANG Fang.Design of baseband shaped filter[J].Wireless Communication Technology,2000(26):5-7.

[4]文峰,石峰.基于FPGA的高速数据采集系统设计[J].研究与开发,2008,27(7):32-35.

WEN Feng,SHI Feng.System design of high speed data collection based on FPGA[J].Research and Development,2008,27(7):32-35.

[5]刘敏.基于软件无线电的π/4-QPSK与GMSK调制系统实现[J].南京航空航天大学学报,2003(11):33-36.

LIU Min.π/4-QPSK and GMSK modulation based on software radio system[J].Journal of Nanjing University of Aeronautics & Astronautics,2003(11):33-36.

[6]HU Xiao-bo,Harber R G,Bass SC.Expanding the range of convergence of the CORDIC algorithm[J].IEEE Trans.on Computers,1991,40(1):13-20.

[7]田耘,徐文泼,张延伟.数字信号处理的FPGA实现[M].北京:电子工业出版社,2008.