基于旁路分析的硬件木马检测方法*

2012-03-15王力纬罗宏伟姚若河

王力纬 罗宏伟 姚若河

(1.华南理工大学电子与信息学院,广东广州510640; 2.工业和信息化部电子第五研究所电子元器件可靠性物理及其应用技术重点实验室,广东广州510610)

对于应用于航空电子、金融、交通等安全敏感系统中的集成电路(IC)芯片,需要特别关注其可靠性、安全性和可信度.但集成电路产业的全球化趋势,使得IC芯片的设计与制造过程相分离,导致IC芯片在外包制造过程中存在风险:部分不可信的制造商可能更改IC芯片的原始设计(如修改掩模板),嵌入所谓的硬件木马(Hardware Trojan)电路;这些电路能在特定的触发条件下被激活,从而泄漏芯片内部的敏感信息或扰乱芯片的原始功能,使整个系统失效.由于硬件木马的潜在危害巨大,而且采用传统的测试技术难以检测,因此,硬件木马被认为是对集成电路安全性的一个重大威胁[1-3].

近年来,人们对硬件木马进行了大量研究,取得了许多成果.文献[4]从硬件木马的物理特征、激活机制和激活后的行为3个方面对硬件木马进行了分类.文献[5]在此基础上进行了扩充,提出了一种更完善的分类方法.文献[6]基于硬件木马的触发机制和载荷类型提出了不同的分类方法.

对于现有的多种不同类型的硬件木马[7],目前还缺少评估各种木马检测方法有效性的准则.用于检测木马的旁路信号包括时序信号和功耗信号.文献[8]中提出了采用电路的功耗信号来检测硬件木马的方法.此外,通过测量芯片电源端的瞬态电流信号,再对这些信号进行电流集成化分析[9]或基于区域的分析[10],可以有效地检测出小规模的硬件木马.文献[11]中提出了一种基于时延的物理不可克隆功能(PUF)的电路结构,该结构能在芯片的测试阶段辅助检测硬件木马.文献[12]中提出了一种基于全芯片的路径时延信息的指纹生成新方法,该方法通过分析硬件木马对芯片时延信息的影响,从而发现那些面积很小的硬件木马电路结构.

尽管已经有了上述诸多研究成果,但在硬件木马检测领域仍然存在改进的空间.首先,现有的绝大多数关于硬件木马检测的研究成果都采用不可综合的电路作为基准电路,如ISCAS’85、ISCAS’89和MCNC’91等.这些基准电路最初用于评价测试向量检测芯片缺陷的能力,不适合用于验证硬件木马的检测方法,因此那些具有特定功能的可综合电路,如加密电路(DES、AES、RSA等)将是更好的选择.其次,现有的绝大多数检测方法都是采用仿真结果进行验证,而硬件木马是对原始芯片设计的硬件进行的修改,因此检测方法的硬件验证(在FPGA或ASIC上的实测验证)是极为必要的.为此,文中提出了一种基于旁路分析的硬件木马检测方法,并在FPGA芯片上将一个可综合的64位DES加密电路作为基准电路加以实现,最终完成该木马检测方法的硬件验证.

1 硬件木马检测原理及流程

1.1 检测原理

硬件木马的激活条件常被称为木马的“触发”部分,原始设计中由于硬件木马被激活而受到影响的那部分电路或功能则被称为木马的“载荷”部分.一种典型的时序触发型硬件木马的电路结构[6]如图1所示.原始设计中逻辑节点(ER)与被修改后的逻辑节点(ER*)是直接相连的,但由于被嵌入了硬件木马,导致实际上它们之间的连接存在一个异或门.该硬件木马的“触发”部分是一个K位的同步计数器,当计数器的值被计满时,通过木马的“载荷”部分(一个异或门)将ER处的逻辑值反向形成ER*,从而引发了一个错误操作.由于这种木马结构典型、实现简便,因此文中采用这种硬件木马电路进行实验.

图1 一种典型的时序触发型硬件木马的电路结构[6]Fig.1 Circuit structure of a typical sequentially-triggered hardware Trojan

从现有的研究成果来看,旁路分析技术因其具有的非破坏性、较高的检测分辨率和低实施成本而被认为是目前最具前景的硬件木马检测技术,文中提出的硬件木马检测方法也是基于旁路分析的.旁路分析是指对集成电路芯片的旁路信号进行分析.旁路信号是与芯片管脚上的输入/输出信号相对的一个概念,后者被称为主信号.常见的旁路信号包括芯片的功耗、电路的时序(延迟)信息、电磁辐射信号、热信号、瞬态电源电流等,文中选择旁路信号中的功耗信息作为分析的对象.

文中基于旁路分析的硬件木马检测方法的基本原理是:当电路处于工作状态时,任何电路结构都会消耗能量,芯片中嵌入的硬件木马也不例外.因此,有木马的芯片与无木马的芯片在相同输入测试向量的激励下,虽然运行的操作是一样的,但硬件木马的存在会导致它们功耗的瞬态变化有细微的差别.木马电路的规模越大,这种差别就越大.因此,通过比较待测芯片与无木马芯片之间的功耗瞬态变化,就能判断待测芯片中是否存在硬件木马.

1.2 检测流程

文中检测方法基于如下假设:能获得N个已确认无硬件木马存在的集成电路芯片.在该假设下,文中研究的硬件木马检测问题可描述为:给定N个无硬件木马的集成电路芯片(I1,I2,…,IN)及一个可疑的芯片IN+1,如何判断芯片IN+1中是否包含硬件木马?

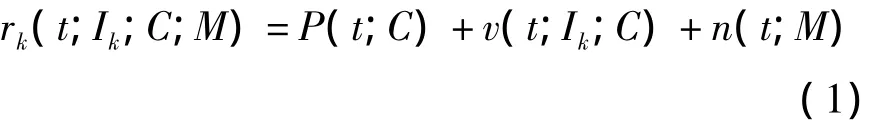

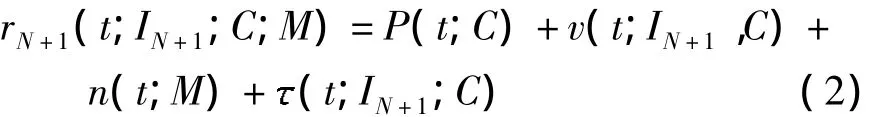

为了解决这个问题,首先需要对芯片的功耗进行分析.以无硬件木马的集成电路芯片Ik(k=1,2,…,N)为例,在其执行运算操作C时,可以进行一次芯片瞬时功耗的测量M.这次功耗测量过程所获得的功耗rk(t;Ik;C;M)可分解为3个部分:

式中:t为时间;P(t;C)为平均功耗,它是对所有无木马的集成电路芯片Ik(k=1,2,…,N)都多次执行运算操作C,并多次测量瞬时功耗信息,再对所有这些测量值取平均而得到的;v(t;Ik;C)为工艺噪声,由于芯片制造过程中工艺参数存在一定程度上的波动,导致即使是同一批次的芯片,在执行相同运行操作时,其功耗也会存在细微的差别,这一差别可用v(t;Ik;C)来表征,它是与芯片Ik及芯片所执行的运算操作C相关的;n(t;M)为测量噪声,仅与时间和测量次数相关.

假如芯片IN+1中被嵌入了硬件木马,那么它的功耗可表征为

一般来说,测量噪声n(t;M)是一个随机噪声,它随着每一次测量过程而发生变化.由于功耗各组成部分中仅有测量噪声n(t;M)与测量次数相关,因此,可以通过对同一个芯片进行多次功耗测量再取平均来消除该测量噪声.工艺噪声v(t;Ik;C)本质上是不同芯片所体现出来的功耗差异,因此可以通过对N个无木马芯片的功耗测量数据取平均来消除.根据式(1),通过上述两次平均运算,从无硬件木马的集成电路芯片Ik(k=1,2,…,N)的功耗测量数据中消除工艺噪声和测量噪声后,可得到最终的平均功耗P(t;C).根据式(1)和(2),由于平均功耗是无木马芯片和有木马芯片的功耗测量数据的共同部分,因此也可以把它从所有功耗测量结果中减去,从而得到

故文中研究的硬件木马检测问题可看成是一个信号特征化的问题:根据式(3),计算出所有无木马芯片的rk(t;Ik;C)后,对其进行特征化,得到工艺噪声v(t;Ik;C)的特征;然后根据式(4)计算出可疑芯片的rN+1(t;IN+1;C),并将其特征与工艺噪声v(t;Ik;C)的特征进行比较,检查两者的特征是否一致.如果特征一致,则表明芯片IN+1中不存在硬件木马;反之,则表明芯片IN+1中存在硬件木马.

综上所述,在可获得N个无硬件木马的集成电路芯片(I1,I2,…,IN)及一个可疑芯片IN+1的前提下,基于旁路分析的硬件木马检测方法的步骤如下:

(1)对每个无硬件木马的集成电路芯片(I1,I2,…,IN)施加测试向量VT,使芯片执行运算操作C,测量收集芯片的瞬时功耗信息L次,采集得到无硬件木马芯片的L×N条功耗曲线;

(2)对可疑芯片IN+1施加测试向量VT,使它执行与无木马芯片相同的运算操作C,测量收集其瞬时功耗信息L次,采集得到可疑芯片的L条功耗曲线;

(3)计算每个芯片的L条功耗曲线的平均值,以消除测量噪声的影响;

(4)为消除工艺噪声,计算步骤(3)中得到的N条无硬件木马芯片的平均功耗曲线的平均值,得到P(t;C);

(5)根据式(3)、(4)计算各个芯片的功耗;

(6)利用奇异值分解算法[13]对无木马芯片(I1,I2,…,IN)的功耗波形数据进行分析,获得子空间S,并将这些功耗波形数据投影到该子空间上;

(7)将可疑芯片IN+1的功耗波形数据投影到子空间S上;

(8)比较步骤(6)和(7)中得到的投影值的特征,如果两者的特征一致,则表明可疑芯片IN+1中不存在硬件木马,反之则存在硬件木马.

2 硬件木马检测实验

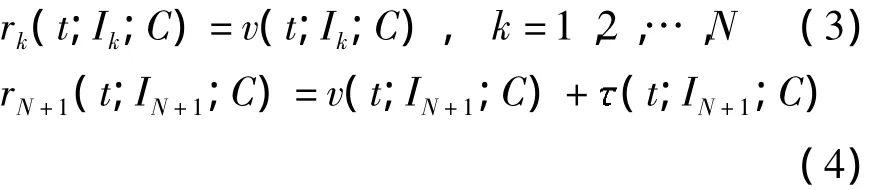

为验证所提出的硬件木马检测方法的有效性,文中搭建了一个FPGA实验平台,其原理框图如图2所示.该平台中的FPGA芯片选用Xilinx公司的Spartan-3E XC3S500E系列FPGA芯片(采用90nm CMOS工艺制造),用于模拟真实的ASIC器件.

图2 FPGA实验平台的原理框图Fig.2 Principal block diagram of FPGA experimental platform

如图2所示,该实验平台中有两块FPGA芯片: (1)待测FPGA,用于模拟无硬件木马和有硬件木马的芯片;(2)测试图形生成FPGA,主要负责给待测FPGA施加测试向量,并对待测FPGA的响应信号进行校验.直流稳压电源通过精密电阻给待测FPGA的内核电源端提供电压.示波器用于测量精密电阻两端的压降,通过计算可得到待测FPGA芯片的瞬时功耗情况.在计算机上用Matlab编程实现相关信号处理算法,用于检测硬件木马.

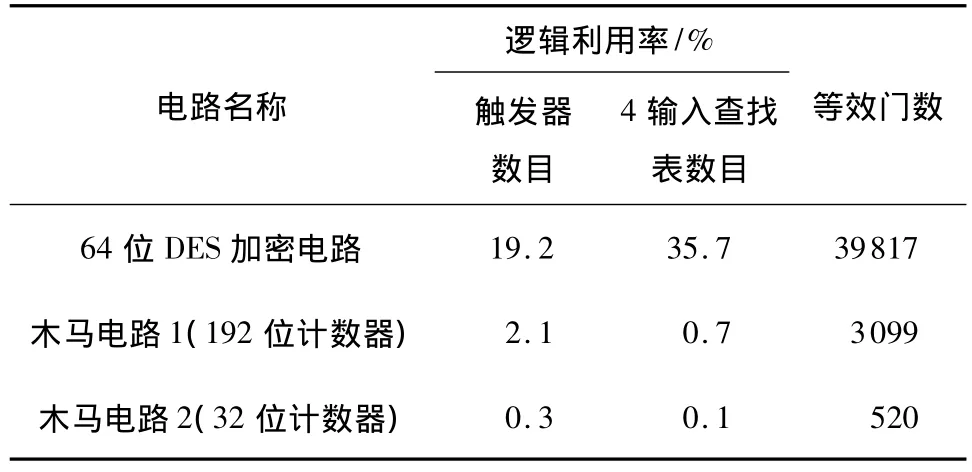

在实验中,采用64位DES加密电路作为基准电路,并设计两种不同面积的硬件木马电路(其电路结构如图1所示).表1给出了基准电路与两种硬件木马电路在FPGA芯片中的逻辑利用情况,可以看出,木马电路1和2的面积分别为64位DES加密电路面积的7.8%和1.3%.

表1 基准电路与两种硬件木马电路的逻辑利用率比较Table 1 Comparision of logic utilization among benchmark circuit and two hardware Trojan circuits

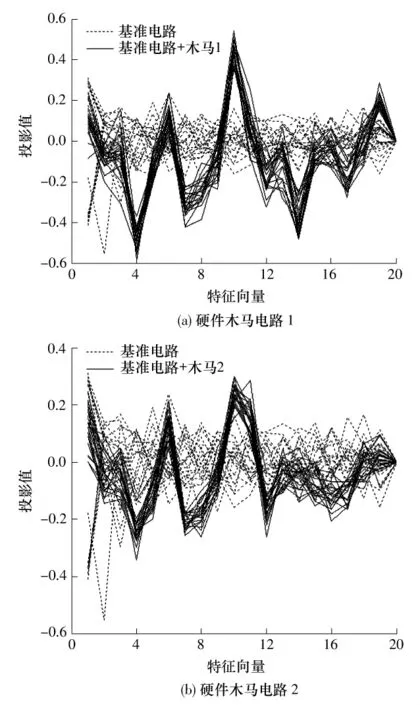

为了对工艺噪声进行建模,共使用20块同型号的待测FPGA芯片进行实验,将3种电路(64位DES加密电路、嵌入了硬件木马1的64位DES加密电路、嵌入了硬件木马2的64位DES加密电路)实现在每块待测FPGA芯片上.对每一块待测FPGA芯片上实现的每一种电路,采样100条功耗曲线,每条功耗曲线共采样10000个点,然后利用文中检测方法对这些功耗曲线进行处理与分析,最终得到3种电路的功耗曲线在子空间上的投影值,如图3所示.从图3可以看出,随着特征向量的增大,基准电路的投影值的均值和方差越来越趋近于0,但嵌入了硬件木马电路的投影值的均值并未趋近于0,且投影值的变化较为剧烈(即方差较大),这表明有硬件木马的FPGA芯片和无硬件木马的FPGA芯片,其功耗曲线在子空间上投影值的特征是很不相同的,这与文献[8]中的描述相符.

从每条功耗曲线中截取了2000个连续采样点进行分析,结果表明,基准电路与嵌入了硬件木马1的电路相比,其功耗曲线的投影值在特征向量4、7、8、10、和14处具有完全不同的特性,如图3(a)所示,这有助于检测出硬件木马1.同样截取了每条功耗曲线的2000个连续采样点进行分析,由于硬件木马2的面积比硬件木马1小,导致了基准电路与嵌入了硬件木马2的电路相比,其功耗曲线的投影值的差别并不如图3(a)中那么大.可以预见,当硬件木马的面积越来越小并达到某个临界值后,就不能区分两个投影值的差别了.在图3(b)中,虽然硬件木马2的面积只占原始设计电路的1.3%,但仍然可以发现,有木马电路和无木马电路的功耗曲线投影值在特征向量4、8和10处具有不同的特性,从而有助于把存在硬件木马2的芯片从无木马的芯片中区分开来.

图3 两种硬件木马电路的检测实验结果Fig.3 Experimental detection results of two hardware Trojan circuits

3 结语

文中提出了一种基于旁路分析的硬件木马检测方法,该方法具有非破坏性、实施开销小等优点.为验证该方法的有效性,在基于90 nm工艺的FPGA芯片上搭建了一个实验平台,对该硬件木马检测方法进行了硬件验证.实验结果表明,即使在测量噪声和工艺噪声较大的环境中,利用文中检测方法对FPGA芯片的功耗测量数据进行统计分析后,其硬件木马的检测分辨率也能达到10-2,即能检测出芯片中面积比原始设计电路小2个数量级的硬件木马.为继续提高硬件木马检测的分辨率,今后将研究开发定制化的测试向量,以便最大可能地激活硬件木马,辅助木马电路的检测;同时探讨比文中采用的奇异值分解算法更适用的信号处理技术,并评估这些技术应用于硬件木马检测时的效率.

[1] DARPA.Trust in integrated circuits-proposer information pamphlet[EB/OL].(2007-07-24)[2011-08-11].http:∥www.darpa.mil/MTO/solicitations/baa07-24/index.html.

[2] Defense Science Board.High performance microchip supply[EB/OL].(2005-02-21)[2011-08-11].http:∥www.acq.osd.mil/dsb/reports/2005-02-HPMS_Report_ Final.pdf.

[3] Adee S.The hunt for the kill switch[J].IEEE Spectrum,2008,45(5):34-39.

[4] Wang X,Tehranipoor M,Plusquellic J.Detecting malicious inclusions in secure hardware:challenges and solutions[C]∥Proceedings of IEEE International Workshop on Hardware-Oriented Security and Trust.Anaheim:IEEE,2008:15-19.

[5] Tehranipoor M,Koushanfar F.A survey of hardware Trojan taxonomy and detection[J].IEEE Design and Test of Computers,2010,2(1):10-25.

[6] Chakraborty R,Narasimhan S,Bhunia S.Hardware Trojan:threats and emerging solutions[C]∥Proceedings of IEEE International High Level Design Validation and Test Workshop.San Francisco:IEEE,2009:166-171.

[7] Jin Y,Kupp N,Makris Y.Experiences in hardware Trojan design and implementation[C]∥Proceedings of IEEE International Workshop on Hardware-Oriented Security and Trust.Francisco:IEEE,2009:50-57.

[8] Agrawal D.Trojan detection using IC fingerprinting[C]∥Proceedings of IEEE Symposium on Security and Privacy.Berkeley:IEEE,2007:296-310.

[9] Wang Xiaoxiao,Salmani H,Tehranipoor M,et al.Hardware Trojan detection and isolation using current integration and localized current analysis[C]∥Proceedings of IEEE International Symposium on Defect and Fault Tolerance of VLSI Systems.Boston:IEEE,2008:87-95.

[10] Rad R M,Wang Xiaoxiao,Tehranipoor M,et al.Power supply signal calibration techniques for improving detection resolution to hardware Trojans[C]∥Proceedings of IEEE/ACM International Conference on Computer-Aided Design.San Jose:IEEE,2008:632-639.

[11] Li J,Lach J.At-speed delay characterization for IC authentication and Trojan horse detection[C]∥Proceedings of IEEE International Workshop on Hardware-Oriented Security and Trust.Anaheim:IEEE,2008:8-14.

[12] Jin Y,Makris Y.Hardware Trojan detection using path delay fingerprint[C]∥Proceedings of IEEE International Workshop on Hardware-Oriented Security and Trust.Anaheim:IEEE,2008:51-57.

[13] Theodoridis S,Koutroumbas K.Pattern recognition[M].4th ed.San Diego:Elsevier,2009:335-341.