基于FPGA的高速采样单元实现

2012-01-19王健

王 健

(1.西安电子科技大学通信工程学院,陕西西安710071;2.河北远东通信系统工程有限公司产品制造部,河北石家庄 050081)

基于FPGA的高速采样单元实现

王 健1,2

(1.西安电子科技大学通信工程学院,陕西西安710071;2.河北远东通信系统工程有限公司产品制造部,河北石家庄 050081)

介绍了一种基于FPGA的高速采样单元硬件实现,包括数据采集器周边电路设计、高速数据传输方法和设计要点、运算处理单元设计、总线控制设计和VHDL程序编写框架。将信号进行样式转换,由采样器转换并通过可编程门阵列FPGA进行处理并存储,再由系统进行控制完成整个采样单元的数据传输。

数据采集器;FPGA;VHDL;DSP

针对基于某电磁环境的模拟设备,该设备通过使用多个高速采样单元,圆满完成了系统对某些信号的实时采集、处理。由于该采样单元具有的稳定性高、采样指标好等特点,相继应用于多个系统中,完成了不同系统对数据采集处理的要求。

设计选用10 bit最高达1.5 Gsample/s的高速采样器进行数据采集,其动态可达50 dBc;该环境模拟系统采用3块高速采样单元完成整体信号同步采集工作。模拟信号在数字板卡上的传输是该板卡的设计难点,该高速采样单元使用差分信号输入采样器来实现信号的高速、抗干扰传输。运算单元的加入使该板卡能够完成一定的数据运算。

1 高速采样单元系统构成

高速采样单元由采样、数据处理、高速数据传输、运算和传输控制系统组成。采样系统由射频转换系统、采样器、外围控制电路组成。数据处理系统由可编程门阵列FPGA和其外围电路组成。高速数据传输系统由两片FPGA用LVDS差分信号完成数据的高速传输。运算系统由DSP芯片和外围控制电路组成。传输控制电路由FPGA和计算机总线接口电路组成。

1.1 主要芯片选择

1.1.1 采样器芯片AT84AS003

采样芯片选取Analog Device公司的AT84AS003,该芯片采样率最可达1.5 Gsample/s、采样位宽10 bit;动态范围达52 dBc;4路10位LVDS差分信号输出;每一路有单独时钟配合。该芯片供电电压分模拟(-5 V,3.3 V,-2.2 V)和数字供电(3.3 V,2.5 V)。高速度、高精度、高稳定性是本方案选用其作为数据采集系统采样器的主要原因。

1.1.2 数据处理器

美国Xilinx公司的Virtex-5系列芯片,该系列芯片相比上一代优化了串行I/O的高性能逻辑部分;其提供的RocketIO 收发器能提供100 Mbit·s-1~3.2 Gbit·s-1的高速串行连接器和最高到1.25 Gbit·s-1的LVDS差分信号;65 nm的工艺保证其可集成更多的逻辑门,降低芯片的整体功耗;更低的核压(1.0 V)保证其功耗相对上一代有大幅度降低。

1.1.3 运算处理器

运算处理器选用美国TI公司的TMS320C6713处理器;该运算处理器可以在225 MHz的工作频率下提供每秒百万浮点运算,2级缓存构架能够支持强劲多样的外部设备;一级缓存分4 kB程序缓存和4 kB数据缓存,二级缓存是一个256 kB共享缓存;丰富的外设接口是选其作为运算处理的重要原因之一,其端口包括2个多声道音频串行端口,两个多通道缓冲串行端口,一个专用输入输出模块和外部存储接口无缝连接SDRAM。

1.1.4 数据传输

和计算机的数据传输选用PCI总线传输方式进行,其选用的芯片为PLX9054,该芯片为一款32 bit 33 MHz的总线接口芯片,突发传输速率可达132 MByte·s-1。双DMA通道是本方案选用其作为数据传输,系统控制的主要原因。

1.2 整体电路设计

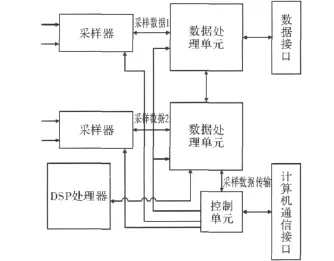

1.2.1 信号流程图

图1 信号流程图

该高速采样单元由系统提供采样时钟和信号,2路时钟、2路信号完成单板1.5 Gsample/s同步采样。数据处理单元完成对信号的FFT运算和存储,通过两个FPGA之间的高速数据传输,可实现单板的数据综合处理,DSP处理器可根据系统指令完成数据的运算;PCI总线接口传输信号和采样数据,完成系统对板卡的功能要求。

1.2.2 硬件设计

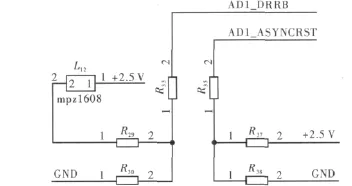

该板卡选用两路采样器,通过数据接口控制实现同步采样;对于该板卡的控制可由预置好的控制单元进行控制,也可通过计算机PCI总线进行控制;该控制单元可实现数据的DMA传输;采样模式控制,使采样器工作在不同的模式下,采样器有如下控制端口:BIST:自动检测功能,10 kΩ电阻接地;ASYNRST:同步复位,需配合DRRB,2条件需要连接到FPGA以便实现复位需求,线要等长。上拉和下拉电阻要尽量靠近采样器,连接方式如图2所示;PGEB:采样器样式控制器,0 Ω电阻接-5 V;SDA:采样延时调整控制,10 kΩ电阻接地;GA:采样增益调整;B/BG:0 Ω电阻接-5 V;SLEEP:10 kΩ电阻接地;STAGG:输出模式选择,10 kΩ电阻接地。

图2 上拉和下拉电阻连接方式

通过图2电路,可实现多个采样器的同步工作,拓展了采样的精度,完成该系统对实时环境信号的采集工作;该设计要点在同步控制上,2个复位信号的电压有电阻进行匹配,通过FPGA控制。数据输出要等长,如果选用多个采样器进行采样,需要所有输出信号线等长。

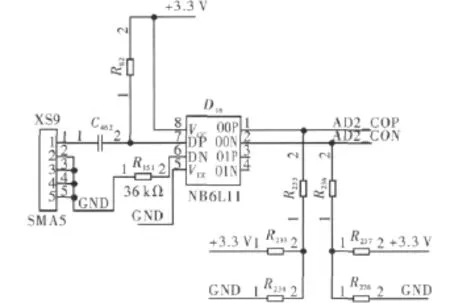

采样器时钟的输入决定了该采样器的工作频率(150 Msample/s~1.5 Gsample/s)。对于采样器信号和时钟的选择方式上,选用模拟转差分电路进行匹配,既不影响数字信号,也提高了高频信号在数字板的稳定度;时钟设计电路如图3所示。

图3 时钟设计电路

采样器工作前要给一个复位信号。在相关电路匹配正常情况下完成采样。采样器正常工作应注意以下几点:(1)选用3种模拟电压进行供电,分别为-5 V、-2.2 V、3.3 V;其中 -5 V工作电流在 660 mA、-2.2 V工作在200 mA、3.3 V工作在100 mA。(2)较高的功率造成该芯片有高发热量,需要大功率散热器或整体散热器对其进行散热。(3)为了防止信号的干扰,采样板选用分割地的方式对板卡进行布局,AGND和GND要有多个点进行连接,既保证了地的隔离又不影响地的相对电压值。

存储器部分是决定存储采样时间的模块,由于FPGA内部集成的RAM不能长时间的存储数据,为快速长时间的存储数据,需要扩展外部存储空间,方案选择了DDR2颗粒(MT47H128M16)作为该部件的扩展存储单元:A<0:15>地址和BA<0:2>接上拉电阻;DATA<0:15>串联电阻进行匹配阻抗连接到FPGA;控制管脚 CAS、RAS、WE、CS接上拉电阻;DQS、CK 要以差分对形式接入FPGA,其中DQS要求接到FPGA的局域时钟上,时钟CK要求接上拉电阻CKE和ODT信号要接下拉电阻。同样的连接方式可以扩展多片存储器,对于数据要求每片单独放在一个bank里,如果放不下可以放在2个bank里,但要求DQS信号和数据在一个bank里面。

图4 存储模块

数据处理单元是对采样器传输过来的离散数字信号进行处理,在FPGA对采样器送来的信号进行FFT运算,程序首先将采样器转换的差分信号在FPGA内部转换为单端信号,然后通过IDDR把信号转换成SDR模式的信号方便处理,最后用FPGA进行FFT处理并存储备用。

处理器采用并行数据传输,由于2片FPGA紧邻摆放,可以实现高位宽、高速度的数据传输,该采样单元设计成64 bit的数据、2路全局时钟来完成数据的高速传输。为保证传输速度稳定快速,这64对LVDS信号差分线要实行等长处理,每8 bit一组,每组的两端要保证在一个bank里面,如想分位控制,可以实现每组配备2个时钟信号分别进2个FPGA的CC管脚上。整体在2对信号分别接在2个FPGA的GC管脚上。每对差分线在其信号输入端要接100 Ω的匹配阻抗。在完成以上的硬件设计之后2个FPGA可实现高速数据传输。

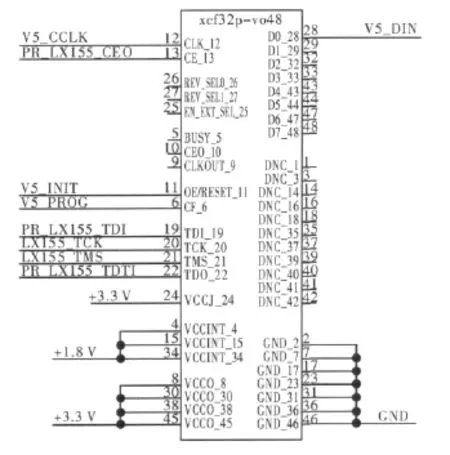

板卡的FPGA配置电路设计,可由第3片控制芯片完成,方案采用总线加载方式进行配置设计,其配置管脚如图4所示,M0、M1、M2为控制加载方式的管脚,其配置为1-1-0。

由1 400 AN控制2片V5的FPGA加载,可根据自己的需求来配置M0-2实现不同的加载方式。文中采样程序固化到PROM里,实现上电加载程序。配合V5系列的FPGA外接PROM选用XCF32PVOG48C。

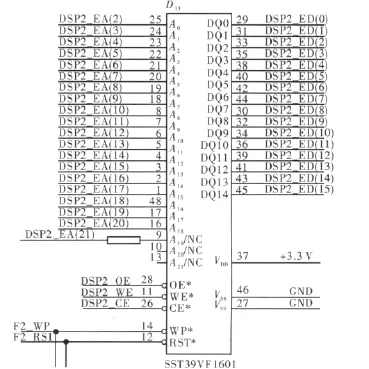

DSP设计上选用TMS320C6713连接一片FPGA进行数据运算;DSP外接一片MT48LC4M32芯片作为外接存储单元其原件如图5所示。32位数据和总线要DSP、FPGA共用,设计时注意总线上匹配的排阻要靠近DSP端,排阻要保持一定距离以便后期调试,检测电路是使用复位电路设计选用板载开关接上拉(3.3 V)电阻进行控制,同时要把该复位端口也连接到FPGA上,方便系统对其进行控制,Flash的地址端A<0:19>连接到总线地址的<2:21>。Flash的数据位D<0:16>连接到DSP数据总线的低16位上,其余控制端OE、WE、CE、WP、RST按数据手册连接到DSP的专用控制管脚上,来实现自动加载程序。

图5 外接存储单元

3 结束语

采样器的选择直接关系到整个板卡的信号采集效果,同步功能是该板卡的特点之一,通过板间同步的LVDS差分信号,可实现块板卡同步采样,为后续数字处理提供更多的信息,板载DSP处理器可单独完成对信号的处理。该采样器具备了高速、高位宽等特点,可完全胜任模拟信号的数字化处理。实际制作中3块该板卡可实现6个采样器同步采样,有效快速地响应系统要求。

[1]侯伯亨,顾新.VHDL硬件描述语言与数字逻辑电路设计[M].西安:西安电子科技大学出版社,2006.

[2]胡广书.数字信号处理[M].2版.北京:清华大学出版社,2003.

[3]樊昌信,张甫翊,徐炳祥,等.通信原理[M].5版.北京:国防工业出版社,2007.

[4]王超,黄显高.高速数据采集系统的电源设计[J].西安邮电学院学报,2009(9):55-58.

Implementation of Signal Sampling with FPGA

WANG Jian1,2

(1.School of Telecommunications Engineering,Xidian University,Xi'an 710071,China;2.Manufacturing Division ,54 Institute of China Electronics Technology Group Corporation,Shijiazhuang 050081,China)

A high-speed sampling unit hardware realization based on FPGA is proposed,including the circuit design of data acquisition;the approach of high speed data transmission;the design of operational processor system and bus control system,and the VHDL program framework.The signal types are transformed by the sampler and then processed and stored with programmable gate arrays FPGA.Finally,the data of the sample unit is transmitted under the control of the whole system.

data acquisition;FPGA;VHDL;DSP

TP274+.2

A

1007-7820(2012)08-049-04

2012-03-25

王健(1982—),男,助理工程师。研究方向:军用电子技术。