基于DSP的多通道弹载数据记录仪的设计*

2011-12-07杜力力李永红

王 琦,杜力力,李永红

(中北大学信息与通信工程学院,太原 030051)

0 引言

为适应信息化战争要求,常规弹药的信息化、制导化已作为武器装备信息化的重要组成部分,制导炮弹与常规炮弹的主要差别是弹丸上装有制导系统和可供驱动的弹翼或尾舵等空气动力装置。文中是利用弹载数据记录仪具有的体积微小、抗高冲击过载能力、微小功耗、测试精度高等特点,实现了对于短程制导兵器研制中动态参数的实时测试记录。

设计以DSP为主控单元,能够实现20路模拟信号,10路 TT L信号及一路232信号的实时采样,采样频率的选择由硬件实现,可实现多种采样频率选择。对模拟信号的采样由DSP内部12位ADC完成,产生的数据将保存在FLASH存储器中并在回收后由通信模块发给上位机。由于采用了FLASH存储器,因此无需备用电源。系统采用整体结构化设计,体积小、抗冲击过载能力强。系统在要求的环境下均能准确记录炮弹内的信号,为分析炮弹的飞行参数和故障的定位起到了重要作用。

1 系统整体结构

1.1 系统框图设计

系统整体框图如图1所示。由图1可知,整个系统主要由主控模块、数据存储模块、采样时序控制模块、通信模块组成。

图1 系统整体框图

1.2 系统工作原理

系统在上电后将在主控模块的控制下首先进行各功能模块的配置,在各功能配置完成之后,将进入待触发状态,整个采集过程将由触发信号启动。采集启动后,各通道的模拟信号在模拟开关的控制下将以时序发生器要求的频率经过信号调理后进入DSP内部ADC,经过AD转换的数据将和 TT L信号以及232信号一同被储存在数据存储模块中。数据在系统回收后经通信模块发至PC机进行处理。

2 系统各模块设计

2.1 主控逻辑模块

控制逻辑由32位微处理器和接口部分组成,完成对信号采样时序控制模块、数据存储模块和通信模块的控制。主控制器件由TI公司的带12位ADC的32位微处理器DSP构成,32位的DSP整合了DSP和微控制器的最佳特性[1],可以很好的完成整个测试系统的各项要求。整个采集过程中,包含两种中断,即ADC中断和串口接收中断,数据的采集及编码即是在DSP中断中实现的。

系统时钟的高低决定了记录仪功耗的大小,因此在允许的情况下要尽可能的降低DSP主时钟频率。本设计中对系统时钟要求最苛刻的地方就是对FLASH写操作,因为FLASH的写操作是以页为单位,写一页的时间为ms数量级,在采用乒乓操作的情况下,经过反复实验后,选定DSP主时钟频率为40M,这样整个系统工作的最高功耗控制在140mA左右。

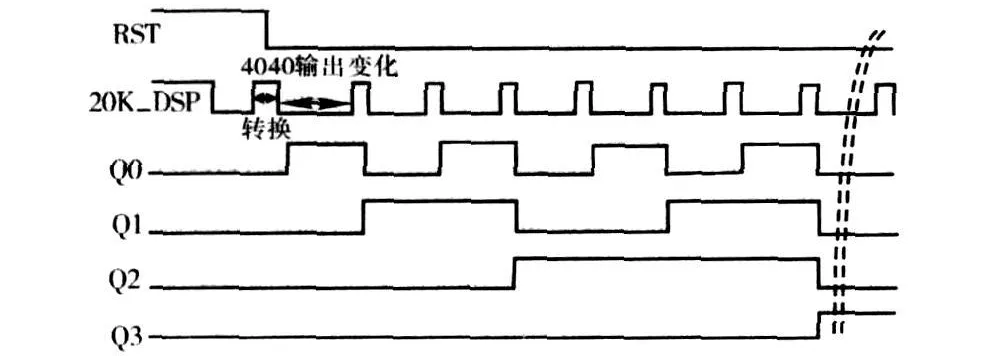

2.2 采样时序控制模块

系统采样时序由DSP产生时序发生器的复位信号及20K的时钟信号,时序发生器的输出再控制模拟开关。由于ADC真正的转换时间很短,因此20K时钟信号占空比并不是1∶1,而是将转换时间缩短,而留给模拟开关稳定的时间很长,这样可以最大限度的避免串扰的影响。如图2所示,时序发生器在20K_DSP的上升沿启动转换,下降沿输出变化。

图2 采样时序图

根据设计要求,DSP的三个ADC通道作为一个采样序列,每个通道的采样频率为20K。其中16路模拟信号通过模拟开关后进入DSP通道1,实际每路采样率为20/16=1.25K;四路模拟信号通过模拟开关后进入DSP通道2,实际每路采样率为20/4=5K;一路模拟信号直接进入DSP通道3,采样率为20K,TT L信号在一个采样序列结束时进行一次采样,因此采样率为20K。

2.3 FLASH存储模块

数据存储模块由存储器芯片和处理器接口组成。存储器芯片选择FLASH存储芯片,FLASH存储器是非易失性的,掉电后数据不会丢失,具有功耗低、擦写速度快、寿命长、体积小等优点[2]。处理器通过接口部分完成对FLASH存储器芯片的读、写等控制操作。

由于工艺等原因,FLASH芯片在出厂时就有可能存在无效块,使用过程中也可能产生无效块。如果对FLASH中的无效块进行操作,FLASH反馈的状态信息不稳定,可能使软件进入死循环,更为重要的是无效块会在数据记录的过程中造成数据的丢失和误码,影响数据的有效性和完整性,进而影响整个测试系统的性能。因此必须在使用前对FLASH进行无效块检查,避免对无效块的操作[3]。下面给出一种可以实现无效块地址实时更新的方法。

本设计通过发送固定指令,读取特定位置的坏块信息,调用FLASH内部的BLOCK0存储器区间存储无效块信息,规定BLOCK0中的数据即为无效块的地址。在BLOCK0中建立无效块地址列表,在数据采集过程中的读、写、擦过程中都需先将当前块地址与无效快地址列表进行对比,如果当前块为无效块,选择下一块进行同样操作,同时将此块的块地址写入无效块地址列表中,有效保证了无效块列表的动态更新。

2.4 通信模块

串行数据通信以其独特的优势在当今工程应用中占有非常重要的地位,DSP提供了可方便与计算机或其他串行设备连接的异步通信口。由于232总线存在共地噪声、传输距离短、传输速率低、抗干扰能力差等问题,因此通信模块采用RS-485串行接口总线标准,实现记录仪与PC机的全双工通信。

RS-485收发器采用平衡发送和差分接收,即在发送端,驱动器将T TL电平信号转换成差分信号输出;在接收端,接收器将差分信号变成TTL电平,因此具有很强的抑制共模干扰的能力,而且接收器具有高的灵敏度,能检测低达200mV的电压,最大传输速率达到10Mb/s[3]。由于在收发软件的设计中加入了握手机制,因此串口在大量读数时不会出现丢数现象。

3 数据编码及帧格式

由于数据记录仪是对31路信号进行实时采集存储,为了读数后数据分析的方便,就要在存储时对这31路数据进行编码区分。数据编码的主要作用是:将31路采集数据组合成一路经过编码的数据帧,以方便存储到FLASH存储器。

帧格式:具体定义了存储的每一帧的数据格式,也就是有效数据、帧计数写入存储模块的具体顺序。帧格式的定义方便了读数后的数据分析以及错误帧检查。

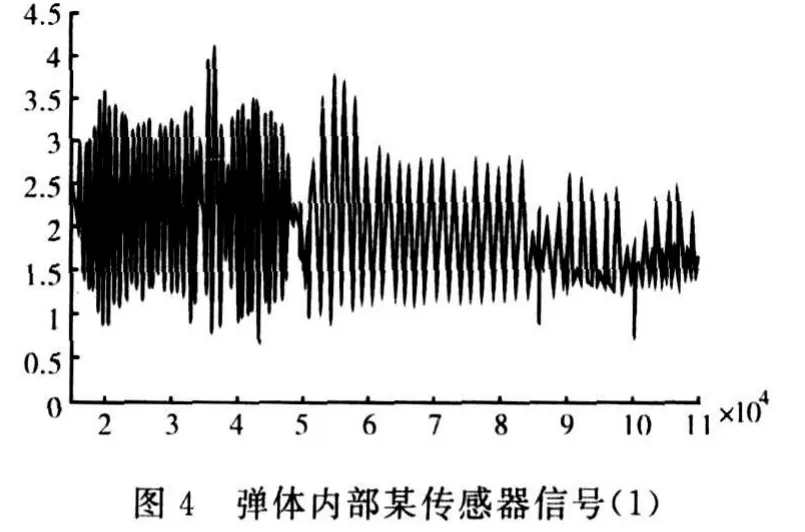

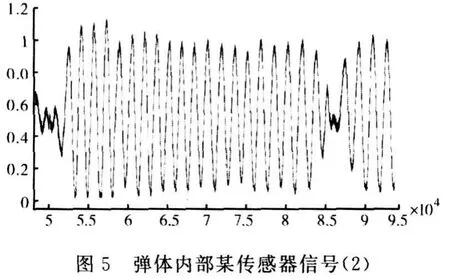

4 匹配试验数据

图3 弹体内部开关信号

由以上部分测试数据可以看出,系统准确地记录了载体内的重要信号,性能稳定,数据记录准确、实时性较好,完全符合设计的要求。

5 结论

文中完整地介绍了某型制导武器弹载数据记录仪的设计和研制,并且成功地运用于实际测试中。从样机的运行结果来看,系统完整地记录下了弹上的关键数据,完全达到了弹载数据记录仪各项性能指标的要求,为日后制导兵器测试弹的研制打下了坚实的基础。

[1]苏奎峰,吕强,常天庆,等.TMS320X281XDSP原理及C程序开发[M].北京:北京航空航天大学出版社,2008.

[2]NAND Flash Applications Design Guide[Z].System Solutions from Toshiba America Electronic Components,Inc.Revision 1.0 April 2003.

[3]林颖,罗金炎,刘骄,等.基于RS485总线的PC机与多单片机系统的串行通信[J].机械与电子,2006(1):34-37.