基于黑盒测试环境的交会对接软件时序分析技术及应用

2011-11-25张国峰王振华陈朝晖

张国峰,王振华,陈朝晖

(1.北京控制工程研究所,北京100190;2.空间智能控制技术重点实验室,北京100190)

基于黑盒测试环境的交会对接软件时序分析技术及应用

张国峰1,2,王振华1,2,陈朝晖1,2

(1.北京控制工程研究所,北京100190;2.空间智能控制技术重点实验室,北京100190)

航天器空间交会对接难度大,GNC软件对任务的完成起到重要作用.由于交会对接控制软件功能复杂,时序要求严格,这对软件测试提出了很高的要求.基于黑盒测试环境,利用FPGA设计方法和时序分析技术,实现了对交会对接软件重要数据运行时序的捕获和对上下行信号相位关系的跟踪,完善了故障触发和上行注入手段.该测试环境在交会对接软件研制过程中起到重要作用.

交会对接;GNC软件;黑盒测试;黑盒测试环境;FPGA设计;时序分析

航天器空间交会对接技术复杂,只有少数几个国家掌握.目前已投入使用的国外空间交会对接飞行器有:美国的航天飞机(2011年发射后已退役)、俄罗斯的联盟号载人运输飞船、进步号货运飞船、欧盟的ATV货运飞船、日本的HTV货运飞船[1].而中国的首次空间交会对接的成功打破了这一技术垄断.

交会对接分为交会和对接两个主要阶段.交会指两个航天器在轨道上的接近过程,即从追踪航天器远距离(150km~80km)导引去接近目标航天器开始,直到满足两航天器对接机构实施对接的初始条件为止.对接是指在满足两航天器对接机构条件下,对接机构完成耦合和刚性密封连接的过程[2-3].交会过程中,在与目标飞行器不同的距离情况下,运行不同的飞行模式,采用不同的控制算法,这是一个任务要求极高的系统[4],由此对软件的可靠性、安全性提出了很高的要求,软件时序十分复杂.

1 空间交会对接软件特征及测试要求

GNC软件是交会对接控制的核心,功能复杂,时序苛刻,该软件工作的正确与否直接影响到空间交会对接任务的成败.

因此,对飞船软件运行时序的分析具有重要意义.通过时序分析可以获得准确的软件运行时序和调用关系,分析潜在的时序冲突,从而提升空间交会对接软件的可靠性和安全性,为提高软件质量服务.

由于任务的复杂性,导致航天控制软件尤其是空间交会对接软件具有如下特点:1)软件复杂度高,时序要求严格;2)软硬件联系紧密,性能要求苛刻;3)极高的可靠性和安全性要求.交会对接导航制导控制属于安全关键性A类软件,容错处理,纠错处理和其他安全性设计作用突出.

根据交会对接软件的特点,针对软件的确认测试具有如下特点:1)外围接口多样,时序复杂,需要设计专门的测试环境,其仿真度和真实性直接影响软件测试的可靠性;2)被测试软件强实时性要求和复杂度高的特点,要求测试环境有较强的时序分析和性能测试能力.

2 基于黑盒测试技术的半物理仿真测试环境

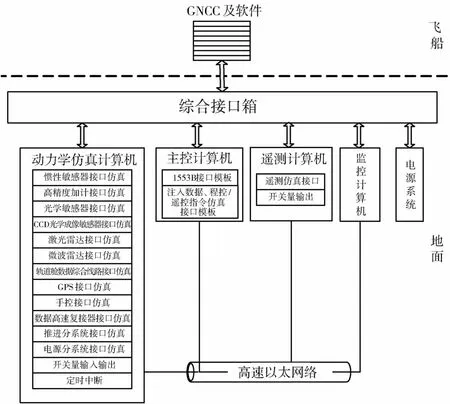

为提高型号软件的质量,航天系统应十分重视软件开发工具和环境的使用[5],交会对接软件半实物环境对于测试工作具有重要意义,是测试船载软件的一种非常有效的手段,与此同时该环境也是进一步开展自动化测试的基础条件之一[6],该测试环境主要包括动力学仿真计算机、遥测计算机、主控计算机、监控计算机、综合接口箱和电源系统等部分,如图1所示.

半物理仿真测试环境与星载计算机构成了闭环回路,控制软件运行在这个环境上.通过运行在测试环境中的船地联试可以验证船载软件的正确性,验证系统方案的准确性、完整性,为应用软件提供一个动态闭环调试和测试环境,并及早发现软件中潜在的问题.

交会对接软件的确认测试主要在一套基于黑盒测试技术的半物理仿真测试环境中进行,该测试环境通过对交会对接飞行提供轨道动力学运算仿真,对惯性敏感器、红外地球敏感器、太阳敏感器等定姿敏感器、以及CCD、激光雷达等各种交会对接敏感器接口模拟和信息处理的模拟,对遥控遥测、上行注入和总线通信的仿真,与真实的GNC计算机和应用软件组成一个闭环的交会对接软件运行环境.

图1 黑盒半物理仿真测试环境结构图

通过半物理仿真环境,对交会对接软件的功能进行测试.对交会对接软件这样复杂的软件,不满足于只对功能点进行测试,需要尽可能地了解其运行时序,尤其是重要数据和有可能导致多级中断嵌套异常的情况.

3 时序分析技术及其应用

在基于黑盒的软件测试环境基础上,我们综合利用FPGA设计与同步基准处理等技术,通过对外围信号的采集和处理,获得船载计算机外部信号与基准信号相位差的关系,通过动态对采集数据进行相应的处理和分析,获得所关注的重要信号的时序关系,有效地提升了测试平台对时序分析的能力.从而能够及时地对测试中的中断冲突等异常情况进行分析和快速定位,确保软件的整体研制进度.

3.1 仿真环境时序分析硬件设计

对外围器件的模拟,采用通用化的FPGA数字量输入输出板卡设计,可以在同一块板卡上实现对多路复杂协议的模拟.

在上行数据设置和下行数据采集的设计上,FPGA仿真板卡均采用100MHz高稳定性精密有源晶振,因此在时间记录上,能够达到0.01μs的精度.同时,高速的工作主频,能够更大程度地减少数据处理所耗的时间,进而降低系统工作时造成的时间累积误差,提高时序电路的计数精度.

板卡上所选FPGA选取200万门、40个快存储RAM、4个时钟单元,完全能够胜任高难度、复杂性的数字时序逻辑模拟功能.其较大容量的存储特点,可专门用来实现大数据量存储的功能、开辟多个数据缓存区,防止数据丢失.通过拨码开关,可以选择切换板卡内部所加载的程序内容,提高测试设置的灵活性;FPGA的配置芯片带有4个预存程序区,板卡可根据拨码开关来选择需要加载的功能模块,实现一板多用.该功能的设计简化了多种板卡复杂操作的模式.

3.2 时间同步技术和数据完整性设计

在时间同步问题上,通过引入船载计算机的硬件控制周期信号,此信号为船载软件的定时中断信号,因此可以通过记录船载计算机所有上下行信号与控制周期信号的精确时间戳,作为进行船载软件时序分析的基础.

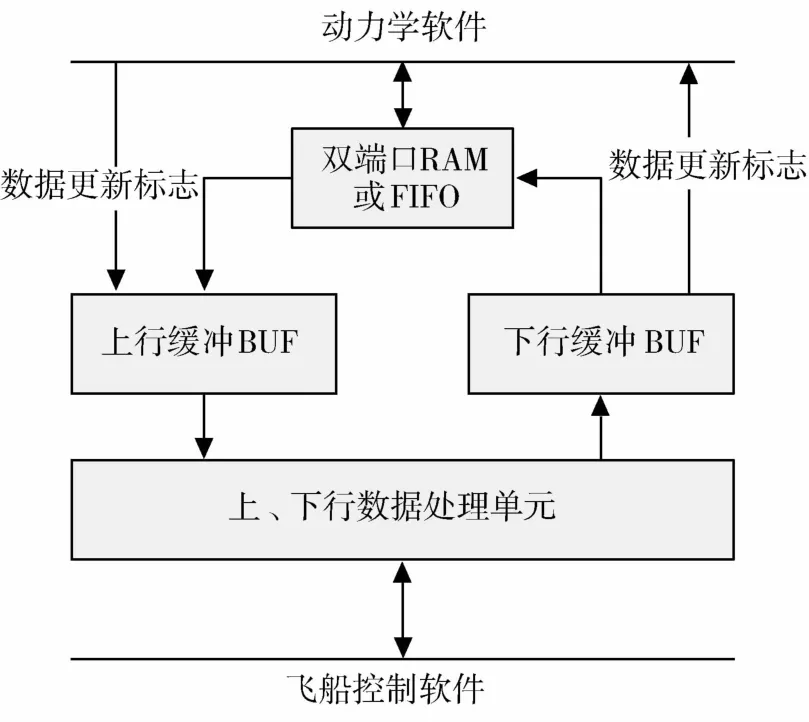

此外,还必须在设计上保证上下行数据的完整性.动力学软件每个控制周期访问一次 FPGA,对上下行数据进行处理.由于动力学软件与船载软件的非同步性,所以可能会出现丢包、错包的情况.如FPGA正在发送上行数据时,动力学软件更改发送数据;或者FPGA正在接收下行数据,而动力学软件在访问FPGA获取数据.设计中采用二级缓冲BUF的方式来保证各种数据包完整.结构图2所示.

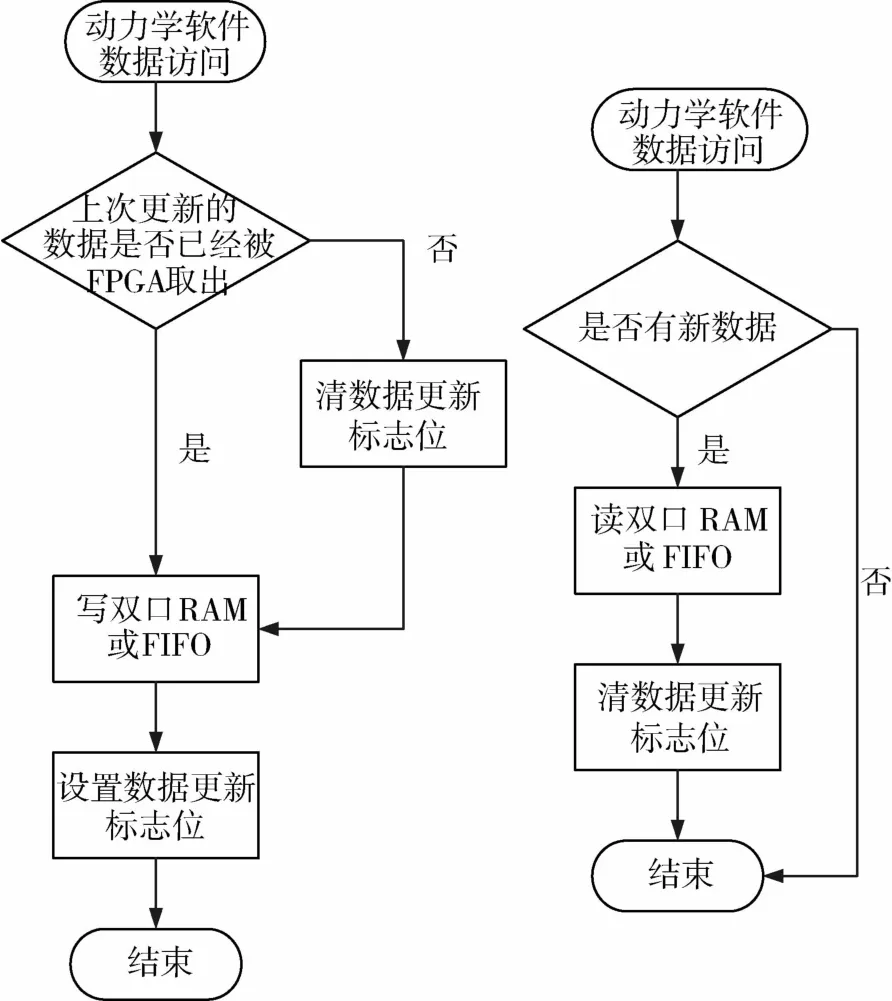

采用缓冲BUF之后,动力学软件对上行数据的处理流程如下:上行数据处理单元是用FPGA来实现的,该单元在空闲状态时,查询数据更新标志,如果有新的数据,则从双口RAM或者FIFO中取出数据到缓冲 BUF中,当数据取空之后,清数据更新标志.

FPGA的IP核对数据的处理流程如下:下行数据处理单元采用FPGA实现,该单元在接收到完整的船上数据后,设置数据更新标志,将数据写入双口RAM或者FIFO中.由于FPGA和PCI总线接口桥接芯片 PCI9054采用同步设计,因此避免了FPGA处于读写过程而PCI9054处于写读过程时发生数据冲突的可能.动力学访问上下方式参见图3.

图2 二级缓冲BUF结构

图3 FPGA及上位机软件数据处理流程

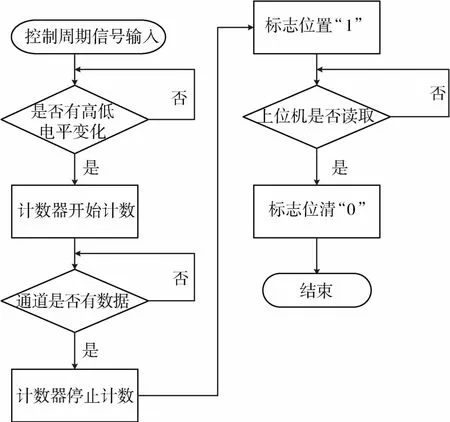

FPGA软件对时间戳的处理流程如下:上下行通道所对应的计数器在检测到控制周期下降沿(或上降沿,可由上位机软件设置)后,作为时间记录的基准,开始计数,FPGA下行数据处理单元在接收到相应的船上数据后,立即停止计数,记录时间戳并计算相位差,同时,将所计数据存入FPGA内部的缓存区,清零计数器,并把相位差测量标志位置“1”.当上位机扫描到该通道的标志位为“1”时,将缓存区数据读取,并清除标志位.该数据即为所记录的电平信号的相位差,当量为0.01μs,时间戳记录流程见图4.

3.3 敏感器和执行机构等接口设计

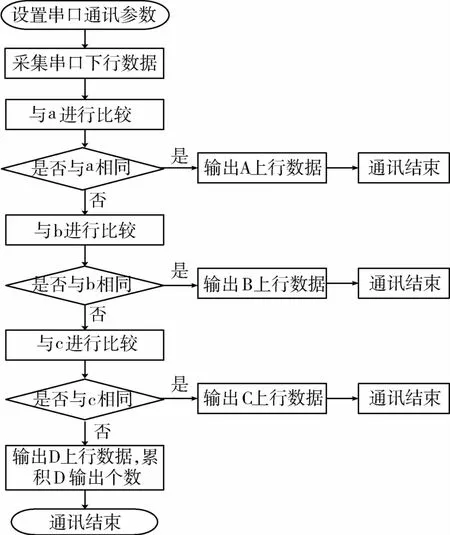

动力学功能板卡对接收到的下行通信数据进行判断,当下行通信数据的帧头与a数据区的内容相同时,发送A数据区的内容;当下行通信数据的帧头与b数据区的内容相同时,发送 B数据区的内容;当下行通信数据的帧头与c数据区的内容相同时,发送 C数据区的内容;若都不相同,则发送D数据区的内容,并累计发送 D的次数.同时,可设置上行发送数据的响应时间和间隔时间.

图4 时间戳记录流程

在功能板卡正常工作之前,首先需要上位机软件对异步通信串口进行参数设置,否则无法正常完成通信工作.设置内容包括:a数据区的个数、a数据区的内容、b数据区的个数、b数据区的内容、c数据区的个数、c数据区的内容、A数据区的个数、A数据区的内容、B数据区的个数、B数据区的内容、C数据区的个数、C数据区的内容、D数据区的个数、D数据区的内容、响应时间、间隔时间、接收数据个数、比较数据个数.

当设置完所需参数后,即可正常工作.上位机可通过总线读取板卡中数据缓存区中接收到的下行通信数据,同时也可读取D的个数、时间戳等数据内容.板卡中的计时当量均为0.01μs.同时,每路串口均带有响应开关,可通过上位机软件进行设置.板卡在接收数据过程中,超时后(长时间无下行数据)会进行复位(即结束该次通信过程).

串口功能模块内部带有一个专门记录时间戳的计数器.当板卡查询到串口有下行数据时,触发计数器开始计数;当接收完毕后开始发送上行数据时,关闭计数.FPGA将所计数据存入内部缓存区,在发送上行数据时将接收完毕标志位置“1”.上位机检测到该标志位后,读取缓存区中接收的数据以及所记录的时间戳.

值得一提的是,本次串口程序设计采用并行工作模式,即采用边收数,边比对的模式.当串口接收第一位字节后,立即与 a、b、c数据区的第一位字节进行比对,以此类推.当接收完下行数据后,也同时完成了数据的比对工作,可迅速得出结论,是发送 A、B、C、还是 D.并行工作模式,能够有效地利用FPGA内部门电路资源,从而能够更加快速地完成数字逻辑电路的运算.由于接收功能和比对功能几乎同步完成,因此对于串口时间戳的计时结果,几乎不会产生系统运算因耗时而造成的累积误差,时间戳数值可非常精确,异步串口处理流程参见图4.

图5 异步串口处理流程

3.4 异常保护

1)板卡上的FPGA最多可开辟40个FIFO数据缓存区,在FPGA程序研发时,为每个下行数据存储区均开辟了一个备份存储区.当上位机未及时读取数据时,用户无需担心数据由于被改写、覆盖而丢失的情况发生,因为未及时读取的数据均已存入备份存储区.

2)当执行串口通信功能时,如果船上的下行数据在发送过程中突然出现异常情况,导致发送过程无法完成或继续.仿真板卡会做出超时响应,停止此次接收并复位到初始状态.为不影响板卡工作稳定性及可靠性,超时时间设置并为对用户提供响应设置接口,超时时间设定数值由研发人员直接设定在功能程序内部.

3)板卡的连接接口在初始化前均设定为高阻模式,在将用户设备接入整套系统时,保证了用户设备的安全性.当上位对板卡机初始化后,板卡接口的输入输出才被开启.

4)板卡带有热插拔功能,能够在插拔板卡时,迅速对相关电路断电.加强了用户方设备的安全性.

3.5实际应用

使用上述时间戳记录的方法,可以获得船载软件对敏感器和执行机构等外围部件操作的准确相位差,从而分析出船载软件在每个控制周期对外围部件的时序关系.同时,通过此方法也可对船载计算机外部中断信号的触发时序进行控制,从而实现对船载软件的多级中断并发测试和嵌套测试,保证了软件的可靠性和安全性.

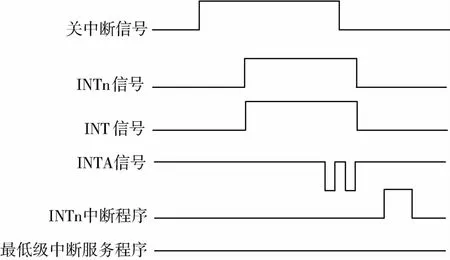

某次调试过程中发现敏感器相位关系异常,程序运行也发现中断控制状态异常.在程序运行过程当中,程序会偶尔进入陷阱中断,通过遥测记录的数据发现进陷阱中断的计数器计数值增加,表明程序进入陷阱中断服务程序.

根据所记录的时序关系状态初步确定为中断时序嵌套存在不合理.

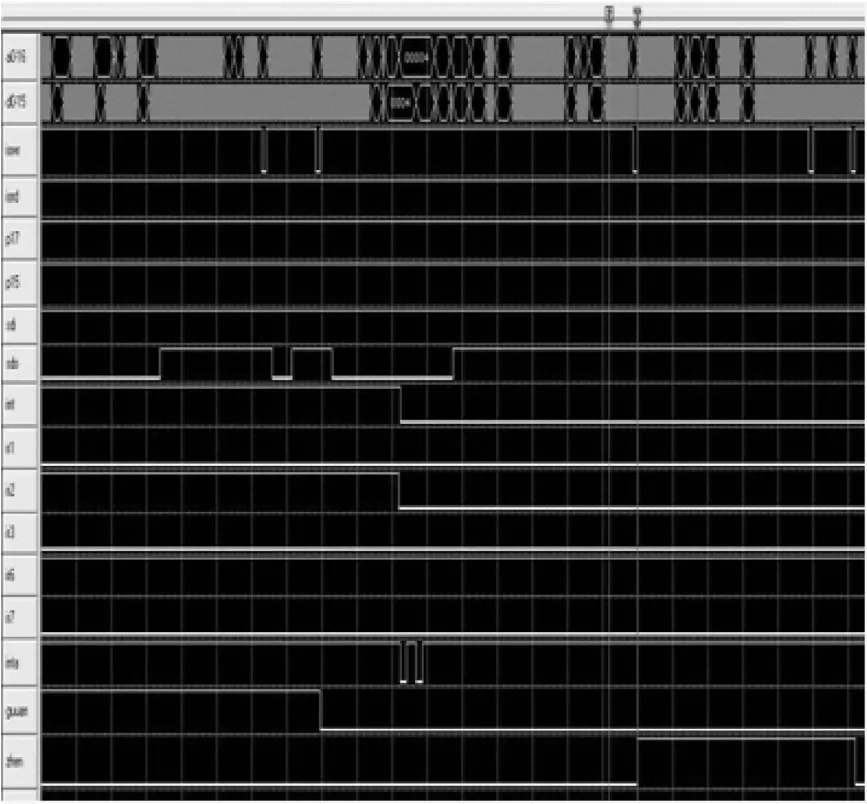

通过使用逻辑分析仪确认了数据分析的正确性,实验捕获异常状态参见图6.

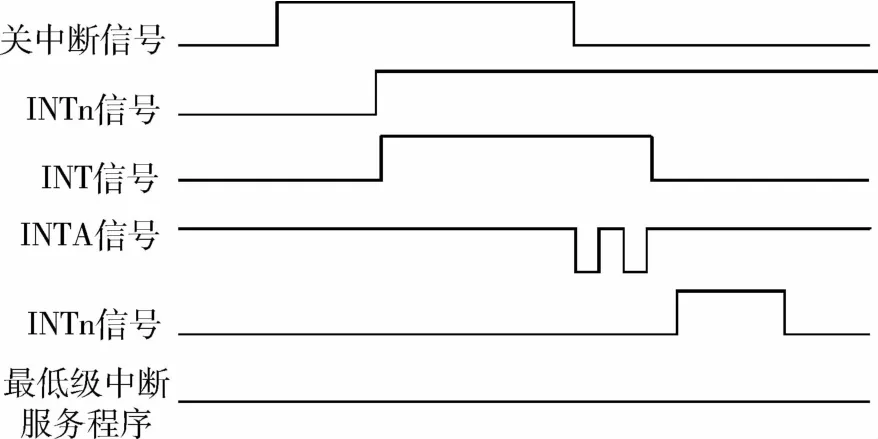

故障的原因:如果中断高电平时间太长时,如图7所示,对于82C59中断的沿触发来说,在高电平期间,不可能形成一个上升沿,影响了同一个中断的下次触发,造成了中断的丢失.异常和正常的时序分析曲线参见图7~8.

通过采用本文介绍的时序分析技术对软件运行进行分析,提示设计人员从软件上或硬件上采取措施来改善中断请求信号的高电平长度,从而提高多级中断的可靠性设计,由此提升航天嵌入式软件的质量,在进行相应的更改后该问题不再复现.

图6 逻辑分析仪捕获的软件时序

图7 高电平时间太长时序情况

图8 正常响应中断时序情况

4 结 论

基于黑盒的时序分析技术能够通过对传统半物理仿真测试平台进行改进,获取所需要的上下行信号的时间特性,从而对船载GNC软件进行相应的时序分析.

下行采集:改变以前黑盒测试环境只能进行功能测试,无法获取软件运行的时序关系的现状,获得了对复杂软件运行的时序关系,特别是船载计算机与外部敏感器和执行机构接口处理的时序状态和相位关系.

上行设置:可以对上行外部中断信号的触发时序和相位差进行设置,实现对多级中断的优先级和中断嵌套测试,完善故障设置能力,综合提高对航天器交会对接软件测试的充分性,提升软件测试覆盖性.

实践证明:通过对上述时序分析技术的应用,提升了半物理仿真测试环境的性能测试能力,为软件的可靠性设计提供依据.在通过测试环境的时序分析后能够初步定位问题,给后续的精确定位提供了方向,节约了宝贵的研制开发时间.

[1] Valin T.Commercial crewamp;cargo program overview[C].ISS-A New National Laboratory Special Session AIAA Aerospace Sciences Meeting,USA, January 11,2007

[2] 张淑琴,王忠贵,冉隆隧,等.空间交会对接测量技术及工程应用[M].北京:中国宇航出版社,2005

[3] 朱仁璋.航天器交会对接技术[M].北京:机械工业出版社,2007

[4] Sommerville I.软件工程[M].程成,陈霞,译.北京:机械工业出版社,2007

[5] 石柱.航天星载软件工程化十年回顾与展望[J].航天控制,2006,24(4):66-72

[6] 陈能技.软件测试技术大全[M].北京:人民邮电出版社,2008

Tim ing Sequence Analysis Technique for Black Box Test Environm ent-Based Rendezvous and Docking Software and Its App lication

ZHANG Guofeng1,2,WANG Zhenhua1,2,CHEN Zhaohui1,2

(1.Beijing Institute of Control Engineering, Beijing 100190,China;2.Science and Technology on Space Intelligent Control Laboratory, Beijing 100190,China)

The rendezvous and docking of spacecrafts is a difficult task,the GNC software is very important for it.The software is complex, the demand for timing sequence is strict, and the software testmust be in high level.For the black box test environment-based software,FPGA design method and timing sequence analysis technique are used to obtain timing sequence capture ability,and the fault trigger and data injectmethod is also improved,this technique is proved to be very useful in the development of the rendezvous and docking software.

rendezvous and docking;GNC software;black box test;black box test environment;FPGA design;timing sequence analysis

TP31

A

1674-1579(2011)06-0060-06

DO I:10.3969/j.issn.1674-1579.2011.06.010

2011-09-20

张国峰(1972—),男,山西人,高级工程师,研究方向为航天器嵌入式软件技术(e-mail:zhanggf@bice.org.cn).