高速CCD成像电路抗串扰技术

2011-11-06薛旭成李洪法郭永飞

薛旭成,李洪法,郭永飞

(中国科学院长春光学精密机械与物理研究所,吉林长春130033)

1 引言

电荷耦合器件(CCD)由于具有低噪声、宽动态范围以及线性响应等优点,在成像领域获得了广泛的应用。使用CCD成像系统时,需要成像电路的支持。成像电路主要包括CCD时序产生及驱动电路、CCD视频信号放大电路、CCD视频信号相关双采样电路以及模数转换电路等。其中CCD驱动电路驱动电容性负载,会导致瞬态大电流的产生,而此电流会成为一种干扰源。模数转换电路是模拟域和数字域的转换电路。因此,CCD成像电路是一个复杂的模数信号混合电路系统。如果设计中不采取抗串扰技术,CCD驱动信号和数字电路信号会对CCD视频模拟信号产生串扰,在高速情况下这种串扰会更加严重。此外,为了实现高速成像,CCD往往采用多个视频抽头并行输出技术,每个抽头都需要相应的处理电路,这样成像电路又是一个多通道并行处理系统,这些通道间也会产生相互串扰。串扰的产生主要是由于印刷电路板(Print Circuit Board,PCB)的设计不合理,这种现象在调试阶段才会发现,此时PCB已经加工完成,难以修改,重新设计又会增加产品的成本,使产品不能按期完成,因此,在设计阶段就要对串扰现象进行研究,并采取有效措施防止串扰的产生。

国内外相关技术人员对串扰问题已经进行了大量的研究。如,哈勃望远镜上WF/PC I相机出现的串扰问题,其等效噪声电子数达100e-。为了解决它的定位,花费了近一年的时间。最后,是在采样和模数转换时采用集总参数电路的方法禁止时钟并屏蔽复位信号及视频信号线来降低串扰[1]。文献[2-4]对信号在PCB中的传输进行了分析建模,解决了信号完整性问题。文献[5-6]分析了传输线间相互串扰的传输线模型。文献[7]则采用信号处理的方法识别串扰信号的频率。本文应用相邻走线的传输线模型和电源接地的开关噪声模型具体分析了CCD成像系统的串扰,并研究了相应的抗串扰技术。

2 CCD成像电路串扰模型

为了解决串扰问题,需要研究串扰产生的原因。如果PCB上的走线是理想的导线,那么电路就不会发生串扰。理想的导线包含两方面内容:一是指信号在导线上的传输不需要时间;二是指导线的电阻、电感以及电容都是零。信号在导线上的传输不需要时间表明导线上的各点电压在同一时刻是相同的,也就是说导线可以认为是一点,这是基尔霍夫电路理论的假设。由于导线的各点电压相同,因此,电路理论中信号只是时间的函数而不是空间的函数。实际上由麦克斯韦方程组描述的电磁理论才是准确的物理定律。基尔霍夫电路理论由于忽略了信号随空间的变化,因此只是低频近似理论。当电路工作频率提高时,信号就会出现反射等现象,此时需要用基于电磁理论的传输线理论来进行分析。此外,在高频下PCB走线的电阻、电感以及电容也不能忽略。电感和电容还包括和其它PCB走线间的互感和互容。这些由PCB走线非理想导致的电阻、电感和电容现象称为寄生现象。寄生现象导致了信号线被其他走线通过互容和互感方式进行干扰,信号反射等现象则进一步使串扰加重。此外,电路间共用电源和地线也会导致由公共阻抗产生的串扰。

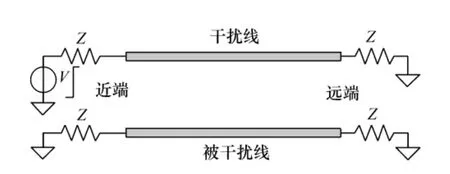

图1 相邻走线的等效传输线模型Fig.1 Transmission line model of two close routes

CCD成像电路中,PCB走线主要包括CCD视频信号走线、CCD驱动走线、数字电路走线等。不管这些走线是什么类型,当靠近信号走线时,都有可能对信号走线构成干扰。这时串扰的模型可以看成是PCB上相邻的两条走线,一条为干扰线,另一条为被干扰线。根据传输线理论可知,在被干扰线的两端测得的干扰电压是不同的,距离源端最近的一端为近端,而离源端最远的一端为远端,如图1所示。

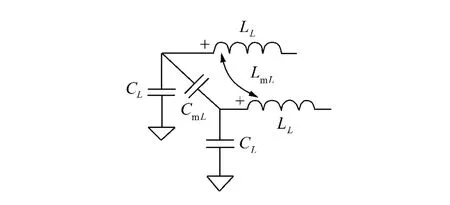

可以用互容和互感组成的电路模型来描述耦合。图2为串扰模型等效电路。由于互容和互感都与长度成比例,所以这里使用单位长度互容CmL和单位长度互感LmL。

图2 互容互感耦合电路模型Fig.2 Couple circuit model of mutual capacitance and mutual inductance

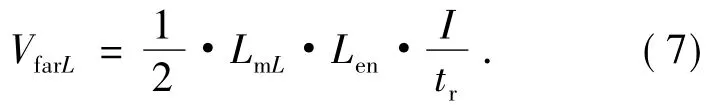

当信号沿着干扰线传播时,其通过互容和互感作用到达被干扰线上。然而,只有在信号变化的区域互容和互感才能干扰被干扰线[8]。那么通过互容产生的干扰电流为:

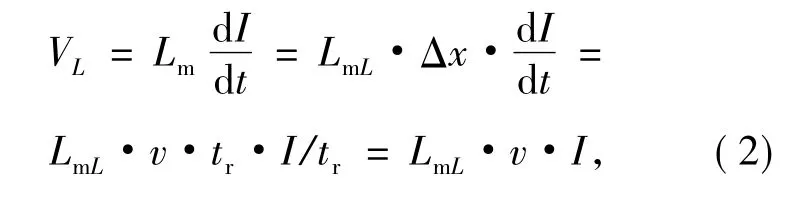

式中:Cm表示干扰信号上升沿在走线中延伸长度对应的总电容,V表示干扰信号电压,Δx表示干扰信号上升沿在走线中延伸的长度,tr表示干扰信号上升沿时间,v表示干扰信号的传播速度。通过互感产生的干扰电压为:

式中:Lm表示干扰信号上升沿在走线中延伸长度对应的总电感,I表示干扰信号电流。干扰信号的传播速度为:

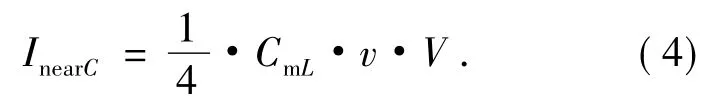

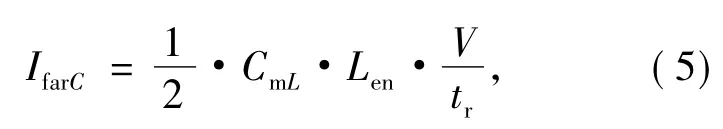

式中,Z为每条走线的特性阻抗。通过互容产生的干扰电流流到近端的大小为:

通过互容产生的干扰电流流到远端的大小为:

《水利工程代码编制规范》(SL 213—2012)在原有标准《水利工程基础信息代码编制规定》(SL 213—98)基础上,进行了几方面修订:一是将标准名称由“水利工程基础信息代码编制规定”更改为“水利工程代码编制规范”。二是在技术内容上,调整了河流代码的编码规则;调整了堤防代码的编码规则;调整了灌区和水土保持工程的分类码;修改了湖泊代码的编码规则;修改了水文测站代码的编码规则;修改了穿堤建筑物的编码规则;将墒情测站代码、地下水观测井站代码归入水文测站代码;将发电工程代码更改为水力发电工程代码,并修改了编码规则等。

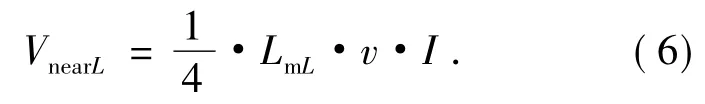

式中,Len为干扰走线总长度。通过互感产生的干扰电压在近端大小为:

通过互感产生的干扰电压在远端大小为:

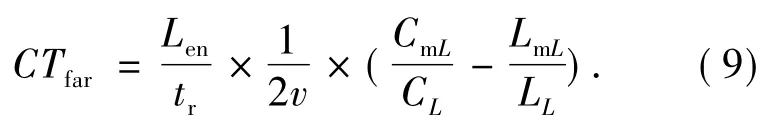

由式(3),(4),(6)可得近端串扰系数为:

同样由式(3),(5),(7)可得远端串扰系数为:

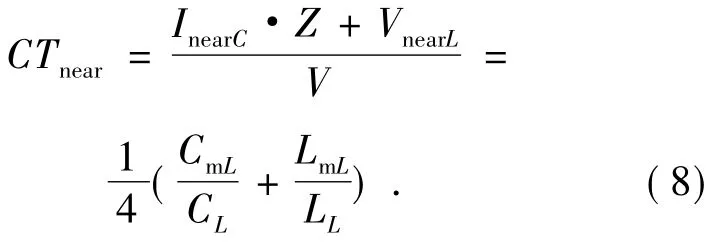

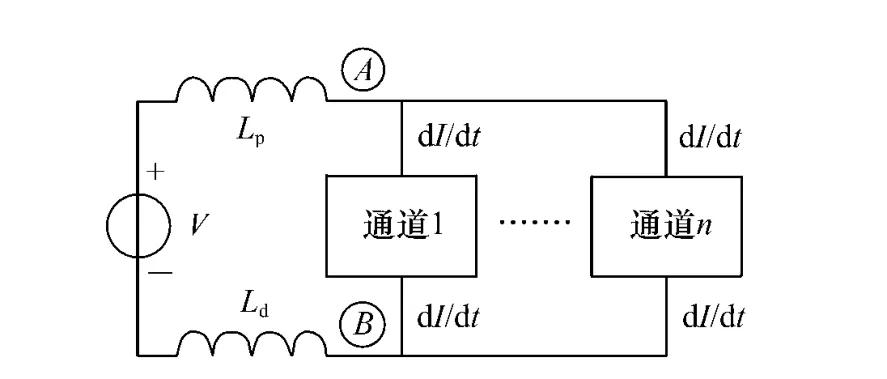

下面分析电源和地线对串扰的影响。由于电源和地线不是理想的导线,因此,会通过电源和地线的公共阻抗产生串扰。图3为电源和接地的开关噪声模型。电源和接地的寄生成分主要是电感,用Lp表示电源等效电感,Ld表示接地电感。当通道1电路中有变化的电流dI/dt时,就会导致A点电压的波动:

图3 电源接地的开关噪声模型Fig.3 Switch noise model of power supply and ground

从而影响其它通道的供电电压产生串扰。同样B点也会产生电压波动,从而产生串扰。

3 CCD成像电路抗串扰技术

对上述串扰模型进行分析,可以得到相应的有效抗串扰措施。

3.1 特性阻抗控制和端接技术

端接方案如图4所示。可以在源端端接,也可以在接收端端接。对于数字信号,为了降低功耗可以只在源端端接,而对于模拟信号,则在源端和接收端都进行端接,使反射降至最低。

图4 传输线端接方案Fig.4 Termination scheme for transmission line

3.2 带状线及防护布线隔离技术

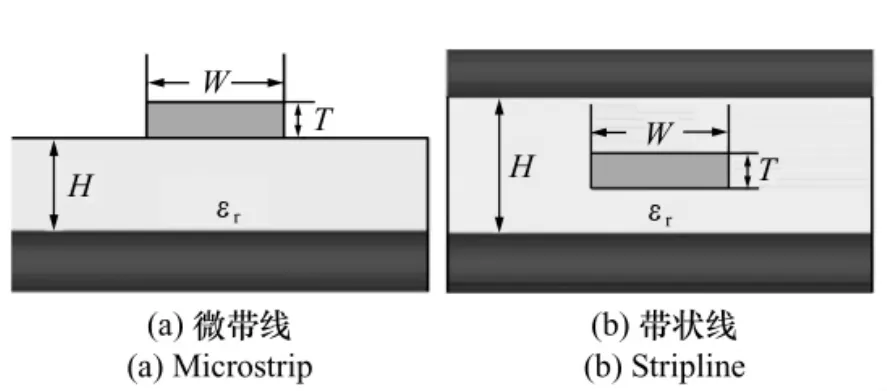

在PCB走线中有两种常用且重要的走线方式,即微带线和带状线[9]。微带线是指走线下面为PCB介质,参考平面上面为空气,即PCB的外层走线,如图5(a)所示。带状线为走线被PCB介质包围,上下都是参考平面,如图5(b)所示。从下面分析可以看出,相邻的带状线不存在远端串扰。

图5 微带线和带状线结构Fig.5 Structures of mircrostrip and stripline

两条相邻的走线可以支持偶模和奇模两种模态的传输。偶模的两条走线传输同相位的信号,奇模则传输反相位的信号。偶模的单位长度传输延时为:

奇模的单位长度传输延时则为:

而信号单位长度传输延时可表示为:

式中:εr为有效介电常数,c为光速。由于微带线暴露在空气中,其偶模和奇模的有效介电常数是不同的,而带状线则是相同的。即带状线的偶模和奇模传输延时相同,得到:

即:

根据式(9)可得远端串扰系数为零。实际上,即使是带状线,介质材料也不可能完全同质,所以介电常数总有一些变化,这种介质分布不均匀将引起远端噪声。为此,可以在带状线间加入接地走线形成防护走线,进一步降低串扰。对于CCD视频信号,采用带状线并使用防护布线进行隔离将大幅度降低串扰。

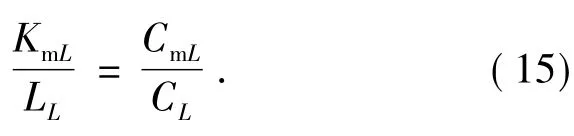

3.3 电源隔离及去耦技术

CCD视频信号串扰的另外一个原因是共用电源,为此,需对多通道电源供电进行隔离设计。如图6所示,每个通道的电源入口都采用去耦滤波设计。Ld为磁珠,在工作频率要有足够高的阻抗。电容Cb和Cd则根据电路的工作频率选择参数,具体实现时还要使用多个电容并联以减少寄生电感。

图6 电源隔离设计Fig.6 Design of isolation of power supply

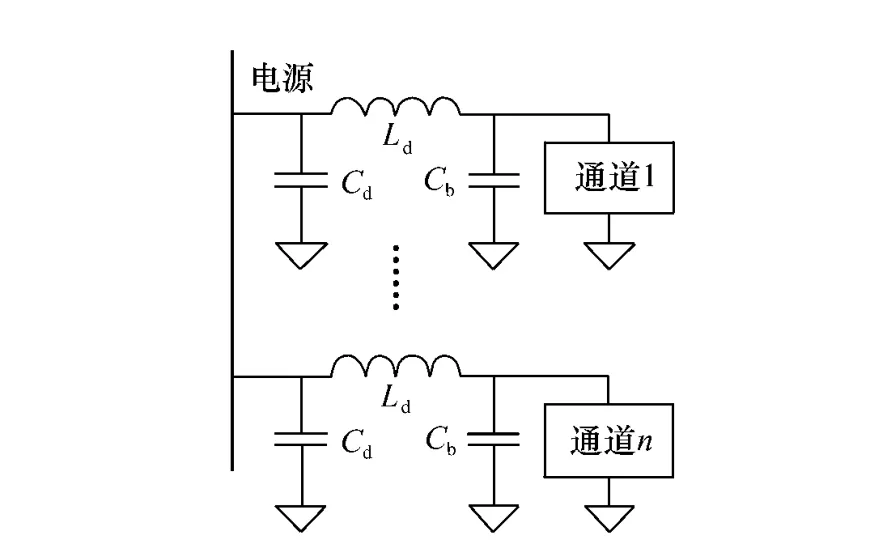

如图7所示,采用多个过孔连接方法对去耦电容布线[10],这种方法可以把寄生电感减少到0.4 nH。

图7 去耦电容布线方法Fig.7 Routing method of decoupling capacitor

3.4 统一地平面技术

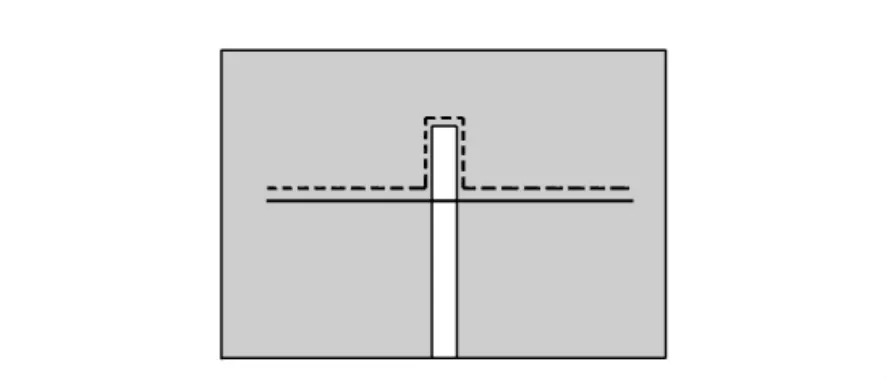

为了防止数字电路对模拟电路造成干扰,应对模拟电路和数字电路进行分区布局,但采用统一的地平面[11],不能让走线跨越分割的地平面。如图8所示,黑色的粗线为PCB走线,当它跨越分割的地平面时,返回电流要按照最低电感的路径返回,如虚线所示。这样返回路径和没有分割地平面相比电感大了很多,因此,会造成地平面电压的波动,形成地弹,从而影响信号。

图8 地平面分割Fig.8 Partition of ground plane

4 实验结果

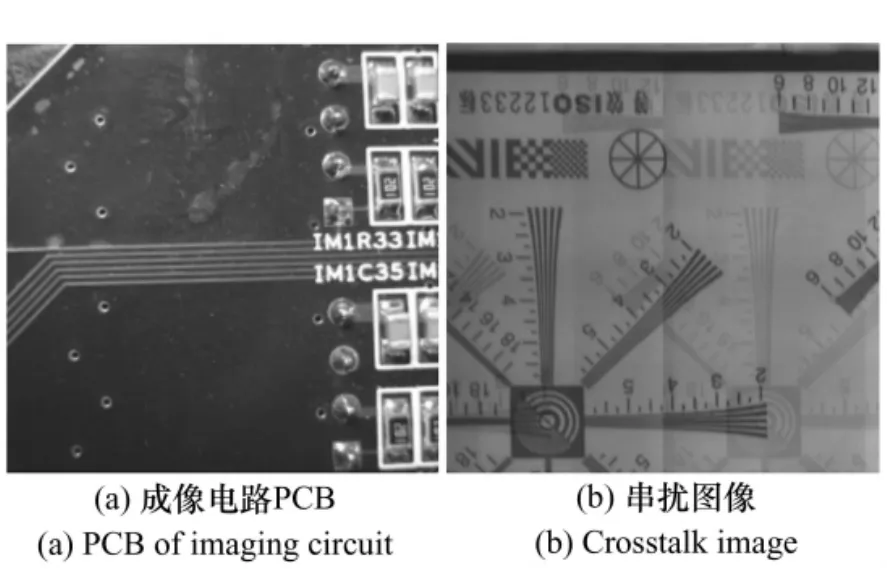

图9为一个串扰较严重的CCD成像电路的PCB及其成像结果。图9(a)所示为CCD视频信号走线,由于是微带线且走线距离很近,因此,串扰较严重。图9(b)为该CCD相邻两个通道的成像图像,可以看出存在着明显的相互串扰现象。

图9 存在串扰的成像电路PCB及串扰图像Fig.9 PCB of crosstalk imaging circuit and crosstalk image

采用上述抗串扰技术对该CCD成像电路进行了重新设计,视频信号走线采用具有防护走线的带状线。对新的成像电路进行了PCB走线特性阻抗的控制和端接,电源进行了隔离设计,采用统一的地平面。图10(a)为新的成像电路的成像图像,可以看出串扰已经消除。图10(b)为测试通道隔离度的串扰图像。实验中把一个通道的视频输入接地并设置偏置,研究另外一个图像通道对其的影响。由于输入接地的通道没有串扰产生,图像为10 bit,因此,通道隔离度大于60 dB。

图10 新系统的成像及串扰测试图像Fig.10 Imaging of new system and crosstalk test image

5 结论

CCD成像电路系统是个多通道并行处理模数混合信号系统。由于电路工作频率高,如果在设计中对抗串扰措施不给予充分重视,信号通道间极易发生串扰现象,且驱动信号和数字信号也会干扰模拟信号,从而使图像质量下降。本文通过对串扰机理的分析,给出了有效的抗串扰措施,所有的模拟和数字信号线都采用特性阻抗控制技术和端接技术,避免了信号自身的反射对信号质量的影响。对多通道的CCD视频信号采用带状线而非微带线并使用防护布线进行隔离。对多通道的电源供电进行了隔离设计,并采取有效的去耦电容布线方法降低寄生电感,从而避免了由电源公共阻抗引起的串扰。采用统一的地平面对模拟电路和数字电路进行分区布局,避免了地弹对信号的影响。采取上述技术,避免了串扰的发生,通道隔离度大于60 dB,保证了图像的质量。

[1] JANESICK J R.Scientific Charge-Coupled Devices[M].Bellingham:SPIE Press,2001:714-715.

[2] SHARMA R,CHAKRAVARTY T,BHATTACHARYYA A B.Analytical model for optimum signal integrity in PCB interconnects using ground tracks[J].IEEE T.Electromagn.C.,2009,51(1):67-77.

[3] SCHUSTER C,FICHTNER W.Parasitic modes on printed circuit boards and their effects on EMC and signal integrity[J].IEEE T.Electromagn.C.,2001,43(4):416-425.

[4] 刘学观,江盼盼,郭辉萍,等.高速数字信号在PCB中的传输特性分析[J].电波科学学报,2009,24(3):498-500.LIU X G,WANG P P,GUO H P,et al.Transmission characteristics of high-speed digital signal in PCB[J].Chinese J.Radio Sci.,2009,24(3):498-500.(in Chinese)

[5] 董刚,杨杨,柴常春,等.考虑工艺波动的两相邻耦合RC互连串扰噪声估计[J].西安电子科技大学学报,2010,37(6):1082-1087.DONG G,YANG Y,CAI CH C,et al..Crosstalk noise estimation of two adjacent RC interconnects with process variations[J].J.Xidian University,2010,37(6):1082-1087.(in Chinese)

[6] 安静,武俊峰,吴一辉.防护带结构参数对耦合微带线间串扰的影响[J].武汉理工大学学报,2010,32(23):81-84.AN J,WU J F,WU Y H.Influence of the structural parameters of via fences on reducing the crosstalk between coupled microstrip lines[J].J.Wuhan University Technol,,2010,32(23):81-84.(in Chinese)

[7] 丁爱萍,金建刚,孙士保.小波函数在识别PCB串扰信号频率中的应用[J].微电子学与计算机,2010,27(7):146-148.DING A P,JIN J G,SUN SH B.Applications of wavelet functions in recognizing PCB crosstalk signal frequency[J].Microelectronics Computer,2010,27(7):146-148.(in Chinese)

[8] BOGATIN E.Signal Integrity-Simplified[M].Englewood Cliff,NJ:Prentice Hall,2003.

[9] BROOKS D.Signal Integrity Issues and Printed Circuit Board Design[M].Englewood Cliff,NJ:Prentice Hall,2003.

[10] OTT H W.Electromagnetic Compatibility Engineering[M].Hoboken,NJ:John Wiley & Sons,Inc.,2009.

[11] PAOLETTI U,HISAKADO T,WADA O.Analytical calculation of the point-to-point partial inductance of a perfect ground plane[C].IEEE Workshop on Signal Propagation on Interconnects,Genova,Italy,13-16 May,2007:217-220.