基于HMC830的低相噪低杂散频率源的设计

2011-10-09潘玉剑张晓发袁乃昌

潘玉剑,张晓发,袁乃昌

(国防科学技术大学 电子科学与工程学院,湖南 长沙 410073)

频率源可在雷达中用作本振信号,进行上下变频,也可以作为数据处理的采样时钟等,在雷达和移动通信领域有着重要的作用。相位噪声和杂散是衡量频率源的两个重要指标,大的相位噪声会造成时域的抖动,导致采样数据的信噪比恶化,而大的杂散会影响混频后信号的纯度,降低接收机灵敏度[1]。所以必须使这两者尽可能低。

频率源的设计目前主要有3种技术:直接频率合成、锁相频率合成、DDS(直接数字频率合成),而锁相频率合成具有高性价比的特点。文中使用了锁相频率合成这一技术,借助于HMC830锁相环芯片设计出了一种低相噪低杂散的频率源。实验结果表明该频率源的设计取得了理想的效果。

1 HMC830的主要性能和工作原理

HMC830是Hittite公司于2011年4月份新推出的一款宽带锁相环芯片,其内部集成了VCO,输出频率范围为25 MHz~3 GHz。内部鉴相器的鉴相频率可达100 MHz,高的鉴相频率一方面可以降低相噪,另一方面可以设计带宽较宽的低通滤波器,从而抑制VCO噪声和缩短锁定时间。芯片典型的输出功率为6 dBm,并且可以3 dB步进调节。该芯片可工作于整数

分频模式和小数分频模式,其中小数模式下典型分辨率为3 Hz,并且在小数分频模式下引入了精确频率模式,使得某些符合特定条件的频率可以精确获得。这款锁相环芯片有着业界领先的低相噪和低杂散,其典型相噪为-110 dBc/Hz。芯片尺寸为6×6 mm,并且在-40~+85℃都能保持良好的性能。

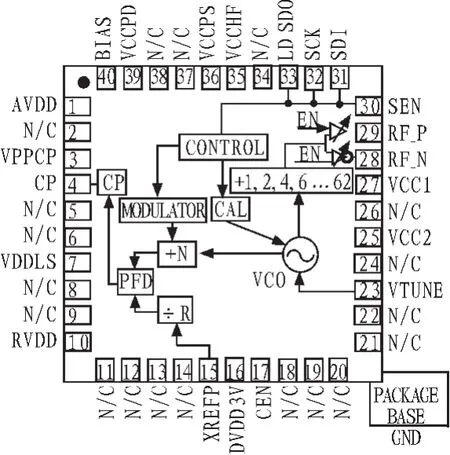

如图1所示为HMC830的功能框图,从图中可以看出该芯片的各个功能模块。

参考信号从XREFP管脚进去到参考支路R分频器、PFD鉴频鉴相器、CP电荷泵,从CP管脚出去,通过外部低通滤波器,再从VTUNE管脚进去到VCO压控振荡器,通过N分频器反馈到PFD鉴频鉴相器形成锁相环路。其中通过加到N分频器上的Δ∑调制器以提供小数分频的功能。VCO通过CAL模块获得校准的能力,最后VCO通过一可变系数的分频器将需要的频率输出,其中管脚RF_P和RF_N为差分输出。

外部控制信号通过SCK、SDI和SEN管脚以SPI总线的形式写进芯片内部的寄存器。管脚LD_SDO为多功能管脚,可以输出内部寄存器的值,也可以配置为锁定监测输出等信号,配置为锁定监测输出时,高电平表示环路已经锁定,低电平表示环路未锁定。CEN管脚为芯片使能,BIAS管脚需串联一电容到地,为偏置电路退耦。剩余管脚为各种电源输入以及空闲管脚。

图1 HMC830功能框图Fig.1 HMC830 functional diagram

该芯片输出频率为

其中,fref为参考信号频率,R为参考支路分频系数,Nint为反馈支路分频系数的整数部分,Nfrac为反馈支路分频系数的小数部分(当工作在整数模式时该值为0),k为从VCO出来的分频系数,根据芯片规定,只能为偶数。上述值均可以通过芯片内部寄存器控制。

2 频率源的实现

频率源的实现主要包括硬件电路的实现和软件的调试,即寄存器的操作。

2.1 供电设计

由图1可以看出,该芯片有多达10个电源管脚,为了使输出的相噪和杂散尽可能小,供电部分需认真考虑。首先VCO的5 V供电不能受干扰影响,不然会增加噪声,故单独供电。数字供电和模拟供电要分开,故将5 V模拟VPPCP和5 V数字VDDLS分开供电。3.3 V的数字DVDD3V和单片机的3.3 V使用一个电源,剩余的3.3 V使用一个电源。故需共使用5块稳压芯片。稳压芯片采用NS公司的低噪声LP3878和LP5900稳压芯片,LP3878输出5 V,LP5900输出3.3 V。

2.2 低通滤波器设计

HMC830由于内部集成了VCO,故使用很简单,只需设计1个外部滤波器就可以工作。低通滤波器在环路中处于鉴相器和VCO之间,可以滤除来自晶振的噪声,鉴相器本身的输出噪声和载频分量,以及减少鉴相频率的泄露,还可以滤除来自VCO的噪声,但最重要的是建立起环路的动态特性。

滤波器设计时其带宽需要折中考虑,带宽小了,VCO噪声影响大,而且环路锁定时间延长;带宽大了,晶振和鉴相器噪声影响大。本设计借助于Hittite PLL Design设计滤波器。该软件是Hittite公司推出的锁相环辅助设计软件,可以仿真锁相环的相噪特性、锁定时间等。通过仿真比较,在鉴相频率为100 MHz,输出频率为1.8 GHz时,设定滤波器为无源四阶低通滤波器,3 dB带宽为100 kHz,相位裕度为80度。滤波器电路图如图2所示,电路两端分别接CP管脚和VTUNE管脚。

图2 低通滤波器电路图Fig.2 Low pass filter circuit

2.3 整体硬件电路设计

HMC830为差分输出,现在只需要单端输出。虽然可以通过寄存器设置为单端输出,但考虑到最大功率输出,故采用差分到单端的转换器,该转换器采用的是M/A-COM公司的ETC1-1-13。进行寄存器读写采用的是SiLabs公司的C8051F300,该单片机体积小,利于小型化。另外HMC830外围电路可以参照Hittite给出的评估版电路图进行设计。如图3所示,为设计完成的频率源的实体电路。

图3 频率源实物图Fig.3 Actual photo of frequency source

2.4 软件编程

HMC830拥有17个PLL寄存器和7个VCO Subsystem寄存器[4]。PLL寄存器为Reg00h到Reg0Ah到Reg13h,其中包括分多个频系数寄存器、电荷泵寄存器、锁定监测寄存器等。VCOSubsystem寄存器为VCO_Reg00h到VCO_Reg06h,包括VCO分频系数设定、输出功率设定和信号输出设定等。对VCO Subsystem寄存器的操作是通过写PLL寄存器Reg05实现的。

对寄存器操作的一般顺序和说明如下:

1)写Reg02h寄存器,参考支路分频系数设定;

2)写Reg06h寄存器,该寄存器设置芯片工作于整数模式或小数模式;

3)写Reg07h寄存器,设置锁定监测的时间窗口。时间窗口设置过小会造成无法监测是否锁定;

4)写Reg09h寄存器,设置电荷泵电流和电荷泵偏移电流。小数模式下需设置电荷泵偏移电流,整数模式不需要。一般电荷泵电流越大,相噪越小;

5)写Reg0Ah,VCO自动校准设置,如设置为手动校准,可以实现捷变频;

6)写Reg0Bh,可以设置为防止锁相环跳周或滑变;

8)写Reg0Fh,LD_SDO管脚功能定义,一般配置为锁定监测输出;

9)写Reg05h,通过写该寄存器,间接写到VCO Subsystem的7个寄存器中,VCO_Reg00h最后写,以便芯片能正确对VCO自动校准;

10)写Reg03h和Reg04h,设定N分频器分频系数;

11)写Reg0Ch,在小数模式下可将某些频率精确输出。

数据写入采用的是SPI总线的形式,时序如图4所示。

图4 HMC830 SPI写时序图Fig.4 HMC830 SPI timing diagram of write

SCK为来自单片机的时钟信号,SCK第一个上升沿,SDI为高电平即开始写,SEN为写使能。SDI先输入6位寄存器地址信号,再输入24位数据,该24位数据就是对应地址寄存器的值,在每一个时钟上升沿数据被送入芯片,高位先进。

软件编程采用的是Silicon Laboratories IDE编程环境,C语言编写,最后下载到单片机执行。

3 测试结果及分析

测试时,鉴相频率设置为100 MHz,输出频率为1.8 GHz,为了获取尽可能小的相噪,芯片工作在整数模式下。参考频率由晶振提供。晶振采用的是Pascall公司的OCXO-3-100.0-1-0-0晶振,该晶振在偏移1 kHz处相噪为-158 dBc,典型输出功率为13 dBm,性能很好。

测试仪器为R&S公司的FSP-40频谱分析仪。测试结果如图5所示。

图5 测试结果Fig.5 Test result

图5(a)显示偏离载波1 kHz时相噪为-112.2 dBc/Hz;(b)中span为20 kHz显示在偏离10 kHz的相噪和偏离1 kHz时相比,几乎没有变化;(c)显示在偏离载波4.5 MHz处有杂散,杂散抑制度为-81 dBc;(d)中频谱仪span为250 MHz,在偏离载波100 MHz处有杂散,杂散抑制度为-75.6 dBc。这里的杂散是由于鉴相频率的泄露造成的。

4 结 论

笔者介绍了利用Hittite公司新推出的HMC830锁相环芯片设计低相噪低杂散的频率源的方法,使用该方法获得了良好的性能。这款芯片集成了VCO,具有设计简单,带宽大,性能优异的特点。其低相噪低杂散的优点能够很好地满足雷达和无线通信系统的要求,可替代市场同类产品。

[1]Analog Devices.锁相环常见问题解答 [EB/OL].(2011)[2011-08-19].http://www.analog.com/static/imported-files/zh/faqs/faq_PLL.pdf.

[2]Hittite Microwave Corporation.HMC830LP6GE Datasheet[EB/OL].(2011)[2011-08-19].http://www.hittite.com/content/documents/data_sheet/hmc830lp6g.pdf.

[3]Gardner, Floyd M..锁相环技术[M].姚剑清,译.北京:人民邮电出版社,2007.

[4]Hittite Microwave Corporation.HMC830LP6GE Eval.PCBSchematic[EB/OL].(2011)[2011-08-19].http://www.hittite.com/content/documents/eval_pcb_schematic/hmc830lp6g_eval_pcb_schematic.pdf.

[5]HittiteMicrowave Corporation. PLLs with Integrated VCORF_applications Production&Operating Guide[EB/OL].(2011)[2011-08-19].http://www.hittite.com/content/documents/operating_guide/pll_operating_guide_rf_vcos.pdf.

[6]Pascall Electronics.Ultra Low Noise VHF Crystal Oscillators[EB/OL].(2011)[2011-08-19].http://www.pascall.co.uk/pdfs/OCXOF%200710.pdf.