SDRAM控制器简易化设计

2011-10-09刘浩淼卞树檀朱守保

刘浩淼,卞树檀,朱守保

(第二炮兵工程学院 陕西 西安 710025)

SDRAM(Synchronous DRAM)是一种大容量快速读写存储器,因为其读写速度快、容量大、价格低廉,被广泛应用到音频、视频处理[1],数据采集,手持电子设备,雷达设备[2-3]等方面。这里使用SDRAM作为视频回波模拟器的回波数据高速缓存。

工控机PC104产生相关的模拟回波数据,以FPGA为中介将数据存储于I/Q两路SDRAM,并进行数据处理和数据输出操纵。由于回波脉冲有一定间隔,所以方案使用SDRAM以单字读写模式工作。

1 SDRAM特性

这里使用的SDRAM芯片是现代公司生产的HY57V561620型号芯片[4],拥有4个Bank,每个Bank容量为4,194,304×16 bit,B0~B1 是 2 根 Bank 选择线,A0~A12 的 13根地址线是行地址,RA0~RA12与列地址 CA0~CA8复用,D0~D15是16根数据线。地址线还可以对工作模式进行设置,A10控制预充电模式等功能。工作时钟能达到133 MHz(7.5 ns),是一种高速存储器。

采用Ateral公司飓风系列的EP1C6Q240芯片[5],对SDRAM控制器进行设计和实现。这种设计节省PCB空间,又增加了系统稳定性。FPGA有重复可编程的特征,使得SDRAM控制器可以方便地进行功能扩展。

2 SDRAM控制操作

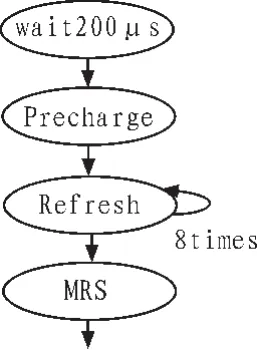

SDRAM 操作[3-4,6-7]包括初始化、读写、预充电和刷新等操作。初始化过程如下:上电等待200 μs,随后完成1次预充电,随后连续进行8次刷新操作,最后对模式寄存器进行设置。至此初始化完毕,SDRAM进入正常工作状态。

SDRAM芯片内部嵌有一个控制模块操作底层的存储单元,所以SDRAM工作状态是通过命令控制的。这些命令包括:预充电(Precharge)和自动预充电(Auto Precharge)、激活(Active)、读(Read)、写(Write)、自动刷新(Auto Refresh)和自刷新(Self Refresh)等。这里介绍几个相关的命令:刷新、预充电、激活、读写。

刷新是对SDRAM内的数据进行更新的操作。SDRAM存储单元实质是使用电容存储数据的,电容有漏电现象,所以需要每隔一段时间对其进行一次重新充电,芯片手册要求在每64 ms对内部所有行213=8 192进行一次刷新。刷新包括:自动刷新和自刷新。自刷新是在低功耗下芯片内部自动完成的。自动刷新是由控制器发起的,它必须在SDRAM没有激活行时才能进行,每次提出刷新命令芯片内部会通过行自加器对行数加一。对芯片刷新的实现方法有:集中刷新和定时刷新。由于模拟数据拥有固定时序,且没有大块的空闲时间,所以选择定时刷新。

预充电是对读写的行进行关闭操作。这里选择预充电而没有使用自动预充电,是出于掌握对时序的主动控制考虑,每次对全部模块进行预充电。

激活是对某一行的激活,这样才能对这一行进行读写操作。激活过程实质上是对行地址的锁存。

读写是在激活行上进行的,读写命令与列地址同时发出。可以突发读写,其长度是在初始化时通过对模式寄存器时设置实现。本设计使用突发读/单一写的模式,突发长度为1。

表1 命令真值表Tab.1 Command truth table

Mode Code设置为220 H,即突发读/单一写,读操作潜伏期为2 clk,顺序突发,突发长度为1。

3 模块化设计

SDRAM控制器采用模块化设计,可以进行功能模块化调试,便于设计。设计模块由4部分组成:状态控制机(State Control Machine)、命令控制机(Command Control Machine)、刷新机(Refresh Machine)、双向锁存器(Latch)。 控制器总体设计如1所示。

图1 SDRAM控制器结构框图Fig.1 SDRAM controller block diagram

3.1 状态控制器

状态控制机是控制模块的核心,它接收请求信号并通过状态分析控制其他模块的工作。状态控制机的设计主要通过设计状态机[8]来完成,SDRAM的控制状态主要分为:初始化、正常工作状态,状态图分别如图2、图3所示。

设备加电后状态控制机先进入初始化状态(Initial),依次完成:等待200 μs、预充电、8次刷新、模式寄存器设置(MRS)。随后进入正常工作状态,工作状态首先进入空闲状态(Idel),此时可能会有读写、刷新请求,因此需要制定一个优先级判别机制。使用SDRAM读取数据模拟脉冲回波,数据不能被中断,因此设置读写操作优先级高于刷新,这样刷新操作必须在空闲状态时才响应。如果当读写操作正在进行时刷新定时到来,可以设置一个标志记录变量,在完成读写操作进入空闲状态后再通过刷新标志变量来判定是否进入刷新状态(Refresh)。VerilogHDL部分实现程序如下:

图2 初始化状态图Fig.2 Initialization state diagram

图3 工作状态图Fig.3 Work state diagram

在读写操作状态(Read/Write)时,也不知道刷新请求会什么时候到来,所以采用每次回到空闲状态前进行一次对所有Bank的预充电(Precharge),为空闲状态的刷新做好准备。读写模式为单一读写,每次间隔与发射脉冲频率相关为500 ns,因此也有足够的时间完成预充电。状态控制机内部有两个分别控制读写的地址译码器,译码器自动递增读写的地址,因此设计了读写激活状态(Active Read/Active Write)来判断是激活读地址还是写地址。

状态控制机还输出dat脉冲信号去锁存双端口锁存器的数据,保证数据在操作时的稳定性。

3.2 命令控制器

状态控制机通过分析状态给出相应的命令信号,命令信号输入到命令控制机(Command Control Machine)。命令控制机输出端直接去控制SDRAM,对输入端命令信号的分析和输出以真值表1为依据,部分实现代码如下:

命令的译码操作主要是根据输入判断输出。在读写操作时,当读写完一行数据29×16=512×16 bit后需要对行地址加一,对列地址再加一为零,从下次开始读写下一行数据。

3.3 刷新机

刷新机(RefreshMachine)的实质是定时器,它以固定时间间隔输出刷新脉冲。芯片手册要求在64 ms内对所用行进行一次刷新,计算每次刷新的间隔为7812.5 ns,片上时钟频率为100 MHz,即每计781个数进行一次刷新,这里考虑到刷新的优先级低,可能被推迟执行,所以设置每记512个数提出一次刷新请求。

3.4 双向锁存器

PC104通过ISA总线和SDRAM通过数据线传输的数据是双向的,双向锁存器(Latch)[9]为满足数据流通提供了桥梁。数据的输入采用锁存机制,使输出端得到的数据稳定。DA[15..0]与PC104的数据总线相连;DB[15..0]与SDRAM的数据线相连;控制数据的流向,高电平时数据从DA[15..0]流向DB[15..0],反之则流向相反;dat脉冲对数据进行锁存。

4 实验分析

对各个模块进行联合实验的时序仿真如图4所示。

图4 控制器整体时序图Fig.4 Control the overall timing diagram

实验对控制器的初始化、写操作、读操作和刷新操作进行了仿真。实验结果表明SDRAM控制器对于各个操作都有正确的时序输出。在设计刷新操作实验时,特意同时给出读脉冲和刷新脉冲来测试控制器对优先级的判定能力,实验结果表明在控制器完成读操作并回到空闲状态后才去响应刷新请求正确地执行了优先级操纵。在时间轴上对每个响应操作的时间进行分析,发现操作响应存在一定的延时,这是硬件电路的性能和时钟频率所决定的,延时在可接受范围内。实验证明使用模块化设计SDRAM控制器的方法可行。

5 结束语

笔者从实际应用出发设计了单一长度读写的SDRAM控制器,使用了状态机和模块化设计,使设计简洁明了,简化了设计流程,并通过了时序仿真,可以被视频回波模拟器设计所使用。下一步要从设计上和时钟上做一些改进尽量减小操作响应的延时。

[1]王骞,丁铁夫.高速图像存储系统中SDRAM控制器的实现[J].液晶与显示,2006,21(1):48-52.

WANG Qian,DING Tie-fu.High-speedimagestorage system SDRAM controller implementation[J].Chinese Journal of Liquid Crystals and Display,2006,21(1):48-52.

[2]余卜一.基于磁盘阵列的雷达回波模拟器的研制[D]成都:电子科技大学,2006.

[3]郑哲,李加琪,吴嗣亮.引信体目标视频回波模拟器SDRAM控制器的FPGA设计[J]微电子学, 2005,35(1):102-104.

ZHENG Zhe, LI Jia-qi, WU Si-liang.FPGA design of SDRAM controllerforwirelessfuseebody-targetvideo frepuenty echo simulator[J].Microelectronics, 2005,35(1):102-104.

[4]Hynix公司.HY57V561620DataSheet[EB/OL].[2011-07-20].www.datasheet.com.

[5]altera公司.Cyclone FPGA Family[EB/OL][2011-07-12].www.altera.com.cn/literature.jsp.

[6]杨映辉.基于FPGA的SDRAM控制器设计及应用[D]兰州:兰州大学,2007.

[7]程方敏,黄启俊,向守坤,等.基于FPGA的高速SDRAM控制器的视频应用[J]应用设计,2009,36(7):22-24.

CHENG Fang-min, HUANG Qi-jun, XIANG Shou-kun,et al.The video application of high speed SDRAM controller based on FPGA[J].Application Design,2009,36(7):22-24.

[8]姚远,李辰.FPGA应用开发入门与典型实例[M].北京:人民邮电出版社,2010.

[9]杜志传,郑建立.基于CPLD/FPGA的VHDL语言电路优化设计[J].现代电子技术,2010(03):191-193.

DU Zhi-chuan,ZHENG Jian-li.Optimized design of circuits in VHDL based on CPLD/FPGA[J].Modern Electronics Technique,2010(03):191-193.