高速高密度PCB的RE问题

2011-10-09周胜海

周胜海,王 林

(信阳师范学院 物理与电子工程学院,河南 信阳 464000)

电子产品的RE (radiated emission)是指其PCB(printed circuit board)和电缆辐射出去的不需要的电磁场。作为一种外部噪声源,可能对附近的电子产品造成干扰。在许多国家电子产品的RE都是强制认证指标。对数字电子产品而言,PCB级RE有差模电流引起的差模RE和共模电流引起的共模RE两种。通常,共模RE较差模RE强得多(微安对毫安),且共模RE更难甚至不可能预测和控制。数字产品的发展趋势使RE问题更加严重和复杂[1]。所以,研究高速高密度PCB的RE问题具有实际意义。本文从高速高密度PCB设计的角度,总结PCB级RE的主要来源,分析PCB级RE的基本规律,给出PCB级RE的抑制对策。

1 PCB级RE的主要来源

对高速高密度PCB而言,PCB级RE的主要来源是集成电路(IC)、信号迹线(traces)和连接到 PCB 上的输入/输出(I/O)电缆产生的电磁辐射。引起RE的电流有差模电流和共模电流两种,前者是电路正常工作形成的,即信号电流(开关电流);后者是电路中的寄生效应(如不希望的电压降)引起的[2]。

通常,高速高密度PCB上的每一片数字IC都有相关的去耦电容(decoupling capacitors)。如图1所示,IC内部信号传输时,信号电流流动会形成两个电流环路,分别在IC和去耦电容上,环路面积为灰色区域,一般后者较前者小得多。这种电流环路相当于环形天线,向外辐射电磁场。

图1 IC引起的差模REFig.1 Differential-mode RE from an IC

信号迹线用于IC之间信号传输。信号迹线上有信号电流流过。信号迹线与信号电流返回的参考导体平面(reference conductor plane)一起构成电流环路。这种电流环路相当于环形天线,向外辐射电磁场。

连接到PCB上的I/O电缆产生的电磁辐射有3个来源。1)是差模电流(信号电流)引起的。对I/O电缆(如同轴电缆、双绞线、扁平电缆)而言,信号线对是平行又靠近的,因而差模电流产生的电磁辐射近似相消。需要进一步分析时,可将其等效为环形天线。2)是PCB的寄生效应引起的共模电流引起的[2-3]。如图2所示,PCB的地平面有阻抗,差模电流流过地阻抗时在逻辑地系统产生电压降VN(噪声电压)。I/O电缆一般以系统地为参考电位。所以,共模地电势驱动I/O电缆形成共模电流,I/O电缆相当于偶极天线或单极天线,向外辐射电磁场。3)是差分驱动器(differential drivers)的固有不平衡引起的共模电流引起的。差分驱动器和接收器(differential drivers and receivers)主要用于非常高速数字系统(如电信设备)[4]。所以,相对而言,第二个来源是主要的。

图2 I/O电缆产生的共模REFig.2 Common-mode RE from I/O cables

2 PCB级RE的天线理论

在天线理论中,一般认为环形天线周长或偶极天线长度小于λ/10(λ为信号波长)时是电小尺寸的,分别称为小环天线和短偶极天线[5],天线上各小段电流近似是均匀的。作为工程近似,通常以λ/4为判据,天线上各小段电流是同相的。

对IC和信号迹线产生RE的电流环路而言,一般都满足环路周长小于λ/4(1 GHz时为30 cm)的条件,所以通常等效成小环天线。根据天线理论可知,小环天线在自由空间的辐射场(远场)为[5]

式(1)中:E为电场强度,f为电流频率,Idm为差模电流大小,A为小环天线的环路面积,γ为天线至场点的距离,θ为场点与小环平面法线的夹角。

环路周长大于λ/4时,由于天线上各小段电流并非都是同相的,所以有些小段产生的RE对总RE的贡献是相减(削弱),而非相加(增强)。

虽然式(1)是从圆形小环天线导出的,但可用于其他形状的平面小环天线。因为小环天线的辐射强度与小环面积有关,而对小环形状不敏感[6]。

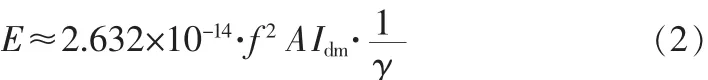

考虑到电子产品的RE认证测试关注最大辐射场强 (θ=90°)以及测试时地平面的反射,小环天线的辐射场的测量值可写为

式(2)是预测和抑制差模RE的理论依据。

地电位差驱动I/O电缆产生的共模辐射是共模辐射的主要来源。I/O电缆产生的共模辐射可等效成偶极天线或单极天线。

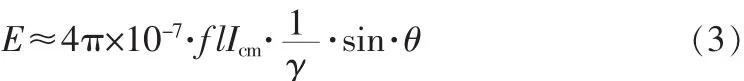

根据天线理论可知,短偶极天线(长度小于λ/4)在自由空间的辐射场(远场)为[5]

式中:E为电场强度,f为电流频率,Icm为共模电流大小,l为小偶极天线的环路长度,γ为天线至场点的距离,θ为场点与短偶极天线轴线的夹角。

若I/O电缆是连接到设备的另一块,则I/O电缆近似“顶帽”天线(top-hat antenna)[5],各小段电流近似是均匀的,很好地满足了式(3)的近似条件,误差很小。

考虑到电子产品的RE认证测试关注最大辐射场强 (θ=90°),短偶极天线的辐射场的测量值可写为

式(4)是预测和抑制共模RE的理论依据。

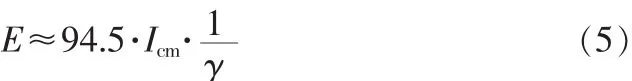

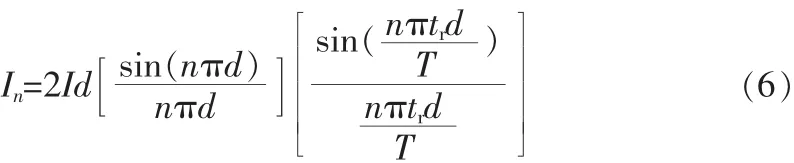

若I/O电缆长度大于λ/4,可对式(4)的结论修正而得到辐射场为

无穷大参考平面上面的单极天线的辐射场与偶极天线的辐射场相同,只是辐射场只存在于平面上半空间。

3 PCB级RE的基本规律

美国 FCC(FederalCommunicationsCommission)和国际电联CISPR (Interational Special Committee On Radio Interference)的相关标准中规定[7],B类产品RE限值为3 m距离处电场强度小于100 mV/m。

对于差模 RE,由式(2)可知,若 f=50 MHz、Idm=25 mA,则必须A≤1.8 cm2,否则RE超标。对于共模RE,由式(4)可知,若 f=50 MHz、l=1 m,则必须 Icm≤5 μA,否则 RE 超标。 可见,几微安的共模电流就可导致RE超标。实践中,几毫伏甚至更小的地平面电压降驱动I/O电缆就可能形成几微安的共模电流,进而导致RE超标。

取差模RE强度与共模RE强度相等,由式(2)和式(4)可得 Idm/Icm=4.8×107l/fA。 若 f=48 MHz、l=1 m、A=10 cm2,则Idm/Icm=1 000。可见,在高速高密度PCB上,共模RE往往起决定作用。

实际的数字信号可近似为对称的梯形波。设梯形波电流幅值为 I、周期为T、占空比为d、上升时间(下降时间)为 tr(通常tr≈T/10),则该梯形波的频谱中第n次谐波幅值为[7]

进一步近似占空比d=0.5(即50%)。由式(6)可知,一次谐波(基频)的幅值I1=0.64I,只有奇次谐波,频谱包络如图3所示,谐波幅值随频率的下降以1/πtr确定的频率点为界由20 dB/十倍频变为40 dB/十倍频。

由式(6)计算出各次谐波,依次代入式(2)计算出各次谐波的辐射,再计算出各次谐波的辐射之和,便得到数字信号产生的差模RE。类似地,利用式(4)可计算出数字信号产生的共模RE。

图3 梯形波的频谱包络Fig.3 Envelope of spectrum of a trapezoidal wave

结合图3所示的数字信号的频谱特点,考虑分别由式(2)和式(4)给出的差模RE和共模 RE正比于 f2和f,可得出差模RE和共模RE随f变化的包络如图4所示。可见,在高频段差模RE是主要的,在低频段共模RE是主要的。当tr=1~10 ns时,多数共模 RE出现在 30~300 MHz频段,多数差模RE出现在高于300 MHz频段。这也是诊断和抑制RE问题的重要依据。

图4 差模RE包络和共模RE包络Fig.4 Differential-modeandcommon-modeREenvelopeversusfrequency

由图3可见,数字信号中的高频分量主要取决于tr,tr越大高频分量越少;降低f1(基频)也可减少高频分量。然而,时钟频率越来越高,信号上升时间(下降时间)越来越短,是数字产品的必然趋势。所以,高速高密度PCB的RE逐步成为影响产品EMC(electromagnetic compatibility)的重要因素之一。

高速高密度PCB上的开关电流(△I噪声)可近似为等腰三角波或高斯波[8-9]。等腰三角波或高斯波的频谱可从相关文献查出或计算得到。开关电流引起的RE可用上述同样方法来估算。

4 PCB级RE的抑制

由PCB级RE的基本规律可见,从理论上讲,可以采取多种措施抑制差模RE和共模RE。但是,其中一些措施不是PCB设计者可以控制的。例如,理论上,降低时钟频率和增加信号上升时间(下降时间),对抑制差模RE和共模RE都很有效;实践中,这两个参数往往由产品性能要求而定,PCB设计者很难改变。PCB设计者只能参考PCB级RE的基本规律,结合PCB设计的具体情况,采取若干实用措施抑制RE,最终使产品的RE达到相关EMC标准的要求。

理论上,在PCB级抑制差模RE,降低频率或谐波成分、减小差模电流和减小环路面积都是可选措施。实践中,通常减小环路面积的措施是最实用的。这些措施达不到要求时,必须采取消除环路 (canceling loops)、 时钟展频 (spreadspectrum clock)等特殊措施[4]。

理论上,在PCB级抑制共模RE,降低频率或谐波成分、减小共模电流和减小I/O电缆长度都是可选措施。实践中,通常减小共模电流的措施是最实用的。降低地平面电压降,滤波I/O电缆,屏蔽I/O电缆,用共模扼流圈减小共模电流,用光电耦合器隔离I/O电缆与PCB地,都是常见的具体措施。

总之,对高速高密度PCB而言,在PCB级抑制RE可以说是个复杂的系统工程,需要从IC封装形式、元器件布局、PCB叠层、PCB布线、I/O电缆、机架(机箱)屏蔽等多个方面,进行综合设计。为保证设计可靠性和缩短设计周期,设计过程中恰当的建模、仿真、预测和测试是至关重要的。

可用于PCB级抑制RE的若干实用措施的详细资料可参考相关文献。

5 结束语

随着数字产品的时钟频率越来越高,信号上升时间(下降时间)越来越短,PCB的RE越来越严重,已逐步成为影响产品EMC的重要因素之一。PCB的RE有差模RE和共模RE两部分。差模RE主要由信号电流引起,共模RE主要由地平面电压降驱动I/O电缆形成的共模电流引起。通常,共模RE较差模RE严重得多(微安对毫安),且更难甚至不可能预测和控制。在PCB设计时,采取措施抑制RE,是必要的和有效的。在PCB级抑制RE的设计是个复杂的系统工程。

本文的讨论与结论对高速高密度PCB设计实践具有参考作用。

[1]Bogatin E.Signal and power integrity—simplified[M].2nd ed.Upper Saddle River (NJ,USA):Pearson Education,Inc.,2010:1-42.

[2]周胜海,王秀杰.电子系统共模噪声若干基本问题探讨 [J].信阳师范学院学报:自然科学版,2008,21(2):317-320.

ZHOU Sheng-hai,WANG Xiu-jie.Study on several elementary problems on common-mode noise in electronic systems[J].Joural of Xinyang Normal University:Natural Science Edition,2008,21(2):317-320.

[3]Henry W Ott.Electromagnetic compatibility engineering[M].Hoboken (NJ,USA):John Wiley&Sons,Inc.,2009:464-465,474-476.

[4]Caniggia S,Maradei F.Signal integrity and radiated emission of high-speed digital systems[M].Hoboken(NJ,USA):John Wiley&Sons,Ltd,2008: 441-446.

[5]Balanis C A.Antenna theory:analysis and design[M].3rd ed.Hoboken (NJ,USA):John Wiley&Sons,Inc.,2005:231-275,151-219.

[6]Kraus J D,Marhefka R J.Antennas[M].3rd ed.New York:McGraw-Hill Companies,Inc.,2002:212.

[7]Paul C C.Introduction to electromagnetic compatibility[M].2nd ed.Hoboken (NJ,USA):John Wiley&Sons,Inc. ,2006:49-85,91-166.

[8]周胜海.数字电路中△I噪声的产生与特点[J].电子技术应用,2006,32(8):99-101.

ZHOU Sheng-hai.Mechanism and features of△I Noise in digital circuits[J].Application of Electronic Technique,2006,32(8):99-101.

[9]周胜海,刘百超.数字电路中△I噪声的危害[J].电子技术应用,2006,32(10):118-121.

ZHOU Sheng-hai,LIU Bai-chao.Harmfulness of △I noise in digital circuits[J].Application of Electronic Technique,2006,32(10):118-121.