基于FPGA的OFDM调制器设计与实现

2011-09-19胡同花周维龙

胡同花,周维龙

(1.永州职业技术学院 湖南 永州 425100 2.湖南工业大学 电气与信息工程学院,湖南 株洲 412008)

OFDM系统的基本思想是把高速传输的数据流通过串并转换,分配到传输速率相对较低的若干个正交的子信道中进行传输。它通过降低每个子信道上的数据通信速率从而有效的降低由多径传输引起的码间干扰;并且OFDM系统与CDMA技术的结合使得OFDM系统在未来的移动通信中有着更广泛应用前景的可能性。

OFDM设计优点:1)无需线性均衡,从而避免了噪声的增强,而且由于它的符号间隔很长,对多径效应、脉冲噪声和快速衰落有较强的抵抗能力;2)由于子载波是相互正交的,所以频谱可以交叠使用,频谱利用率比普通的多载波系统要高得多。为了防止各子信道之间的串扰,OFDM要求子载波相互正交。利用这种正交性,接收机能正确分离开各个子数据流。为了保证子载波之间的正交性,OFDM要求各子载波在时间、频率上均保持同步,而且要求相邻子载波的频率间隔为OFDM的有效符号时间间隔T的倒数[1]。

1 实现原理[2]

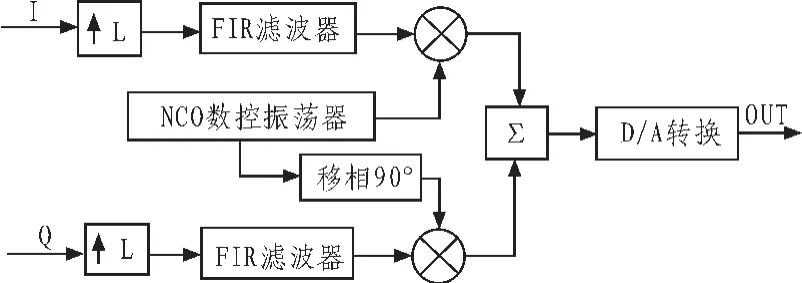

使用数字中频对信号进行I/Q调制可以精确地做到Q路的90°相移,在I/Q两路调制时没有幅度上的失真,所以在很大程度上克服了模拟I/Q调制的幅度和相位不平衡性。由于使用数字电路,克服了模拟混频电路非线性的影响,减少了非线性交调产生的谐波干扰。使用数字电路设计混频器、滤波器简化了硬件电路设计。由于FPGA的可编程性,使用FPGA实现数字中频,可以提高系统的可编程性。

在FPGA中OFDM的数字中频在发射部分使用平方根升余弦滤波器对基带信号滤波,以消除符号间干扰,滤波后的I/Q两路信号通过乘法器与NCO中的正弦和余弦中频载波相乘完成I/Q调制,最后两路信号相加通过D/A转换送入射频部分。如图1所示,其中关键的技术就是滤波器和数字压控振荡器的设计。本文祥细介绍了FIR滤波器和NCO的FPGA实现方法,并结合QuratusII给出了相应的仿真波形。

图1 OFDM调制原理图Fig.1 Diagram of OFDM modulation principle

2 FIR滤波器的FPGA实现

Altera提供的FIR Complier是一个结合Altera FPGA器件的 FIR Filter Core,DSP Builder与 FIR Compiler可以紧密结合起来。DSP Builder提供了一个FIR Core的应用环境和仿真验证环境。

2.1 建立模型文件

为了调用FIR IP Core,在Simulink环境中新建一个模型文件,放置Signal Compiler模块和FIR模块。启动Simulink的方法:打开Matlab,在主命令窗口直接键入Simulink,按回车即可。然后打开Altera DSP Builder模块,在MegaCore Functions调出fir_compiler_v7_0。

2.2 配置FIR滤波器核[2]

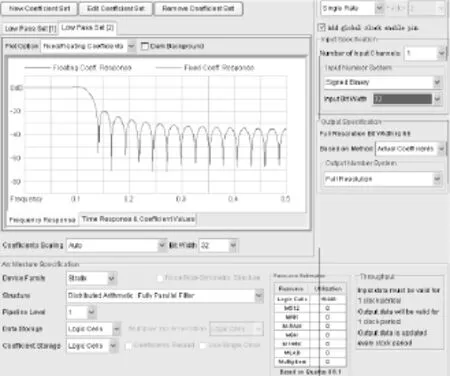

双击模型中的FIR模块,在弹出来的选择窗口中有:关于这个核(About this Core)、程序说明书(Documentation)、显示元件(Display Symbol)、步骤 1 确定参数(Step1:Parameterize)和步骤2生成 (Step2:Generate)等4个不同的选项。点击Step1,便打开了FIR滤波器核的参数设置窗口,如图2所示。

由图2可见,滤波器的系数精度为32位,器件为CycloneIII,结构为并行滤波,器结构选择了1级流水线,滤波器由LC逻辑宏单元构成,系数数据存于FPGA的M9K模块中,1个输入通道,32位有符号并行输入,全精度数据输出。设定后会直接显示滤波器的频率响应 (Frequency Response)或时域响应与系数值(Time Response&Coefficeient Values)。由其频率响应图可以看出,此FIR滤波器为低通滤波器。如果不符合设计要求,则可以通过对Edit Coefficient Set选项,对滤波器的进行重新配置。

图2 确定FIR滤波器系数Fig.2 Sure FIR filter coefficient

2.3 生成VHDL语言

完成FIR滤波器核配置后,便可得到设计好的滤波器,加入输入、输出信号,便形成了如图3所示电路。点击SignalCompiler,再选择 Analyze,选择 Sigle step compilation 中的Convert MDL to VHDL。就可以生成对应的VHDL语言。

图3 FIR滤波器编译电路图Fig.3 FIR filter compiler diagram

在QuartusII中打开编译后生成的fir.qpf工程文件,就可以得到滤波器的VHDL语言[3]。

3 NCO的实现

3.1 NCO的实现原理

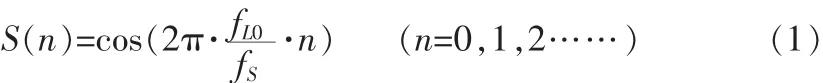

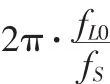

数控振荡器在数字中频中相对来说是比较复杂的,也是决定数字中频性能的主要因素之一,NCO的目标是产生一个理想的正弦波或余弦波,如式(1):

图4 NCO原理框图Fig.4 NCO principle diagram

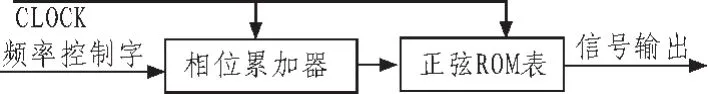

3.2 相位累加器的FPGA实现[5]

相位累加器由N位加法器与N位寄存器级联构成。每来一个时钟fc,加法器将频率控制字K与寄存器输出的累加相位数据相加,再把相加后的结果送至寄存器的数据输入端。相位累加器输出的数据就是合成信号的相位,当相位累加器累加到最大值时会产生一次溢出,完成一个周期的动作。溢出频率就是NCO输出的信号频率。可用VHDL语言实现相位累加器的设计,其主要代码如下:

8位相位累加器的仿真波形如图5所示。由波形图可以看出,当k=08时,在每一个有效脉冲的作用下,输出的数值比前一个输出的数值大8;当k=09时,输出的数值比前一个输出的数值大9;结果证明,该程序实现了相位的累加。

3.3 正弦ROM表的 FPGA实现

用相位累加器输出的数据作为波形存储器的取样地址,完成相位序列(相位码)向幅度序列(幅度码)的转换。这里用ROM构造一个查找表。N位的寻址ROM相当于把一个周期的正弦 波形信号离散成具有2N个幅值的序列,若波形ROM有D位数据位,则2N个幅值以D位二进制数值固化在FPGA的ROM中,按照给定地址的不同可以输出相应相位的正弦信号的幅度编码。

图5 8位相位累加器的仿真波形如图Fig.5 Diagram of showing the stimulated wave of 8 bit Phase-Accumulator

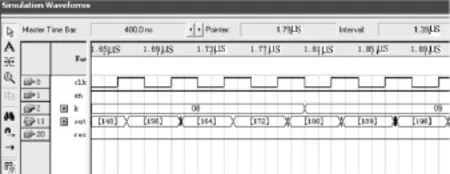

本文采用ROM表压缩结构,所以只需要产生1/4正弦波的数据,然后通过对相位和幅度进行适当的翻转便可得到整个周期的波形数据。查找表中的数据通过在matlab中编程获得,也可以通过C语言编写的正弦函数数据采样得到。matlab实现的1/4正弦波的仿真波形如图6所示。

图6 1/4正弦波形的仿真图Fig.6 Diagram of showing a quarter of the stimulated sin wave

由matlab程序生成的数据存放于sin_rom·coe文件中作为初始值文件。这样,通过QuartusII7.2中的IPcore将存放波形数据的sin_rom·coe文件加入工程,实现对ROM赋初始值。

把上述各部分所生的symbol在QuartusII7.2提供的BlockDiagram/SchematicFile中用 Graphic Editor编辑连接起来,就形成了图1的虚线所示的部分,编译后进行整体模块仿真,经过器件编程,可将整体模块程序烧写到合适的FPGA芯片中,再配以相应的D/A器件及其它外围电路,调试后即完成设计。

4 结束语

用FPGA来实现OFDM调制器,电路简单,设计灵活,便于修改和调试,可靠性高。另外,Altera公司的QuartusII7.2应用软件具有较强大的开放性和综合性,它可以利用其它各种EDA资源以及先进的设计方法,使其功能更加完善和强大。它可以实现从简单的接口电路设计到复杂的状态机,甚至“Sys-temon Chip”。它的可编程特性带来了电路设计的灵活性,缩短了产品的“Time ToMarket”。

[1]梁伟洋,冯祥.OFDM系统中自适应调制技术的研究[J]电子设计工程,2010(7):22-23.

LIANG Wei-yang FENG Xiang.OFDM on adaptive modulation technique in OFDM systems [J]Eelectronic Design Engineering,2010(7):22-23.

[2]王洪强.OFDM调制/解调的FPGA实现[J]通信与广播电视,2009(1):5-10.

WANG Hong-qiang.OFDM M odulation/demodulation with FPGA[J]Communication&Audio and Video,2009 (1):5-10.

[3]FIR Compiler User Guide. Altera Corporation[EB/OL].(2006-09)http://www.altera.com.cn.

[4]胡紫英,周维龙,聂辉.基于SOPC的FIR滤波器设计与实现[J].现代电子技术,2010,33(12):72-74.

HU Zi-ying,ZHOU Wei-long,NIE Hui.Design and realization ofFIR filterbased on SOPC [J]Modern Electronics Technique,2010,33(12):72-74.

[5]万福,周文伟,吕一希.OFDM系统数字中频的FPGA设计[J]通信与广播电视,2006(3):1-6.

WAN Fu,ZHOU Wen-wei,LU Yi-xi.Design of digital if based on FPGA in OFDM system [J].Communication&Audio and Video,2006(3):1-6.

[6]杨威,左月明,刘洋,等.利用FPGA实现DDS信号发生器的研究[J]山西农业大学学报:自然科学版,2007,27(3):329-332.

YANG Wei,ZUO Yue-ming,LIU Yang,et al.The research on using FPGA to realize DDS signal generator[J]Shanxi Agric.Univ.:Natural Science Edition,2007,27(3):329-332.