基于FPGA的宽带信号数字下变频设计与实现

2011-09-30康怀祺李宏波

邓 岚 康怀祺 李宏波 鄢 林

(电子科技大学 成都 611731)

1 引言

针对数字化雷达接收机采样前端,目前市面上已经出现了很多超高速多比特的A/D采样芯片,其采样速度可达到几个Gsps,而由此带来的问题就是数字信号处理器很难实时处理如此高速的数据流,数字下变频技术就显得至关重要。数字下变频的基本功能是将输入的宽带中频信号下变频为数字基带信号,并转换成较低的数据流。常规的数字下变频结构[1],采样后的数据通过与数控振荡NCO产生的解调信号相乘,得到两路正交的信号,同时实现频谱搬移,再由低通滤波器滤波后,进行多倍抽取,达到降速的效果。对于宽带信号,经过高速A/D采样后,数据速率可达几Gsps,由于常规的数字下变频方法,工作速率与ADC输出数据的速率一致,而FPGA器件无法达到如此高的运行速度,因此采用常规的数字下变频方法无法实现对宽带中频信号的处理。

为克服常规的数字下变频方法的缺陷,国外Jeffrey O.Coleman,James J.Alter和Dan Scholnik 等人提出了利用希尔伯特滤波器实现频谱搬移的方法[2]。信号通过带通滤波器滤去复信号,再通过Hilbert滤波器,将得到的信号下变频为零中频,最后进行D倍抽取降速。这种下变频方法虽然可以硬件实现,但是其资源占用量大,系统内部设计复杂。

本文为解决上述两个数字下变频结构的缺陷,提出了一种宽带中频信号的数字下变频方法,不仅可以实现对超高速率中频采样信号的处理,而且设计简单,其资源占用量低。

2 系统结构设计

本文设计的采集系统主要应用于某机载雷达的数据记录仪中,完成实时采集带宽为300MHz,载频为450MHz的雷达回波信号。根据带通采样定理:

式中,fs为采样速率;fH为信号的上限频率;fL为信号的下限频率;f0为信号的中心频率。只要n取满足fs≥2(fH-fL)的最大正整数(0,1,2,…),则采样所得到的信号采样值x(nTs)能准确确定原信号x(t)。为简化系统设计,在设计中选择n=0时的fs,即fs=1.8GHz。

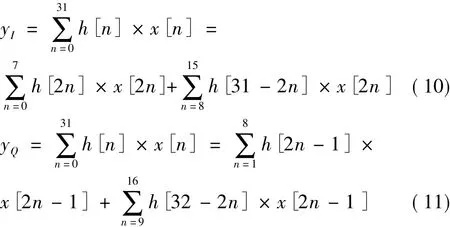

图1 数字下变频I路结构图

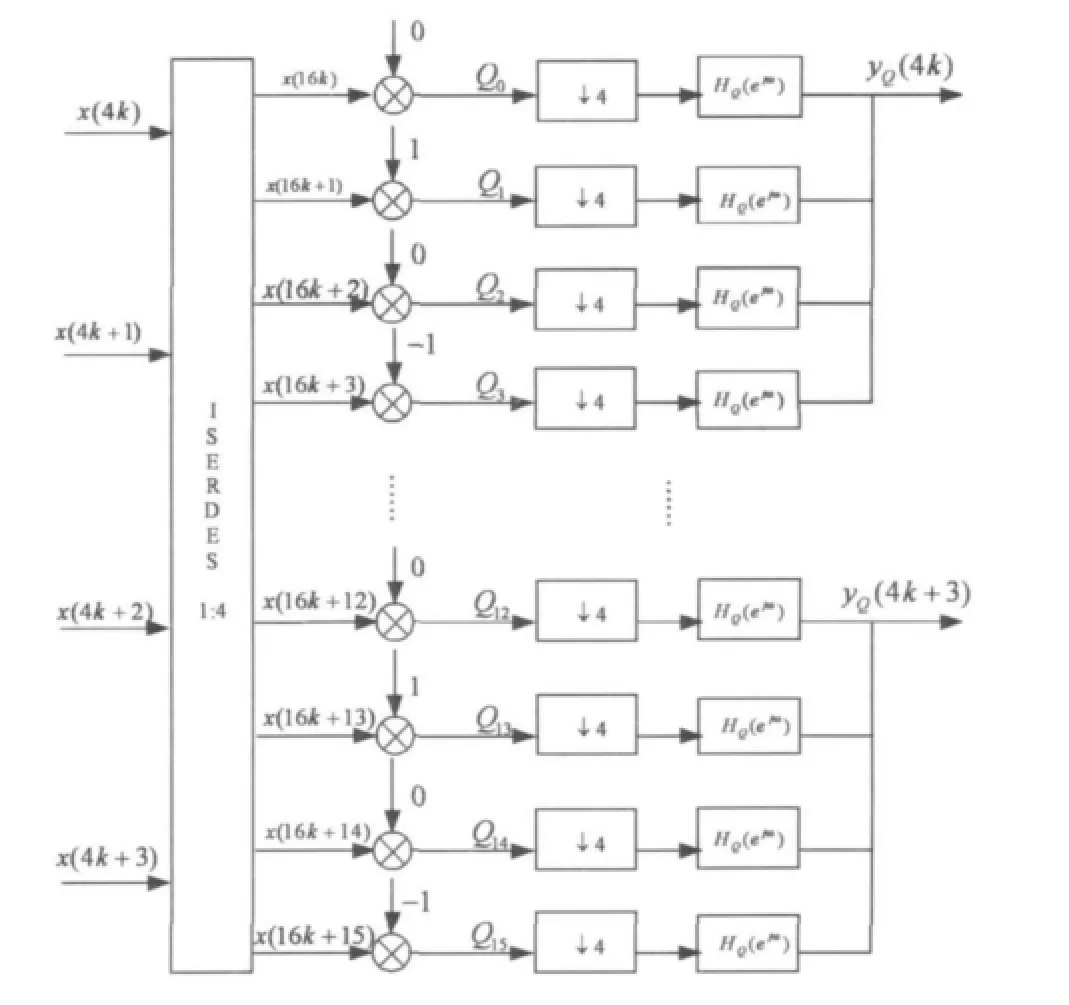

回波信号经过采样芯片处理,产生4路速率为450Msps的8bit信号,且依时序排列。经过串并转换模块,形成16路速率为112.5Msps的并行信号,送入到DDC模块中进行数字下变频处理。首先将16路信号通过基于多相滤波的数字正交变换,实现宽带中频信号下变频为基带信号,产生正交的I、Q两路数据[3];其次利用多相滤波结构和分布式算法实现4倍抽取,产生8路相互正交的I信号和Q信号,其数据率为112.5Msps存入到存储芯片中。其数字下变频I路结构框图如图1所示,Q路结构框图如图2所示。

图2 数字下变频Q路结构图

2.1 并行化模块

在并行化处理过程中,需将4路速率为450Msps的信号降速为16路速率为112.5Msps的信号。因此每一路数据按照1路串行输入,4路并行输出,即1:4进行转换。在此模块中,采用FPGA中串转并原语ISERDES[4],对每路信号进行1:4的串并转换。由于在ISERDES原语中,需要4分频的时钟信号,因此还需利用DCM模块,对输入的时钟信号进行4分频处理。

2.2 正交化模块

4路信号经过并行化模块处理,得到的16路112.5MHz的8bit信号并依时序排列。

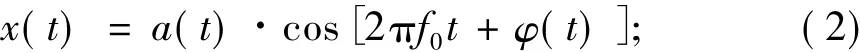

设输入信号为:

其中a(t)为输入信号的包络,φ(t)为信号的相位,载频f0=450MHz,对其进行采样频率为fs=4f0带通采样,得到采样序列为:

分别为x[n]的同相分量和正交分量(零中频信号),根据基于多相滤波的正交变换[5],得到:

为简化系统设计,对多相滤波正交化结构进行改进。将2倍抽取置于乘法器之后,与抽取滤波模块中的D倍抽取结构相结合,形成2D倍抽取。其改进的多相滤波正交变换为:将xI[2n+1]和xQ[2n]都置零,则x[n]的同相分量和正交分量可以转换为下式:

2.3 抽取滤波模块

16路数据经过正交化处理后,形成的16路I和16路 Q数据,每路数据的传输速率仍为112.5Msps。由于传输给存储芯片时,只有4路I通道和4路Q通道,即每路通道数据率为450Msps,其速率过高,后续模块无法处理,则需要对形成的正交16路I和16路Q数据进行降速处理。在本文中选择抽取率D=2,即实现2D=4倍抽取,就可以满足系统要求,最后产生需要存储的4路I数据和4路Q数据,其每路数据速率为112.5MHz。

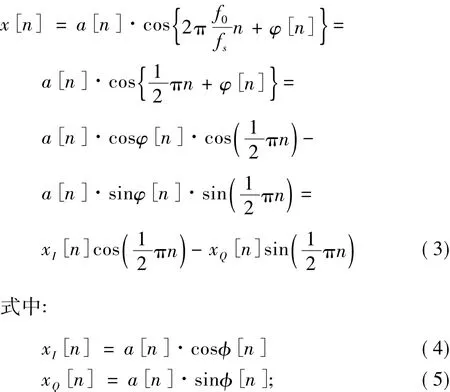

在抽取滤波过程中,首先应对信号进行低通滤波,再进行抽取。根据Noble恒等式知,可先进行抽取,再进行滤波,更简化滤波器的设计[6]。本文采用32阶的FIR滤波器实现4倍抽取,即h[n]=h[-n]。而为了节省资源消耗,提高运算速率,采用了多相滤波和改进型的DA算法[7]进行实现。

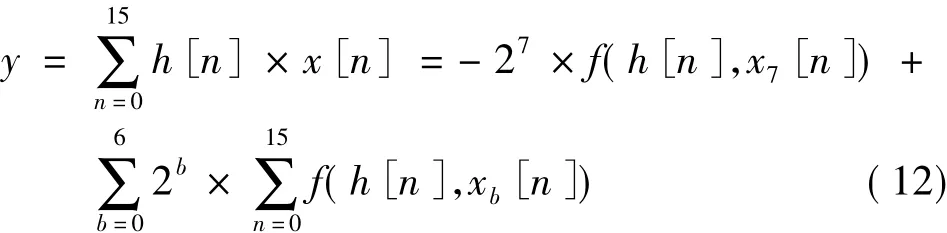

利用Matlab软件的FDAtool工具,生成一个32阶的第I类FIR等纹波低通滤波器,将其系数导出。由于 N=32(即 n=0,1,2,…,31),在进行抽取滤波时,只需要利用 h[n],n=0,1,2,…,15 这 16 个系数进行处理。

信号经过多相滤波正交化后,得到:

利用DA算法实现抽取滤波过程,其DA算法的数学表达式为:

为了节省资源占用量,采用图3所示结构,同时采用块ROM和分布式ROM,利用位移寄存器的方式,产生8个地址,进入到LUT中查表,得到相应结果。将得到结果通过流水线寄存器相加,得到最后滤波结果。

图3 DA算法结构图

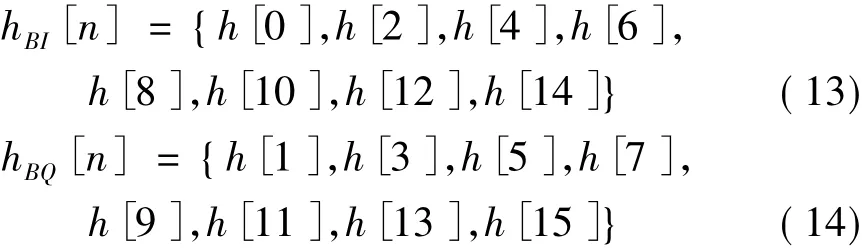

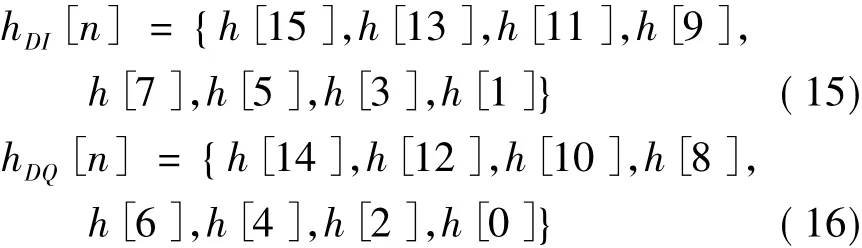

在块ROM中,组成LUT的系数为:

在分布式ROM中,组成LUT的系数为:

此四组系数,分别由Matlab生成.coe文件导入到对应ROM中,生成所需查找表。由于LUT中,略去了 xBI[n]=0 和xBQ[n]=0 的处理,且 xBI[n]和xBQ[n]的零点都是间隔出现,则此处便完成了一次2倍抽取的过程。

根据上述LUT的设计,本系统的滤波器等效于一个16阶滤波器,因此4倍抽取多相滤波结构中,每一个子结构只有16个输入。而在LUT设计时,已实现了2倍抽取,所以在多相滤波抽取过程中,只需完成2倍抽取即可。

为更容易理解,将 xI[n]和xQ[n]中为0的序列去掉,得到新的序列 x'I[n]和x'Q[n]。

在实现2倍抽取过程中,只需要选x'I[n]和x'Q[n]作为滤波器输入便可实现2倍抽取。

3 实验结果及分析

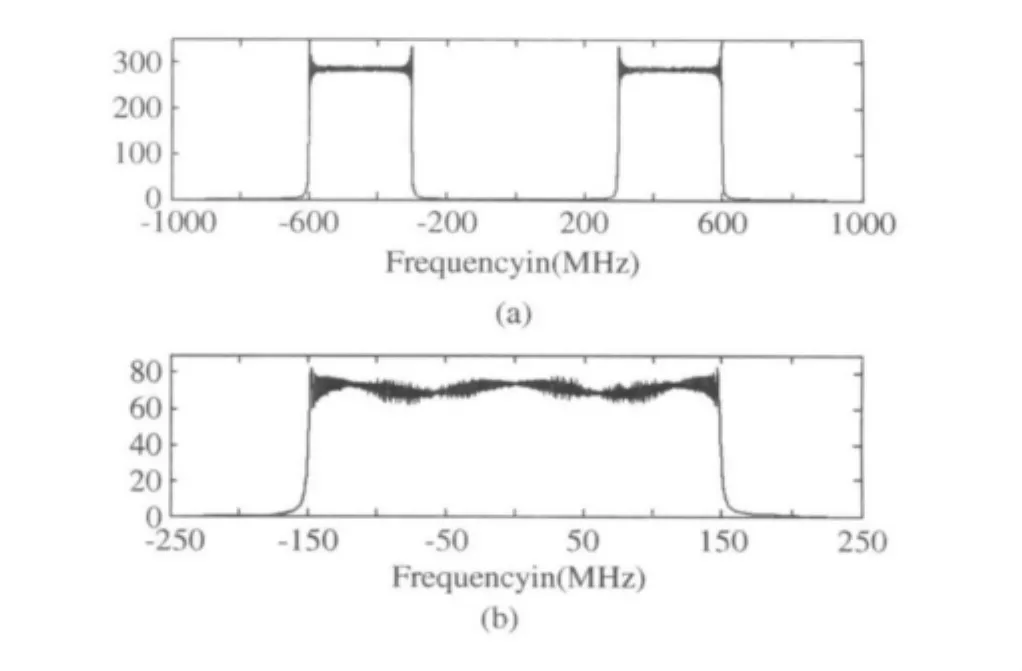

选择Chirp信号模拟雷达中频信号,利用Matlab对上述设计进行仿真,得到如图4-a所示的chirp信号频谱图和如图4-b所示的基带信号频谱图。

图4 a为chirp信号频谱图,b为基带信号频谱图

在FPGA实现过程中,首先将chirp信号数据转换成.txt的数据文本文件,以此作为数据激励源,送入到FPGA中,利用Xilinx公司的xc4vlx25ff668-12 FPGA来实现数字下变频,采用ISE10.1综合软件对其进行综合,采用Modelsim6.3c仿真软件对其进行仿真[7]。数字下变频的时序仿真图如图5所示。FPGA系统资源占用率如表1所示。由此可见,采用FPGA模块化设计能够较好地对宽带中频信号进行下变频处理,采用分布式算法,节省了资源消耗,更利于系统设计。

表1 数字下变频资源利用表

图5 数字下变频时序仿真图

4 结论

本设计通过对超高速中频采样信号进行并行处理,形成多路并行数据,降低了每路数据的运算速度,满足下变频处理中FPGA对工作频率的要求。通过基于多相滤波的正交化处理,简化了下变频结构,节省了很大的资源占用量,提高了运算速度。除此之外,利用多相滤波结构和改进后的DA算法,完成了对中频信号的多倍抽取,实现了下变频结构中降低基带信号传输速率的要求。仿真及实验结果表明:本设计不仅在软件上得到了实现,在硬件上,采用FPGA实现数字下变频延时短,最高系统主频可达到206MHz,输入输出时间延迟为7个时钟周期,满足实时处理要求。

[1]刘红文.基于FPGA的软件无线电数字接收机的研究[D].武汉:武汉理工大学,2009.

[2]Jeffrey O.Coleman,James J.Alter,Dan Scholnik.FPGA Architecture for gigahertz-sampling wideband if-to-baseband conversion[C].2000 Int’l Conf.on Signal Processing Applications and Technology Dallas TX.2000,10.

[3]Wenhao Zhang,Jun Wang,Yuxi Zhang,Wei Li.Design of RF digital receiver based on FPGA[C].International Communication Conference on Wireless Mobile and Computing,2009:699-702.

[4]Vitex-4 User Guide.Xilinx.2007,www.xilinx.com .

[5]杨小牛,娄才义,徐建良.软件无线电技术与应用[M].北京:北京理工大学出版社,2010:87-91.

[6]周浩.宽带数字接收机关键技术研究[D].南京:南京理工大学,2008.

[7]Hua-Ming Liu,Guang-Jun Li,Bo Yan,Qiang Li.A 100MHz digital down converter with modified filter for wideband software-defined radios[C].2010 International Conference on Electronics and Information Engineering,2010:V2540-V2544.