雷达信标源中频处理模块的设计与实现

2011-09-26焦光龙陈小雷

薛 明,焦光龙,陈小雷

(空军工程大学导弹学院,陕西三原713800)

0 引言

现代雷达系统的日益复杂,使得在设计和调试雷达系统的过程中,不可避免地需要雷达的回波信号。当前雷达信号模拟技术逐步发展成熟,成为雷达技术的一个重要分支,雷达信号模拟器的研制更成为国内外研究领域的热门方向[1,2]。雷达信标源是基于数字射频存储器(DRFM)的全硬件回波信号模拟系统,是随着DRFM技术的发展成熟而不断发展起来的。DRFM技术能够将接收到的雷达射频信号相位(频率)实时存储起来,经过一段时间延迟与变换后,再向雷达发射回去,且能保证信号良好的相参性[3]。因此雷达信标源能通过建立雷达系统模型,灵活地产生蕴含多种雷达目标信息的回波信号,满足雷达系统设计、开发和测试的需要。

中频信号处理模块是雷达信标源设计的核心,而中频部分处理主要是对信号距离时延特性和速度多普勒特性的模拟。这里在对雷达信标源介绍的基础上,提出了中频信号处理模块的总体方案,并采用FPGA器件对距离时延和多普勒移频模块进行了设计实现,最后进行了仿真测试及结果分析。

1 雷达信标源

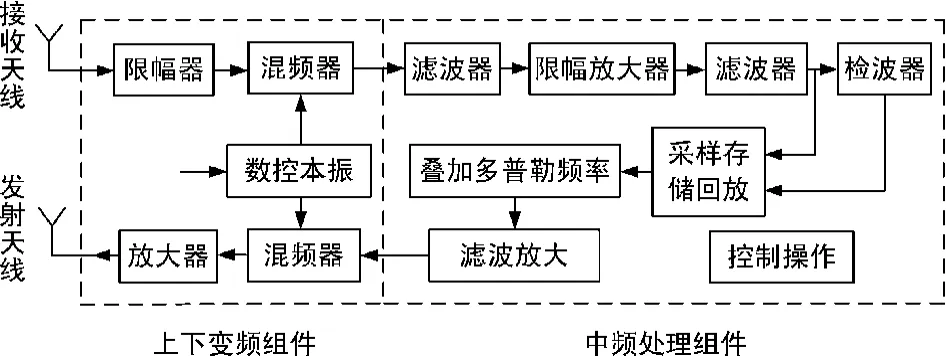

雷达信标源是以DRFM为核心部件的,基于DRFM的相参雷达信标源主要由接收变频器、频率合成器、多普勒频率调制器和发射变频器等设备组成。相参信标主要完成以下功能:①接收经过空间传输的由雷达送出的脉冲连续波信号,并对接收到的信号进行转发放大;②在对接收到的信号进行转发放大时,根据要求加入多普勒频率。雷达信标源的结构框图如图1所示,主要由收发单元、本振频率源、上下变频组件、数字射频存储器和电调衰减器等控制单元组成。在上下变频组件部分,对天线接收的高频信号进行限幅、衰减,与数控本振进行混频,下变频到中频;中频处理结束后,再上变频到高频并经由天线发射出去。中频处理部分,对中频模拟信号进行A/D采样,存储在存储器中,进行距离延时控制,读出存储的数据,紧接着对读出的数字信号进行多普勒移频调制,实现速度特性的模拟,然后滤波放大后输出。

图1 雷达信标源结构

2 中频处理模块的总体方案

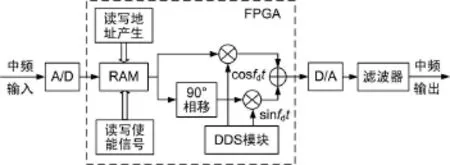

中频信号处理模块用于对下变频后的中频信号进行相关处理,其核心模块主要有距离时延模块和多普勒移频调制模块。中频信号的处理主要是由可编程逻辑器件FPGA进行设计实现的,中频信号处理模块设计实现的总体方案如图 2所示。所用FPGA器件是Cyclone II系列的EP2C70F62C67。

图2 中频信号处理模块总体方案

距离时延模块采用FPGA内部集成的双口RAM模块进行实现,该方法既充分利用了FPGA的灵活方便、可编程性强的特点,同时也利用了RAM模块的功能实现方便、读写控制简单等优点。

多普勒频移模块设计采用了数字正交调制的单边带调制技术[4,5],调制信号采用DDS技术[6]实现,且此DDS模块以及单边带调制模块均由FPGA器件来实现。在这里多普勒移频模块是利用基于DSP Builder工具进行开发设计的。

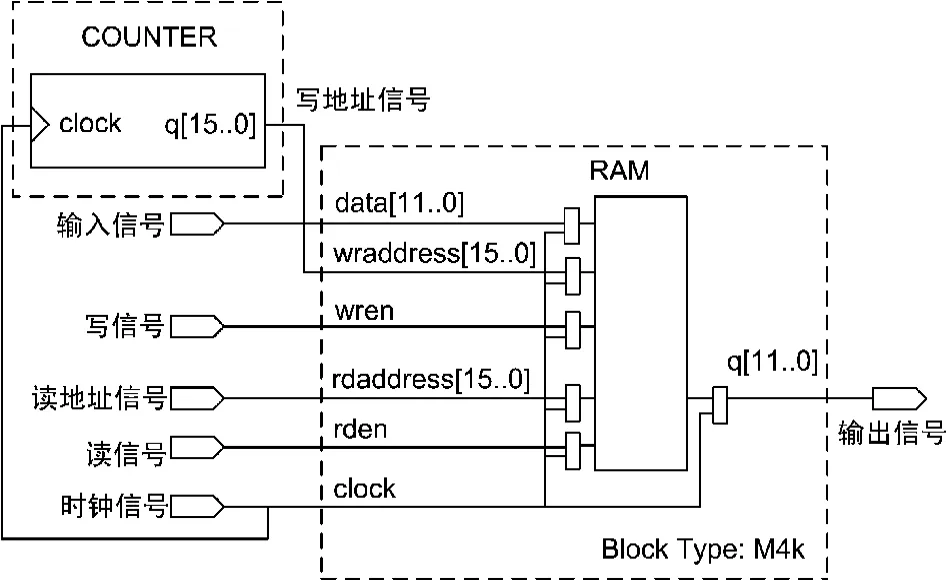

3 距离时延设计

采用FPGA的Quartus II 7.2开发软件的原理图法对距离时延模块进行设计。采用双口RAM进行时延模块的设计时,模块上电后就立即触发写使能信号进行信号的写入存储,当读使能端的计数器计到所需延迟的值时,就会触发读使能信号为高电平,进行存储信息的读取。RAM的读使能信号的控制原理为将需要延时的数值存入寄存器74273b中,设定的延时值与计数器的值在比较器中进行比较,当计数值大于等于延时值时,输出高电平到读使能端,进行存储数据的读取。

因此通过向FPGA中的延迟寄存器写入相应的延时量,就可以产生不同的延迟时间,满足了对不同目标距离的模拟。同时可以通过编程的方式来实时改变延时寄存器中的值,模拟出目标不同的距离变化,这样就大大提高了延时控制的灵活性。时延模块的硬件顶层设计电路实现如图3所示。

图3 时延模块顶层设计电路实现

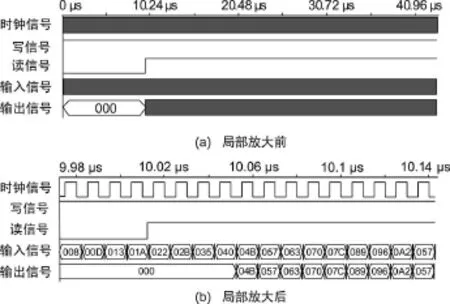

考虑到在设计实现与实际雷达信号进行对接测试是既不方便且不现实的,因此在仿真测试时,都采用了基于ROM模块写入的载波数据波形进行仿真测试。下面对设计的时延模块进行仿真设计,输入波形数据为ROM写入的单周期为64个点的12 bit正弦连续波信号,仿真时间设为500 μ s,时钟周期为10 ns,写使能信号置为高电平,延时100个时钟周期,可得其时序仿真波形如图4所示。

图4 时延模块的仿真波形图

4 多普勒移频设计

DSP Builder是一个面向DSP开发的系统级(或算法级)设计工具,它架构在多个软件工具之上,并把系统级(算法仿真建模)和RTL(硬件实现)2个涉及领域的设计工具连接起来,都放在MATLAB/Simulink图形设计平台上,而将QuartusⅡ作为底层设计工具置于后台,提供了 QuartusⅡ软件和MATLAB/Simulink工具之间的接口,最大程度地发挥了各种工具的优势[7]。

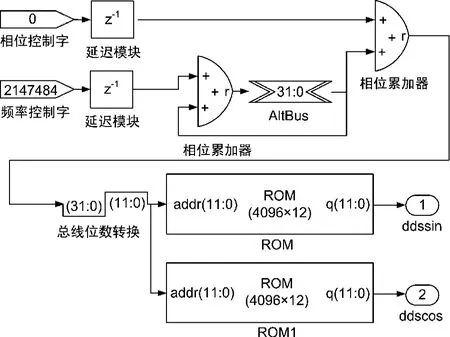

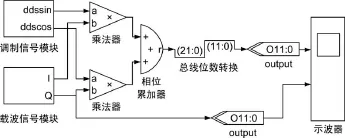

多普勒移频调制模块就是基于DSP Builder进行设计开发的,调制信号采用了DDS技术来产生,并通过对DDS调制信号模块频率控制字的改变来进行多普勒频移的变化,在这里测试信号也是通过DDS产生。DDS模块如图5所示,移频调制模块实现的DSP Builder模型如图6所示,其中output输出的是经多普勒移频调制后的信号,output1输出的是测试载波信号,用于与调制后的信号进行对比。

图5 DDS模块的DSP Builder模型

图6 移频调制模块的DSP Builder模型

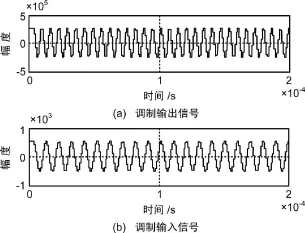

将综合后生成的网表文件通过USB-Blaster下载电缆,以JTAG模式的方式下载到FPGA器件中,从而完成了器件的配置,然后进行硬件在回路仿真(hardware-in-the-loop,HIL)。HIL仿真在开发周期早期就将硬件与软件合并起来进行测试,这样可以及早地发现问题,从而降低了成本[8]。这里系统时钟为10 ns,Simulink仿真采样时间为1 μ s,中频测试信号的频率为100 kHz,调制信号频率为50 kHz,相应的频率控制字分别为2147484、4294968,仿真结束时间为0.2 ms。运用DSP Builder中的HIL模块,测试结果在MATLAB/Simulink的示波器中观察波形如图7所示,结果达到了设计要求。

图7 移频调制模块HIL仿真波形

5 结束语

采用FPGA器件设计实现了雷达信标源的中频信号处理模块,并进行了仿真测试与分析,结果表明了设计实现的中频信号处理模块功能良好,达到了预期的设计要求,可以满足实际中的应用需求。此外,要想使雷达信标源获得更广泛的应用,中频信号处理模块一方面还需在模拟目标信号类型的多样性、目标运动特性变化以及功能拓展应用上进行更深层次的研究与探索,另一方面还有待于高性能指标的DRFM器件的不断发展与应用实现,其中提高器件瞬时带宽和量化精度是DRFM技术发展的2个重要方向。

[1]候建刚,王 越.一种基于TMS320C6416的实时雷达信号模拟器设计[J].火控雷达技术,2004(6):63-66.

[2]高梅国.雷达模拟器信号处理器[J].北京理工大学学报,1999(5):608-611.

[3]罗 进.基于DRFM的欺骗干扰与雷达目标模拟实现[J].电子工程师,2007(4):1-2,6.

[4]严家明,李 瑾,胡楚锋.基于正交混频的数字下变频技术研究[J].计算机测量与控制,2009,17(1):200-202.

[5]崔丽珍,杜普选.基于正交性移频信号技术方案的研究[J].微计算机信息,2008,24(7):234-235.

[6]张 涛,陈 亮.现代 DDS的研究进展与概述[J].电子科技,2008(3):73-77.

[7]卢 毅,赖 杰.基于Altera FPGA/CPLD的电子系统设计及工程实践[M].北京:人民邮电出版社,2009.

[8]潘 松,黄继业,王国栋.现代DSP技术[M].西安:西安电子科技大学出版社,2003.