一种综合模块化航空电子系统时间同步方法

2011-09-25

(中国西南电子技术研究所,成都 610036)

1 引 言

随着微电子和超大规模集成电路的发展,新一代航空电子系统正逐渐朝着综合模块化(IMA)的方向发展[1]。IMA系统的一个典型特征就是系统通常由标准的机架和通用模块组成,机架接收来自机载传感器的各种数据,通过背板总线或线缆分发到各个模块进行处理。由于各模块间的数据关联性越来越强,实时性要求越来越高,因此对系统时间同步提出了新的挑战[2]。

目前关于计算机网络时间同步研究的文献较多。文献[3]介绍了计算机网络中硬件时间同步和软件时间同步方法,重点对网络时间协议(NTP)的工作原理进行了介绍,使用该协议可以在局域网上实现亚毫秒级的时间同步精度;文献[4]对时间同步网的网络结构进行了介绍,指出应该采用主从同步方式,上级的时间服务器通过NTP等协议将时间传递给下级的时间服务器或工作站来完成时间同步;文献[5]提出了一种基于锁相环的时间同步调度机制和算法;文献[6]提出了一种时间同步精度的测试方法,其主要原理是利用GPS标准秒脉冲与被测秒脉冲进行对比,以获得时钟误差。

IMA系统实质上就是一个小型化的分布式计算机网络,拓扑结构和层次关系相对特殊,虽然目前没有文献专门针对IMA系统提出时间同步方法,但可以借鉴常规计算机网络的设计思路。本文针对典型的IMA系统,结合软件授时、硬件同步的原理,从工程实现角度出发,提出了一种系统时间同步方法,并对同步误差进行了分析。

2 系统时间同步方法

2.1 硬件环境

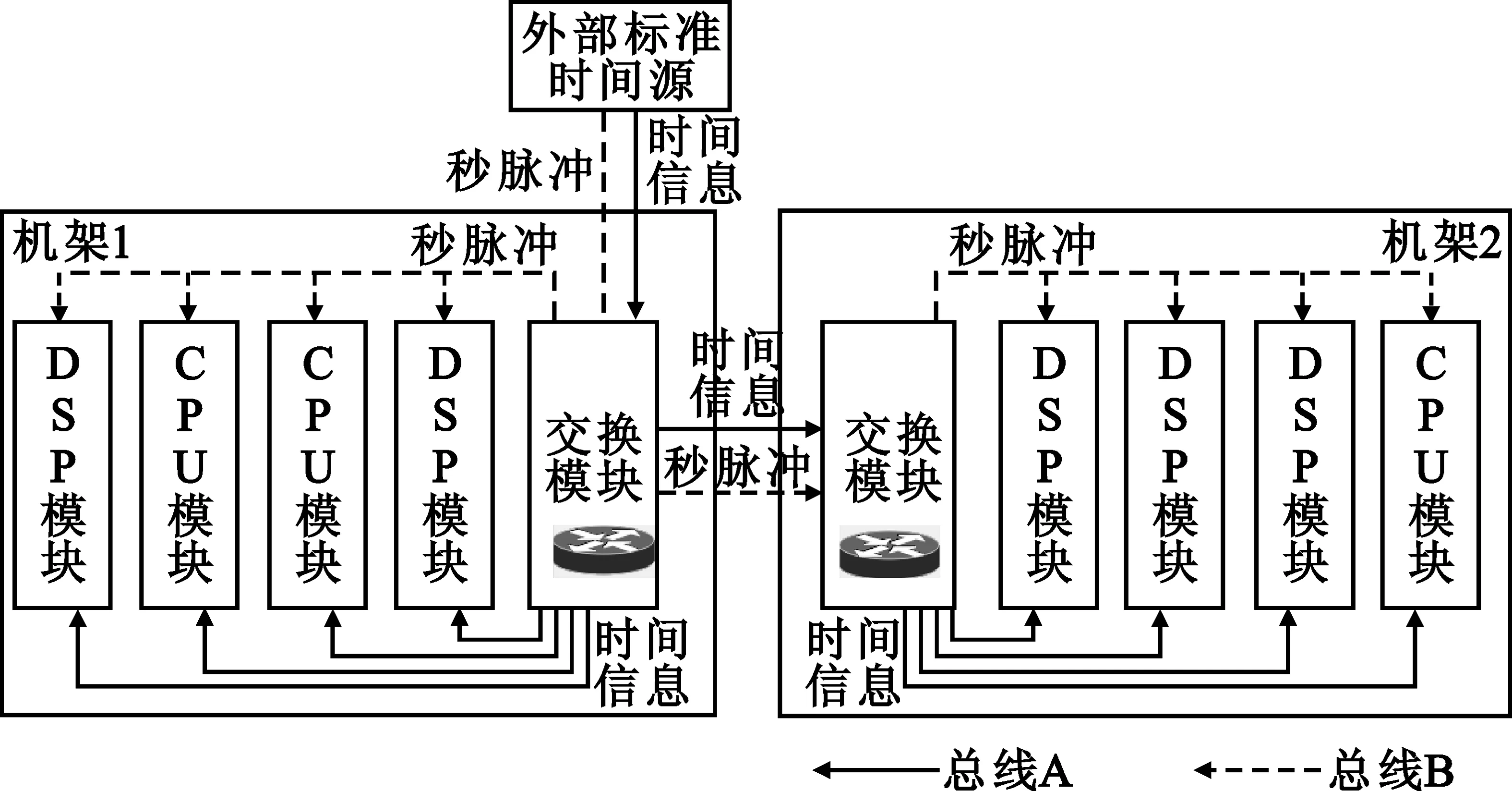

本文提出的时间同步方法适用于通用的IMA系统,为便于描述,对硬件环境进行了适当简化,仅保留了与时间同步相关的部分,系统组成如图1所示。具体描述如下:

(1)系统共包含两个处理机架,需要时间同步的模块为各个机架内所有DSP模块和CPU模块;

(2)机架内各处理模块通过本机架内的交换模块实现星型结构互连,机架间的数据互联由交换模块实现;

(3)系统外部具备一个标准的时间源,周期产生时间信息和秒脉冲,时间信息的发布与秒脉冲的上升沿保持一致;

(4)系统包含总线A(包交换结构总线)和总线B(离散线)两种总线,总线A的传输延迟小于1 s。

图1 时间同步硬件环境Fig.1 Hardware environment for time synchronization

2.2 同步原理

系统时间同步的原理采用“软件授时、硬件同步”的机制,其基本思想是通过总线A(交换网络)分发时间信息,通过总线B(离散线)发送秒脉冲,并利用秒脉冲触发同步。时间同步的基本流程描述如下:

(1)秒脉冲分发

外部标准时间源通过总线B连续不间断地向机架1中的交换模块输出秒脉冲,信号电平可根据具体工程项目选取。交换模块一方面在本机架内向所有DSP模块和CPU模块发送秒脉冲;另一方面,通过总线B将秒脉冲输出到机架2中的交换模块上,并通过该模块将秒脉冲分发到机架内的DSP模块和CPU模块。

(2)时间信息分发

外部标准时间源周期性地利用总线A将时间信息包发给机架1和机架2中的交换模块,并通过它们将时间信息包分发到两个机架内的所有DSP和CPU模块。时间包发送周期为1 s,消息描述格式及时间精度与具体的外部时间源相关,这里假设时间源输出的时间精度为1 ms。

由于总线A的传输延迟小于1 s(这也是目前市面上大多数总线能够达到的技术指标),因此从外部标准时间源开始发送时间包起,1 s内所有DSP和CPU模块均能获取到时间包。外部标准时间源在每个输出秒脉冲的上升沿分发时间信息,因此各模块每次收到的时间信息包刚好相差1 000 ms。

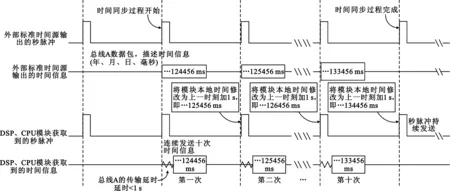

(3)时间同步过程

系统设计师通常将时间同步过程安排在系统初始化过程中,时间同步过程开始时,外部标准时间源在网络A上连续广播n次时间信息,共耗时ns。各个DSP和CPU模块在收到时间信息后,在下一个秒脉冲的上升沿到来时进行本地时间同步,将本地时间进行如下校正:

当前本地时间=最近一次获取到的时间+1 s

(1)

由于时间信息将连续发布n次,因此各模块会连续n次校正本地时间,系统时间同步的时序图如图2所示(这里假设n=10)。

图2 时间同步时序图Fig.2 Schedule of time synchronization

各模块通过连续n次校正本地时钟就完成了一次系统时间同步的过程。随后,外部标准时间源将不再向网络上发布时间信息,但秒脉冲信号将持续不间断地向各个DSP和CPU模块发送,各模块自身进行本地时间的向前计数。在系统工作过程中,若有新的模块上电加入系统,或系统产生了复位,则可根据具体应用需求,设计智能检测机制,使时间同步过程重新启动,以保证在任意时刻,所有模块均处于同步状态。

3 同步误差分析

不管采用哪种时间同步方法,均会不同程度地产生一定的同步误差。影响时间同步误差的因素较多,归结起来可以分为传输延迟、同步处理延迟、守时误差等。本文解决的主要问题就是在时间同步过程完成的时刻,尽量使系统中所有DSP、CPU模块的本地时间保持一致,且尽可能地接近当前外部标准时间源输出的绝对时间。为分析时间同步误差,这里将同步过程的时序图进行放大(如图3所示),并以机架内任意两个模块X和Y为例进行分析。

图3 同步误差分析Fig.3 Synchronization error analysis

外部标准时间源在每个秒脉冲输出的上升沿,通过总线网络A发出时间信息包,由于模块X和模块Y分布在机架的不同插槽内,因此秒脉冲和时间包会分别经过一定的传输延时到达这两个模块。在图3中以模块X为例,其中:

t-X1:外部标准时间源最后一次发出时间包,到模块X收到该包之间的时间间隔。该值主要是由总线网络A的传输延迟组成,即与时间包经过的物理路径长度和交换节点数成正比。以一个经过8跳的百兆以太网路径为例,数据包通过一个交换芯片的延迟为2 μs,信号的传输时间为33 ns(以10 m长的路径为例),加上收发节点的软件开销,得出t-X1的典型值在30~50 μs之间。

t-X2:外部标准时间源发出的秒脉冲到达模块X的传输延迟。该值主要与秒脉冲信号的传输时间、秒脉冲在传输过程中的波形失真,以及路径上经过的接口电路的处理时间有关。忽略由于秒脉冲波形失真造成的脉冲沿偏移,以10 m的物理路径为例,秒脉冲信号的传输时间为33 ns,接口芯片的处理延迟为4 μs(以RS422芯片为例),得出t-X2的典型值在4 μs左右。

t-X3:模块X在秒脉冲上升沿开始修改本地时间,到完成该操作的处理时间。t-X3与模块的本地处理器的处理速度、完成的指令数有关。以CPU模块为例(PowerPC处理器+VxWorks操作系统),从秒脉冲上升沿触发中断,进入时间同步处理线程,再到完成本地时间修改并返回,整个处理时间t-X3的典型值在20 μs左右。

3.1 相对误差

相对误差定义为:在一次时间同步过程完成的时刻(即所有模块均完成本地时间修订时),各模块本地时间之间两两差的最大值。在图3中,以模块X和Y为例,这两个模块在完成时间同步时的本地时间相差为ΔT-XY,从图中可以看到:

ΔT-XY=|t-X2+t-X3-t-Y2-t-Y3|

(2)

相对误差=max(ΔT-XY),X∈∀,Y∈∀

(3)

通过上式发现,采用本文的同步方法可以有效屏蔽总线网络A的传输时延和抖动给系统时间同步带来的影响。相对误差仅与秒脉冲到达各个模块的时间差,以及各模块的本地处理时间差有关,与时间包的传输延迟无关,即与t-X1和t-Y1无关。

假设秒脉冲到达各模块物理路径的距离差最大为10 m,因此秒脉冲传输造成的时间误差为33 ns,该值基本可以忽略不计,这样,相对误差就主要与各模块完成本地时间修正所耗费的处理时间差有关,通过试验测量发现相对误差的典型值一般都小于20 μs。

3.2 绝对误差

绝对误差定义为:在一次时间同步过程完成的时刻(即所有模块均完成本地时间修订时),所有模块的本地时间与当前外部标准时间源输出的绝对时间之间差值的最大值。在图3中,以模块Y为例,ΔT-Y就是模块Y在完成同步时,与当前绝对时间之间的误差。从图中可以看到:

ΔT-Y=t-Y2+t-Y3

(4)

绝对误差=max(ΔT-Y),Y∈∀

(5)

通过上式发现,绝对误差与秒脉冲的传输时间和模块的本地处理时间有关,同样与总线网络A的传输延时无关。假设秒脉冲传输的最长距离为30 m,同时处理器的本地处理时间最长为20 μs,因此得出绝对误差的典型值为25 μs。

3.3 守时误差

系统在完成时间同步后,各模块将在本地对时间进行守时,维护本地时间的向前计数。本地时间记数的设计通常有两种方法:一是采用传统的实时时钟电路(RTC)设计,通过各个模块自身的RTC进行时间记数;二是在每个模块上设计计数器电路,通过外部统一的高速脉冲激励,由计数器进行时间记数。

方法一的守时精度与各个模块的RTC有关,但该方法不需要增加额外的系统走线,实现简单,模块掉电后时间信息可以保存,比较适合前期模块的独立开发调试,另外可以通过对RTC进行统一设计来减小守时误差;方法二的守时精度较高,但需要增加额外的系统走线,对模块的设计提出了新的要求,同时模块掉电后时间信息不易保存,不适合模块的独立开发调试。对于方法一和方法二,可根据实际工程需求进行选择。

4 结 论

本文针对典型的IMA系统,提出了一种时间同步方法,该方法采用“软件授时、硬件同步”的设计思路,可有效屏蔽总线网络的传输时延对同步误差造成的影响。通过对同步误差的分析可以发现,该方法实现的同步精度达到了微秒级,且实现简单,可直接应用于工程化的IMA系统时间同步设计。

参考文献:

[1] STANAG 4626,Final Draft of Proposed Standards for Software:Part I Architecture[S].

[2] STANAG 4626,Final Draft of Proposed Standards for Software:PartVI Guidelines for System Issues[S].

[3] 李伟章. 时钟同步与时间同步网[J].数字通信世界,2008(7):75-79.

LI Wei-zhang. Time synchronization and Time synchronization network[J]. Digital Communication World, 2008(7):75-79. (in Chinese)

[4] 袁海. 时间同步网的原理及其应用[J]. 电信技术,2001(10):69-71.

YUAN Hai. The Principle and Application of Time synchronization network[J]. Telecommunication Technology,2001(10):69-71. (in Chinese)

[5] REN F Y. The time synchronization scheme and algorithm based on phase lock loop[J].Journal of Software, 2007, 18(2):372-380.

[6] 季锋,卜澎. 时间同步系统的测试方法[J]. 电力系统通信, 2003,24(7): 40-41.

JI Feng,BU Peng. Measurement of Time synchronization System [J]. Telecommunication for Electric Power System, 2003,24(7):40-41. (in Chinese)