基于SOA-MZI差分相位法的全光异或逻辑门研究

2011-09-21呙道静

呙道静

(国电南京自动化股份有限公司,南京 210031)

基于SOA-MZI差分相位法的全光异或逻辑门研究

呙道静

(国电南京自动化股份有限公司,南京 210031)

建立了基于SOA-MZI结构差分相位法的全光异或逻辑门模型,实现了20 Gbit/s信号的全光异或逻辑运算。运算结果表明:输出脉冲信号的宽度主要是由延迟时间t决定的。采用差分相位法,可以减弱输出脉冲的码型效应,避免出现“拖尾”现象。

半导体光放大器;马赫—曾德尔干涉仪;差分相位法;异或

全光信号处理技术以其高速率、大容量、高带宽的处理信号能力,已经成为下一代全光网络中不可或缺的关键技术[1]。作为全光信息处理中的关键器件,全光逻辑器件的引入克服了光网络“电子瓶颈”的限制、扩大了光网络的工作容量需求、有效地降低了信号噪声和串扰积累问题,从而提高了光网络的传输速率。全光逻辑门是实现光计算功能的关键器件,可以用于伪随机码的产生、全光逻辑运算电路、全光奇偶校验、全光包地址和载荷的分离、标签交换等[2-3]。异或逻辑门在全光网络中应用很广泛,且半导体光放大器(SOA)具有功耗低、稳定性高、结构简单紧凑、易于集成等特点,非常有利于实现全光逻辑异或门运算。现有的全光逻辑异或门实现方案主要是利用SOA的非线性效应,如交叉增益调制(XGM)效应、交叉相位调制(XPM)效应以及四波混频(FWM)效应等。此外,利用SOA组成的干涉仪结构也可以实现全光逻辑异或门,其中干涉仪有基于光纤或波导的结构[4-5]。

本文建立了基于半导体光放大器的马赫—曾德尔干涉仪(SOA-MZI)结构的全光异或逻辑门理论模型,利用差分相位法数值实现了异或逻辑运算,并分析了逻辑门的性能。

1 理论模型

图1 基于SOA-MZI结构的全光异或门方案

图1给出了基于SOA-MZI结构差分相位法的全光逻辑异或门模型[6]。2个 SOA对称平行置于干涉仪2臂上。1个3 dB耦合器将1束波长为λ3的连续探测光分解成2束光

并同时注入到干涉仪两臂的SOA中。2束波长为λ1和λ2的高强度调制信号光A和B分别经过3 dB耦合器分解成两束光 A1、A2和 B1、B2。B2延迟

时间t后与A1在端口1耦合并注入到SOA1中,A2延迟相同的时间t后与B1在端口2耦合并注入到SOA2中,信号光A和B的输入功率均大于SOA的最大线性输入功率,在经过SOA时,信号光会对探测光进行相位调制,使得探测光在经过SOA后就会携带上信号光的信息。

在耦合器4中,经过相位调制的2路探测光发生干涉,并由相位调制转化成振幅调制,从而完成2路信号光的异或运算,异或信号的输出功率为[7-8]:

其中,Pin(t)是输入探测光功率,G1(t)、G2(t)、φ1(t)、φ2(t)分别为探测光经过MZI上下2臂的SOA后所产生的增益变化和非线性相移。

2路探测光干涉结果如下:当A和B信号不同时,例如信号A为“1”,信号B为“0”时,φ1的波峰先到达,并打开一个时间窗口,称为开关窗口。t秒后,φ2的波峰到达,φ1和φ2的相位差消失,窗口也随之关闭,此时会产生一个波长为λ3的脉冲,即输出异或结果为“1”。当A和B信号相同(A=B=0或A=B=1)时,φ1和φ2相位相同,开关窗口处于关闭状态,此时输出异或结果为“0”。

2 数值模拟及分析

在模拟计算时,本文选取输入的2路信号光A、B的速率均为20 Gbit/s,脉冲宽度(FWHM)为1.25 ps的1阶高斯脉冲模拟信号。探测光波长λ3=1 550 nm,信号光A的波长λ1=1 570 nm,信号光B的波长λ2=1 575 nm;探测光输入功率Pp=-10 dBm,信号光输入功率Ps=0 dBm,输入信号的半高全宽(FWHM)为5 ps,延迟时间t为4 ps。其他仿真中所要用到的基本参数值参考文献[9]。

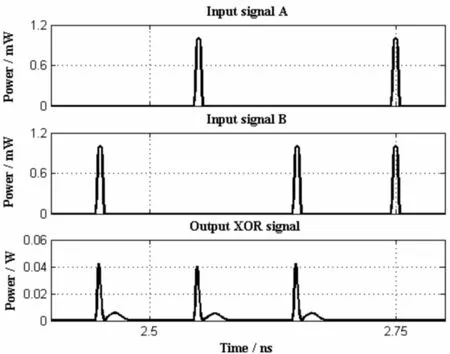

图2 20 Gbit/s信号差分相位法全光异或门仿真结果

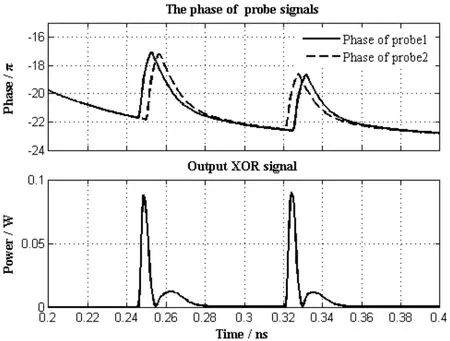

图3 探测光相位变化对比(上)和对应的输出脉冲(下)

本文采用RZ码,一般地,在同一个时隙内如果信号A和信号B相同,则探测光的相位变化φ1和φ2应该相等,输出的功率应该趋于“0”,但是从图2和图3给出的结果可知,每一个“1”脉冲过后,都会紧跟着出现一个很小的脉冲,这时虽然信号A和B相同,但是输出信号并不为“0”。其原因可以如下理解:每一个输入信号波形的影响和增益的不能完全恢复,这使得探测光的相位变化φ1和φ2之间存在差异,从而导致开关窗口重新打开。

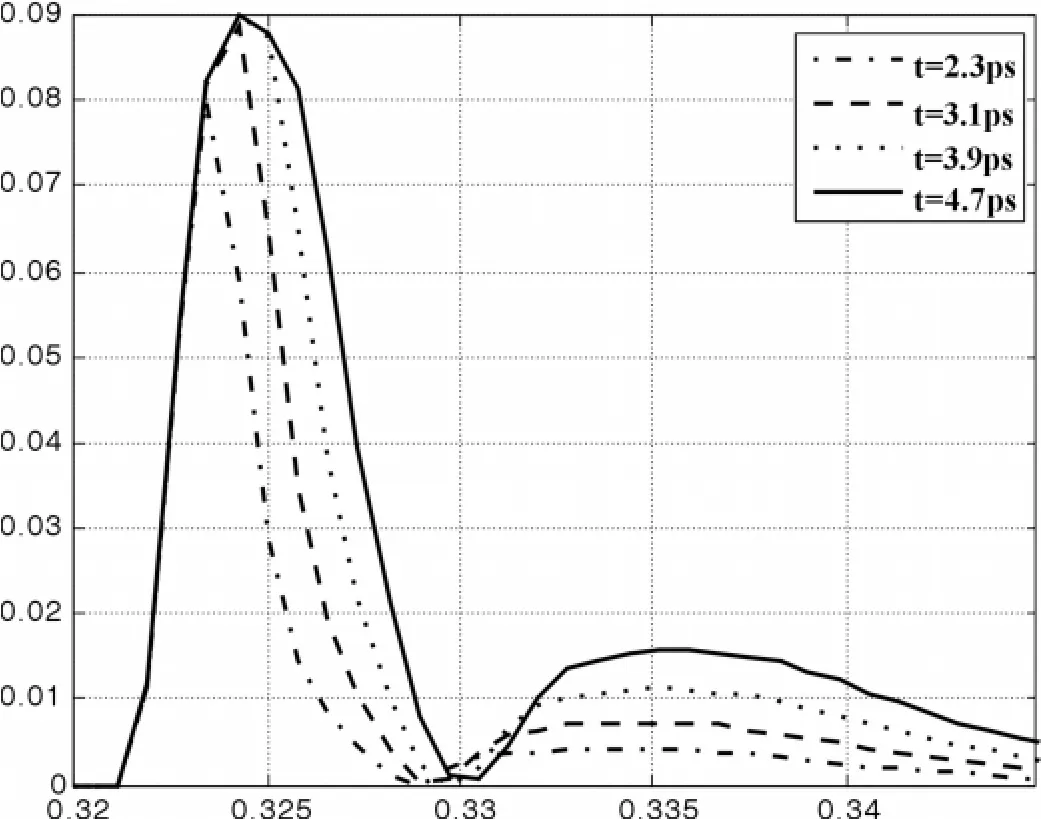

图4给出了差分相位法异或输出脉冲随不同延迟时间t的变化曲线。如该图所示,随着延迟时间t的增大,这种由于输入信号波形的影响和增益的不完全恢复所导致的输出“0”信号功率较高的现象越来越明显,此现象在一定程度上降低了输出信号的消光比。此外,在延迟时间t的增大过程中,输出脉冲的宽度也逐渐增大。而且还可以看出,在不同的延迟时间t下,输出脉冲均不会出现后延展宽,说明差分相位法克服了半导体光放大器中载流子恢复时间对高速信号处理的限制。

图4 延迟时间与输出脉冲的关系

3 结论

本文实现了基于SOA-MZI结构差分相位法的20 Gbit/s信号的全光异或逻辑运算,并分析了不同延迟时间对输出脉冲宽度的影响。数值结果表明,差分相位法可以克服半导体光放大器中载流子恢复时间对高速信号处理的限制;延迟时间的变化对输出信号的脉冲宽度有很大的影响,延迟时间的增大,使得输出脉冲的宽度逐渐增大,并在一定程度上降低了输出信号的消光比。

[1]叶小华,张民,叶培大.全光异或逻辑门技术[J].激光与红外,2007,37(7):56-57.

[2]HALL K L,RAUSCHENBACH K A.All-optical bit pattern generation and matching[J].IEEE Electronics Letters,1996,32(13):1214-1215.

[3]POUSTIE A J,BLOW K J,MANNING R J.All-optical pseudorandom number generator[J].Optics Communications,1999,159(4):208-214.

[4]FJELDE T.Demonstration of 20Gbit/s All-optical logic XOR in integrated SOA-based interferometric wavelength converter[J].IEEE Electronics Letters,2000,36(22):1863-1864.

[5]ROBINSON B S.40Gbit/s All-optical XOR using a fiber-based folded ultrafast nonlinear interferometer[C].OFC'02,Anahein,USA,2002(3):561-563.

[6]KIM J Y,KANG J M,KIM T Y,et al.10 Gbit/s all-optical composite logic gates with XOR,NOR,OR and NAND functions using SOA-MZI structures[J].IEEE Electronics Letters,2006,42(5):278-279.

[7]洪伟,黄德修.半导体光放大器静态增益饱和特性的理论研究[J].华中科技大学学报,2002,30(9):67-69.

[8]邹龙方.基于线性光放大器的波长转换和光逻辑异或门研究[D].成都:西南交通大学,2005:33-52.

[9]赵婵.基于SOA的全光逻辑门[D].武汉:华中科技大学,2006:54-56.

All-Optical XOR Logic Gate Using Differential Phase Scheme Based on SOA-MZI

GUO Daojing

(Guodian Nanjing Automation Co.,Ltd.,Nanjing 210031,China)

A scheme for all-optical XOR logic gate using differential phase method has been investigated.The experimental results for XOR gate at 20Gbit/s are presented.The results show that the width of output pulse is mainly determined by delay time.The pattern effect of the output pulse can be weakened,and the“tail”phenomenon can be avoided by using differential phase scheme.

Semiconductor Optical Amplifier;Mach-Zehnder Interferometer;Differential Phase Scheme;XOR

TN248.4

A

1008-5440(2011)03-0033-03

2011-06-30

呙道静(1976-),男(汉族),湖北襄阳人,工程师,本科,研究方向:电力系统自动化。