密勒调制副载波编解码器的FPGA实现

2011-09-19陈杨张红雨张鹏程

陈杨,张红雨,张鹏程

(电子科技大学 电子工程学院,四川 成都 611731)

随着射频识别 (Radio Frequency Identification,RFID)技术的快速发展与广泛运用,超高频射频识别系统由于具有读写速度快、读写距离远、存储容量大、防碰撞能力强的优点,已经在物流等领域得到了广泛的应用。在超高频读写器设计中,为实现标签与阅读器之间的数据通信,一般采用负载调制方式进行无线通信。在阅读器和标签发射端,在进行负载调制前,需要选用一种编码方式对发送的数据进行编码。在基于ISO/IEC18000-6C协议的超高频读写器设计中,阅读器到标签的数据编码方式采用PIE编码,标签到阅读器的数据编码方式采用FM0编码或密勒调制副载波序列编码 (M=2,4,8)[1]。在分析密勒调制副载波序列特点的基础上,提出一种密勒调制副载波的编解码方式,并且给出了在FPGA中的实现方法。

1 编码设计

密勒码中带有丰富的时钟信号,且抗干扰能力强,因此是射频无线通信中数据传输的优选码型。密勒编码规则规定[2]:在相邻两个数据0之间发生电平跳变,在数据1的中间也将发生电平跳变。从规则可知,密勒码的逻辑1虽然在位的中间要发生电平跳变,但是电平跳变的方向取决于前一位编码结束时的电平;逻辑0的电平跳变也与前一位编码结束时的电平有关。从编码规则可以看出,当前的编码输出是与前一个数据位的编码输出相关的,所以在设计密勒编解码器时,需要采用时序逻辑电路进行设计。

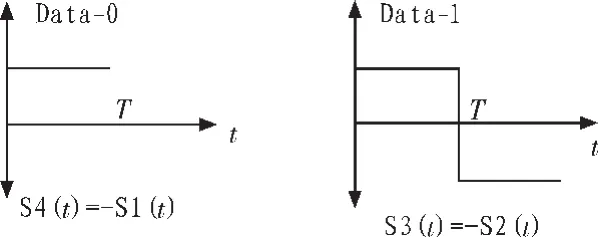

根据密勒编码规则,分别要用两个状态来表示逻辑0和逻辑1;用S1(高电平的逻辑 0)和 S4(低电平的逻辑0)来表示逻辑零,用S2(负跳变)和S3(正跳变)来表示逻辑1,所以有S1=-S4,S2=-S3;下图为密勒编码功能图:

图1 密勒编码功能图Fig.1 Miller encoding map

根据编码,绘制出如下的密勒码序列,如图2所示,从图中能够看到,密勒码中电平的转换是由前一个时刻的电平状态确定的。

图2 密勒编码波形Fig.2 Miller encoding waveform

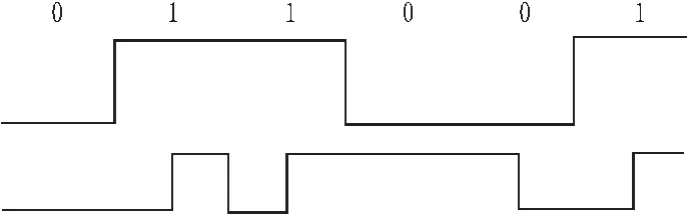

根据密勒码的特点和对各个状态的描述,密勒编码中的4个状态转换关系如下图所示。

图3 密勒编码状态转换图Fig.3 Miller encoding state transition diagram

从密勒编码状态转换图中,能够看到:状态S2在检测到数据零后能够转换到状态S4,但是状态S4无论检测到什么数据,都不能转换到状态S2,这是由于如果状态S4转换到状态S2,电平将不发生翻转,不符合密勒编码规定,故状态S4不能直接转换到状态S2;同理状态S1也不能直接转换到状态S3。

密勒调制副载波序列是用密勒编码的波形去调制副载波序列产生的,M值设定编码的速率,M=2,4,8。 从 ISO/IEC18000-6C协议给出的密勒调制副载波序列可概括出密勒调制副载波的编码规则[1]:每个比特的数据有M个副载波周期;逻辑1电平的中间发生相位的翻转;两个相邻的逻辑0电平之间发生相位的翻转;逻辑0电平期间不发生相位的翻转。

在M=2时,产生数据时钟二分频信号CLK;将密勒编码产生的密勒序列与二分频时钟同或[3,7],将产生M=2时的密勒调制副载波序列。

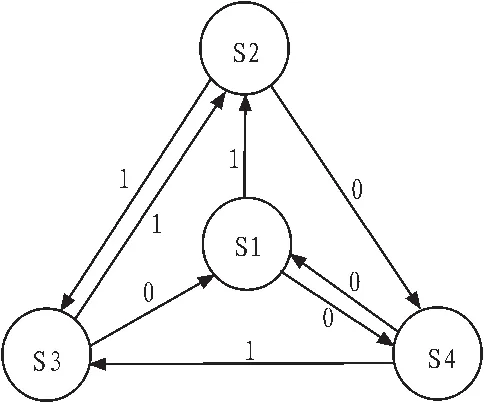

2 解码设计

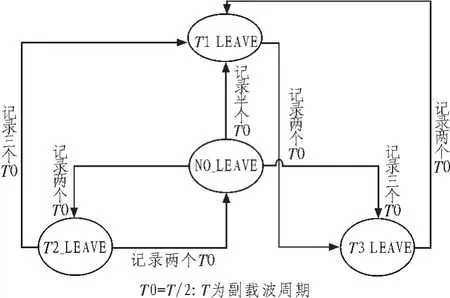

根据密勒调制副载波序列的特点,设计了一种密勒调制副载波解码器。主要的思想是利用FPGA在处理速度上的优势,记录两个数据上升沿之间经过的数据解码时钟个数,根据记录的解码时钟个数确定解码状态,然后根据当前的时钟个数以及当前的解码状态,确定当前的解码输出。为了在超高频读写器中很好地使用解码器模块,本解码器还包括了前导序列检测等功能。由于密勒调制副载波的相位变化特点,做出如下的状态分配:NO_LEAVE:解码一开始就进入此状态。在解码过程中,如果某一次计数完成刚好解码出一个数据位,也进入此状态。

T1_LEAVE:如果某一次计数刚好记录副载波半个周期的时间,则解码器进入此状态。

T2_LEAVE:如果某一次计数刚好记录副载波一个周期的时间,则解码器进入此状态。

T3_LEAVE:如果某一次计数刚好记录副载波一个半周期的时间,则解码器进入此状态。

解码器设计的状态转换图如下:

图4 解码状态装换图Fig.4 Decoding state transition diagram

为了检测前导序列,在解码模块进入解码状态后,检测到第一个“0”的时候,把接下来的解码输出与10111进行比较,如果开始的解码输出为10111,则证明后续的解码数据为标签传输给阅读器的有效数据[4]。

3 仿真结果

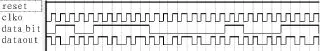

设计的密勒调制副载波序列编码器及解码器采用Verilog HDL语言实现。为了验证设计时序的正确性,采用QuartusII9.1进行设计输入、编译、综合、布局布线[5]以及时序优化等,并通过Altera公司FPGA专用下载线下载到目标板上进行测试,设计编解码模块测试结果完全达到了设计时序要求。图5为通过QuertusII9.1仿真得到的波形图。在仿真测试中,旨在验证本设计的正确性,故选择M=2。密勒调制副载波编码模块仿真结果如图5所示。

图5 编码模块仿真图Fig.5 Encoding module simulated map

在图5中reset为复位信号,当reset为高电平时,密勒调制副载波编码模块开始编码;clk0为编码时钟,是由数据时钟二分频产生的;data_bit是与数据时钟同步的待编码数据;dataout是编码输出。

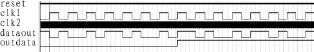

在分析了密勒调制副载波特性后,用Verilog HDL硬件描述语言根据解码状态转换图实现的解码模块仿真结果如图6所示。

在图6中,reset是复位信号,低电平解码模块复位,clk1是编码时钟,clk2是解码时钟,dataout是编码输出的密勒调制副载波序列,outdata是解码模块输出的信号,从图中也能够清晰地看到,编码模块输出是符合密勒调制副载波序列特性的。

图6 解码模块仿真图Fig.6 Decoding module simulated map

通过仿真并且下载到EP1C12Q240C8目标板上,通过示波器检测相应的输出引脚信号,与设计时序进行对比,可以发现设计完全实现了密勒调制副载波编解码功能,示波器能够检测到密勒调制副载波序列和解码输出序列,证明了设计的正确性。

4 结束语

基于ISO/IEC18000-6C协议中规定的密勒调制副载波序列,分析了密勒编码的特点,并且由密勒编码的特点设计出了密勒调制副载波编码器;在研究协议规定的密勒调制副载波序列特性后,设计出了超高频读写器中常用的密勒调制副载波解码器;并运用Verilog HDL硬件描述语言在FPGA上实现了该设计,测试结果验证了该设计的正确性。该设计具有编解码效率高、移植性好、方便模块化设计等优点。

[1]EPC global.EPC radio-frequency,identity protocols class-1 generation-2 UHF RFID protocol for communications at 860MHz~960MHz Version 1.2.0 [S].U.S.A.EPC global Inc,2008.

[2]樊昌信,张甫翊,徐炳祥,等.通信原理[M].北京:国防工业出版社,2008.

[3]邱祖江,郭亚炜,杨莲兴.一种改进miller编解码的实现方法[J].微电子学,2000,30(3):176-178.

QIU Zu-jiang,GUO Ya-wei,YANG Lian-xing.An improved implementation method of encoding and decoding miller[J].Microelectronics,2000,30(3):176-178.

[4]肖自铧,马琪,顾伟,等.一种应用于超高频射频识别的密勒编码器[J].杭州电子科技大学学报,2008 28(6):13-16.

XIAO Zi-hua,MA Qi,GU Wei,et al.A used Miller UHF RFID encoder[J].Hangzhou University of Electronic Science and Technology,2008,28(6):13-16.

[5]周润景,图雅,张丽敏.基于 QuertusII的 FPGA/CPLD数字系统实际实例[M].北京:电子工业出版社,2007.

[6]方洪灿,张福洪,陈胜康.一种改进的RFID中的密勒调制解码方法[J].电子技术应用,200935(9):71-73.

FANG Hong-can,ZHANG Fu-hong,CHEN Sheng-kang.An improved decoding method of Miller in RFID[J].E-technology applications,2009,35(9):71-73.