高速高密度PCB的SI问题

2011-07-13周胜海涂友超

周胜海,涂友超

(信阳师范学院 物理与电子工程学院,河南 信阳 464000)

数字电子产品发展快、应用广。PC机是数字电子产品的代表。PC机性能不断快速提高,要求数据传输速率不断提高,即要求总线带宽(bus bandwidth)不断增加。传统措施:一是提高总线速度,即每秒钟传输更多比特(bit);二是增加总线宽度,即更多比特并行传输。目前,计算机比特率(bit rates)已达到数十吉赫芝(GHz),大尺寸电路板上已是数十甚至数百比特并行传输。随着总线变快变宽,就出现了SI(signal integrity)问题。现代总线设计者,必须计算电压到毫伏,必须计算时序到皮秒(ps)[1]。对高速高密度PCB设计者而言,必须改变传统的逻辑信号观点,必须运用新的设计观念和设计技术,必须有效应对SI问题。在PCB级,影响SI的3个主要方面是互联阻抗不连续引起的反射、邻近互联引起的串扰和逻辑器件开关引起的SSN(simultaneous switching noise)。笔者从高速高密度PCB设计的角度,在介绍SI问题的产生的基础上,着重分析了反射、串扰和SSN的机理、特性及对SI的影响。

1 SI问题的产生

通过提高总线速度来克服总线带宽限制,有两个方面。1)总线频率提高,互联(interconnects)表现出高频效应,频率越高,高频效应越重,可能严重影响总体性能;2)总线频率提高,通常会增加功耗,对电池供电的便携式设计是个大问题。通过增加总线宽度来克服总线带宽限制,也有两个方面。1)引脚数太多,相距太近,相互干扰,难以保证 “干净数据”(clean data);2)据摩尔定律(Moore’s law),增加总线宽度只是短期的权宜之计。所以,比较而言,提高总线速度是必然的。

总线速度越高,要求时序不确定度(timing uncertainity)越小。目前,数字系统的边缘速率(edge rates)已达35 ps[1]。根据Fourier分析,边缘速率越高,频谱中的高频越丰富。所以,在高速数字系统中,每段导线都不再是传统意义上的导线,而是有与频率有关的寄生电感、电容和电阻的寄生元件。寄生元件有时延和瞬时阻抗,会引起信号失真。每段导线与周围环境,包括电源结构、地结构、散热器、其他导线,甚至无线网络,都有耦合。信号不是限于导体中,而是在导体附近的电磁场中[2]。互联中的信号相互影响。

所以,在高速数字系统中,就出现了SI问题。术语SI目前尚无统一定义,一般认为SI是指保证数字脉冲在一对连接盘(a pair of lands)之间传输时,能够以要求的电平和波形到达接收端[3]。在PCB级,影响SI的3个主要方面是互联阻抗不连续引起的反射、邻近互联引起的串扰和逻辑器件开关引起的SSN。

2 反 射

实际数字信号近似为梯形波。数字信号的带宽BW由信号的上升时间 tr决定[4],即

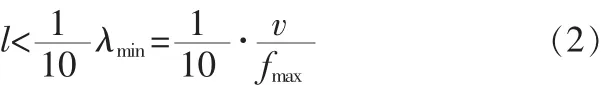

在高速数字设计中,通常使用一个准则,当互联的长度l小于所传输信号最高频率成分(fmax)波长(λmin)的 1/10时,认为互联是电小尺寸 (electrically small),互联不会引起SI问题。即

v是信号在互联中的传播速度。将fmax=1/tr代入式(2),整理得

td是互联的时延(time delay)。对PCB上的互联,作为实用的经验规则,通常取

语法化——一个新兴的语法手段产生过程。一个词语一旦语法化,就会失去独立运用的能力,而成为一种附着成份。一个实词语法化过程往往涉及到两个成分的重新分析,会改变原来的词汇边界。一个词语的语法化过程往往涉及到两个成分的重新分析,而两个成分的重新分析必须在紧邻的句法环境中进行。一个词语的语法化常常会促使其原来意义的抽象化,退化掉一些原来的词汇意等。③

式中:l的单位为 in(1in=2.54 cm),tr的单位为 ns。

在大多数高速数字系统中,tr大约是时钟周期的1/10。对现代和未来的数字产品而言,时钟频率越来越高,tr越来越短,是必然趋势。值得注意的是,即使时钟频率很低(如低于50 MHz),由于高速数字器件的广泛应用,同样会出现很短的tr[5]。在现代高速数字产品中,tr已短至 0.1 ns,据式(4),不引起SI问题的l<0.1 in。实际上,所有的互联长度都超过这一限度。

所以,在现代和未来高速数字产品中,典型的互联,如PCB 上的微带线(microstrip)或带状线(stripline)、同轴电缆、扁平电缆、绞线对电缆等,都必须按传输线(transmission lines)来处理[6]。 传输线任一端的阻抗不匹配(mismatching)或沿传输线的不连续(discontinuities)都引起信号反射,进而引起 SI问题[7]。

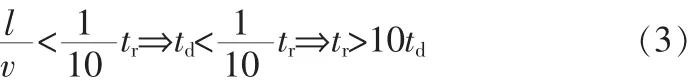

作为一个典型实例,考虑微带线连接的两个CMOS门。典型的 CMOS门,输出电阻(非线性)为 10~30 Ω,输入是典型的容性,电容为5~15 pF。设微带线长为20 cm,线宽为100 mil(1 mil=0.025 4 mm),FR-4 基板(εr=4.7),基板厚为 62 mil。据有关公式计算可知,微带线的特性阻抗为53.4 Ω,时延为1.25 ns。 设驱动门输出为 2.5 V、25 MHz、tr=tf=2 ns、 占空比50%的连续梯形脉冲。驱动门等效为内阻25 Ω的戴维宁等效电路,负载门等效为5 pF的电容。PSPICE仿真得到传输线输出电压(负载门输入电压)波形如图1所示。可见,由于传输线两端阻抗不匹配而引起信号反射,形成振铃(ringing)现象,引起SI问题。可能导致电平进入逻辑0和逻辑1之间的“灰色区域”,引起逻辑错误。测试结果与仿真结果吻合[3]。

图1 反射引起的振铃Fig.1 Ringing caused by reflection

沿传输线还会存在很多引起不连续的因素,如转弯、过孔、线头、分支、封装引线、交叉、测试盘等。这些不连续,对沿传输线传播的信号而言,“看到”的是阻抗发生了变化,即阻抗不连续。阻抗不连续即引起信号反射,进而引起SI问题。

3 串 扰

在高速数字系统中,每一条互联线及其信号返回通路都构成环路,互联中的信号是以电磁场的形式传播的。对邻近的两个(或多个)环路而言,一条互联线中信号的电磁场,有一部分进入相邻环路,即相邻互联线之间存在互容(mutual capacitance)和互感(mutual inductance)。 据电磁理论,一条互联线上电流变化 △I/△t(电压变化 △V/△t)通过互感 LM(互容CM)在邻近互联线上感应产生的噪声电压△VL(噪声电流△IC)分别为

可见,在数字系统中,当一条互联线上传输信号时,会在临近互联线上感应产生噪声,即串扰噪声(crosstalk noise)。

信号返回通路是大的均匀的导体平面时,如高速PCB上大多数耦合传输线,感性耦合电流与容性耦合电流为同一量级。信号返回通路是IC封装中的单根导线或连接器中的引脚时,感性耦合电流比容性耦合电流大得多,后者可略。

比较而言,带状线和嵌入式微带线(embedded microstrip)的串扰都较微带线的串扰小。所以,研究PCB互联线串扰时,通常以微带线为具体对象。典型代表是FR-4基材PCB上的微带线,特性阻抗50 Ω,线宽和线间距均为5 mil。5 mil是目前PCB工艺水平达到的最小值。

多平行微带线间的串扰与其电容矩阵(capacitance matrix)和电感矩阵(inductance matrix)[8]密切相关。 矩阵取决于多平行微带线的几何结构。矩阵的各元素值可由专业软件(如Ansoft SI2D Field Solver)快速精确算出。对均匀传输线,元素值通常取单位长度值。电容矩阵和电感矩阵是仿真和预测串扰的基础。

高速高密度PCB上的多数传输线信号返回通路都是大的连续的导体平面,串扰主要来自紧邻的传输线,来自其他邻近传输线的串扰可略。

对串扰的关注重点是近端串扰(near-end crosstalk)噪声电压和远端串扰(far-end crosstalk)噪声电压。通常用串扰系数(串扰噪声电压幅值与信号电压幅值之比)来评价串扰程度。在tr/2时间内,信号在互联线上传播的距离,称为饱和长度(saturation length)。对FR-4基材PCB上的传输线,信号的传播速度约为6 in/ns。所以,对数据率大于数Gbit/s的高速数字系统,互联线的耦合长度都大于饱和长度。

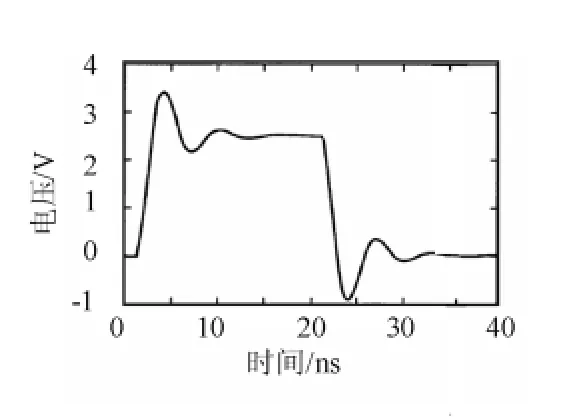

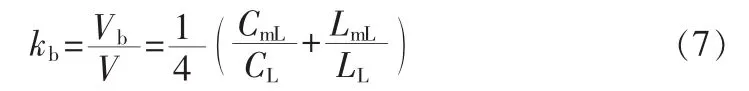

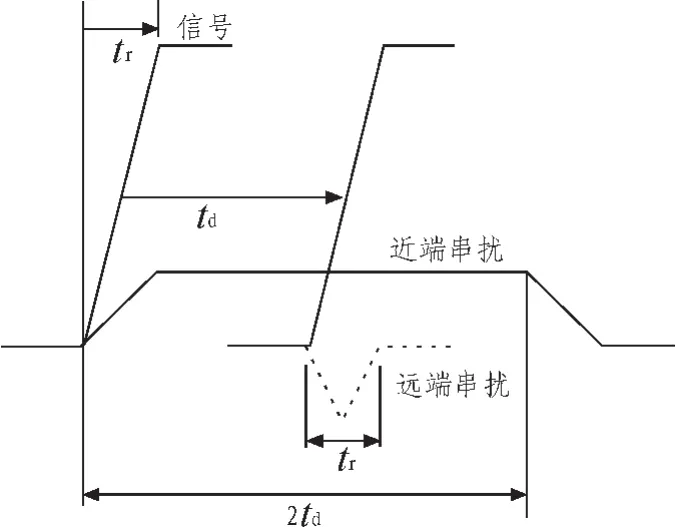

对两条端接平行微带线,当耦合长度大于饱和长度时,近端串扰噪声电压波形如图2所示[1],近端串扰系数kb为[5]

式中:Vb是近端串扰噪声电压,V是信号电压,CmL是单位长度的互容,CL是信号线单位长度的电容,LmL是单位长度的互感,LL是信号线单位长度的电感。

图2 近端串扰和远端串扰噪声脉冲Fig.2 Near and far-end crosstalk noise pulses

可见,近端串扰只取决于耦合强弱,而与耦合长度和信号上升时间(tr)均无关。

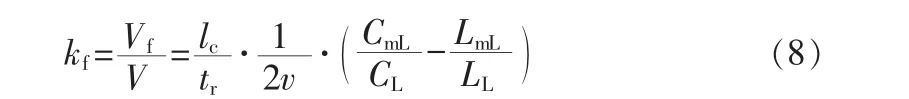

两条端接平行微带线的远端串扰噪声电压波形如图2所示,远端串扰系数kf为[5]

式中:Vf是远端串扰噪声电压,lc是耦合长度,tr是信号上升时间,v是信号传播速度。

可见,远端串扰不仅取决于耦合强弱,还取决于耦合长度和信号上升时间(tr),耦合长度越长和信号上升时间越短,串扰都越严重。

若互联线的两边都有平行的互联线(如总线),则串扰为式(7)、(8)结果的 2 倍。

不同系列数字IC的噪声容限不完全相同,典型的是噪声容限约为信号电压摆幅的15%。通常将这15%的1/3(即5%)分配给串扰。如信号摆幅为3.3 V,最大允许串扰噪声约为160 mV。这似乎对最大允许串扰噪声的限制并不严格。然而,PCB上典型互联线最大串扰噪声可能超过5%。仿真结果表明,FR-4基材PCB上的微带线,两边都有3.3 V的信号传输时,引起的串扰噪声大于300 mV[5]。

大多数数字系统使用信号传输接口(signaling interfaces),信号传输接口中有大量的互联线通过IC封装、连接器(connectors)及PCB平行分布,串扰可能成为决定数字系统性能的因素之一。数字系统速度更快、尺寸更小的发展趋势,将进一步加剧串扰的严重性。串扰引起的问题主要有两方面:其一,串扰改变互联线的传播特性(特性阻抗和传播速度),进而影响SI和时序;其二,串扰在互联线上产生噪声,进而损害 SI和降低噪声容限(noise margins)[1]。

4 SSN

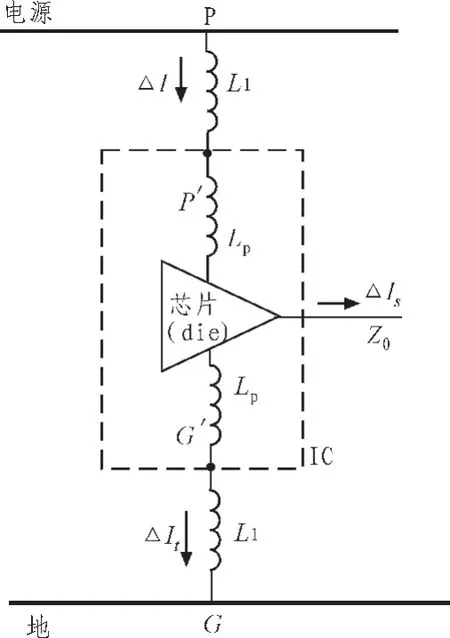

在数字系统PCB上,通常用一对电源总线或一对完整导体平面 (铜箔层)给IC供电。IC与PDN (power distribution networks)连接的简化等效电路如图3所示。PDN的特性阻抗为 ZPDN。 IC 电源引脚(P′)和地引脚(G′)与 PDN 的连线有引线电感L1,IC内芯片(die)与引脚之间有封装电感Lp。IC的输出通过特性阻抗为Z0的互联线到接收器(receiver)。输出逻辑0→1转换或逻辑1→0转换时,输出电平变化为△V,转换时间为△t。输出转换时,输出级的两个管子(totem-pole结构)会瞬间同时导通,使PDN的电源与地之间瞬间出现低阻通路,形成瞬变电流△It。同时,输出逻辑0→1转换时,形成另一瞬变电流△Is为

图3 IC与PDN连接Fig.3 Connection of an IC to a PDN

△Is也必须由PDN提供。所以,PDN必须提供的总瞬变电流△I为

△I在P、G两点间引起的瞬变电压△VPG为

△VPG是一种冲激骚扰,通过PDN加到IC的电源上,引起SI问题。IC内多个门同步开关时,这种噪声会叠加而变强,这就是SSN。SSN可达到引起系统故障的程度[9]。

据式(11),设计PCB时,减小SSN的有效方法是尽量减小ZPDN。随着大规模IC的电源电压越来越低和功耗越来越大,要求ZPDN必须低,有的要求达到甚至低于1 mΩ[10]。

IC电源通路还有一部分瞬变电压△V1是由引线电感L1引起的,

随着数字系统的速度越来越高,tr越小,△V1越大。减小△V1的有效方法是尽量减小L1。

封装电感Lp也会在IC电源通路引起瞬变电压,高性能IC设计与制造时必须采取应对措施[11-12]。

5 结束语

高速高密度PCB的SI对产品性能有决定性影响。在PCB设计中,必须进行SI仿真和预测。在PCB级,影响SI的3个主要问题是反射、串扰和SSN。全面、准确地认识这3个问题的机理、特性及对SI的影响,是有效应对SI问题的基础。

本文的讨论与结论对高速高密度PCB设计实践具有参考作用。

[1]Hall S H,Heck H L.Advanced signal integrity for highspeed digital design[M].Hoboken (NJ, USA):John Wiley&Sons, 2009:1-8, 170, 145-146.

[2]Lehner G.Electromagnetic field theory for engineers and physicists[M].Berlin:Springer, 2010:343-505.

[3]Paul C C.Introduction to electromagnetic compatibility[M].2nd ed.Hoboken (NJ, USA):John Wiley&Sons, 2006:225-259.

[4]Ott H W.Electromagnetic compatibility engineering[M].Hoboken (NJ, USA):John Wiley&Sons, 2009:380.

[5]Bogatin E.Signal and power integrity—simplified[M].2nd ed.Upper Saddle River (NJ, USA):Pearson Education,2010(19): 405-474.

[6]Caniggia S,Maradei F.Signal integrity and radiated emission of high-speed digital systems[M].Hoboken (NJ,USA):John Wiley&Sons, 2008:91-92.

[7]Peterson A F,Durgin G D.Transient signals on transmission lines[M].San Rafael (CA, USA):Morgan&Claypool Publishers, 2009:1-8.

[8]Paul C R.Analysis of multiconductor transmission lines[M].2nd ed.Hoboken (NJ, USA):John Wiley&Sons, 2008:160-239.

[9]周胜海,李长庚.高速高密度PCB上的SSN问题[J].电子质量,2011(6):4-6.ZHOU Sheng-hai,LI Chang-geng.SSN problems in highspeed and high-density PCBs[J].Electronics Quality,2011(6):4-6.

[10]Novak I,Miller J R.Frequency-domain characterization of power distribution networks[M].Norwood (MA, USA):Artech House Inc., 2007:123.

[11]Kaeslin H.Digital integrated circuit design[M].New York:Cambridge University Press, 2008:495-522.

[12]Jakushokas R,Popovich M,Mezhiba A V,et al.Power distribution networks with on-chip decoupling capacitors[M].2nd ed.Berlin:Springer, 2011:27-69, 285-301.