在机车横向振动信号模数转化中的应用

2011-07-13齐文达

齐文达

(广西军区75475部队 广西 防城港 538037)

列车在运行过程中横向存在着多种运动形式的组合,在曲线上既有所要滤除的横向离心加速度信号,又有需要的列车本身的横向振动信号。为了消除各种随机振动对控制上所需的横向加速度信号的影响,必须对加速度传感器测出的信号进行滤波处理,由于加速度传感器测得的是模拟信号,在对信号进行数字滤波前,必须进行模数转换。DSP具有强大的运算能力,TMS320LF2407 DSP模数转换模块带内置采样/保持(S/H)的10位模数转换模块ADC,多达16个的模拟输入通道,具有自动排序的能力,转换的通道都可通过编程来选择,可单独访问的16个结果寄存器(RESULT0—RESULT15)用来存储转换结果,多个触发源可以启动AD转换。共有单排序和双排序两种工作模式,每一种模式有连续的自动排序模式和启动/停止模式,本论文选用的TMS320LF2407 DSP集成的ADC。

1 机车横向振动信号采集与采样频率的确定[1-3]

机车每个转向架配置2套减震系统,2个加速度传感器,每个传感器测得2路振动信号,在通过A/D转化、数字滤波、每个传感器获得的两路信号分别矢量相加后获得横向振动控制信号,分别为两个减振系统提供控制信号。车体横向振动的频率范围为1~4 Hz,频带较窄,这个频率带是影响人体感受舒适度的频带。列车过曲线时的离心加速度信号范围的频率仅为0.078 Hz,随着列车运行速度的提高,其频率将增大,但不会超过0.5 Hz,根据国内外的相关资料,截止频率应在0.5~1 Hz之间。据 《中华人民共和国铁道行业标准》TB/T 2360-93铁道机车动力学性能实验鉴定方法及评定标准,测量的加速度信号通过截止频率为40 Hz的低通滤波器,满足采样定理:ωs≥2ωmax,采样频率可以取 100 Hz。

2 TMS320LF2407 ADC模块在A/D转化中的应用

从控制原理上可以看出,需要对4路信号同时采样(一个传感器采集两路信号),进行信号数字信号处理后,再输出控制信号。但是TMS32DLF2407的模数转换模块(ADC)是顺序采样,并不是并行采样[4]。那就要具体判断,顺序采样能否限制在误差范围内,如果达不到要求,就要进行并行A/D转换芯片的扩展。仔细考虑,合理安排4路采样的顺序,只要尽可能对一个传感器输出的两路信号采样间隔在允许的范围内就可以。

2.1 A/D转换的设计

10 位的A/D转换器最小转换时间为500 ns,所以相邻两路转换时间上也就是相差A/D这个时间。1,2,3,4路信号可以合理安排,因为每个转向架上有一个加速度传感器,每个加速度传感器输出的一对信号在A/D转换后进入控制器内进行滤波,积分,矢量相加等信号处理,最终经D/A转化后作为控制信号输出。所以安排第一个传感器占用第一和第二A/D转换通道,第二个传感器占用第三和第四通道。

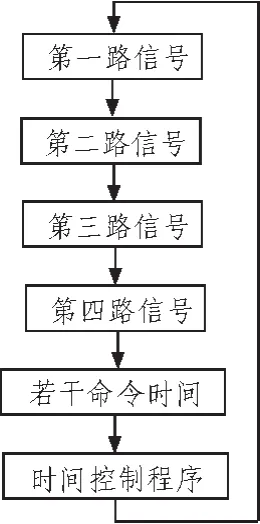

完全可以结合采样频率(本系统设定为100 Hz)人为控制连续4路的A/D转换情况,使每两路信号的采样限制在最小时间范围内,再用时间控制程序安排在4路采样结束和重新开始之间,这样以满足每路采样频率达到100 Hz,有如图1所示的示意图。

图1 A/D转换示意图Fig.1 A/D converter schematic

若干命令时间是指每进行完一次周期采样后读取结果寄存器(RESULTn)的几个结果的命令和初始化相关A/D转换寄存器命令所需的时间。加大时间控制程序运行时间可以使同一传感器两路检测信号之间转换的时间差达到最小,即为了减少不同步转换造成的误差达到最小,使其满足系统采样频率的要求。

2.2 ADC模块的寄存器

ADC模块的寄存器[5]包括ADC控制寄存器ADCTRL1/2、最大转换通道数寄存器MAXCONV、通道选择排序控制寄存器CHSELSEQ1/2/3/4、转换结果缓冲寄存器RESULT0-15。

1)ADC控制寄存器ADCTRLn的设置。

①它的8-11位ACQPS3-ACQPS0是采样时间选择位,这几位决定了ADC时钟的预定标系数。为了减小采样通道之间的时间,把ACQPS3-ACQPS0均设置成0,这样采样时间为 2×(本控制器采用的 CPU为30 MHz)。

②7位CPS是转换时钟预定标位。在此设置该位为0,转换时钟FCLK=CLK/1,CLK为CPU的时钟频率。

③6位CONT RUN是连续转换位,这一位决定排序器工作在连续转换模式或者启动/停止模式。在启动/停止模式下,排序器必须复位使排序器指针指到CONV00,针对采样频率的确定,采用启动/停止模式,该位设置为0。

④位SEQ ACSC是级连排序器工作方式位。由于本程序设计采样4路信号,可以用双排序工作模式。该位设置为0。

总之,其他位设置为默认方式,这时*ADCTRL1=0x0050。软件启动SEQ1,所以*ADCTRL2=0x2000。

2)最大转换通道数寄存器MAXCONV寄存器设置,0-6位决定了一次自动转换最多转换的通道个数。由于对SEQ1进行操作,所以应该对MAX CONV0-2位赋值,由于是4路信号,所以*MAX CONV=0x04。

3)转换结果缓冲寄存器RESULT0-3。是缓存转换结果的,不需要设置。

4)*CHSELSEQ1=0x3210。

2.3 采样与误差分析

分析如下[6]:

1)每一路采样周期=4×ADC转换周期+若干命令时间+时间控制程序时间。从这一公式可以看出每一路采样频率是一定的,均可设置到固定的100 Hz。在这个公式中可以看出,能改变的只是ADC转换周期和时间控制程序时间,而ADC转换时间和时间控制程序时间是此消彼长的关系。但是要想减少由于不并行处理带来的误差就要减少ADC转换周期,这样ADC转换周期减少,等待循环时间就必须增加了。

2)由于系统需要的采样频率是100 Hz,也就是说采样周期为10 ms,而每相邻两路转换时间间隔最少仅为500 ns,所以这个时间和10 ms相比是微不足道的。再者,由于有用信号是1~4 Hz的低频信号,采样到的信号还要经过滤波,本系统是连续采样不连续输出,对积分结果平均再输出误差不显著。所以,本系统完全可以用TMS320LF2407 DSP集成的A/D转换芯片。

3 结 论

通过对DSP ADC模块进行软件编程,实现不同的采样频率,使A/D转换能够完全满足控制系统的要求,给系统硬件设计带来了很大的便利性,具有其他控制器不可比拟的优势。

[1]丁问司.机车横向半主动控制液压减振器研究[D].北京:清华大学,2003.

[2]余泊.DSP在振动信号采集与分析中的应用[J].测控技术,1998(5):7-9.

YU Bo.DSP signal acquisition and analysis of vibration in the application[J].Control Technology ,1998(5):7-9.

[3]蒋红梅.计算机控制系统中采样周期的确定[J].工业控制计算机,2005(18):5-8.

JIANG Hong-mei.The computer control system to determine the sampling period [J].Industrial Control Computer,2005(18):5-8.

[4]刘和平.TMS320LF240X DSP C语言开发应用[M].北京:北京航空航天大学出版社,2003.

[5]黄英哲.TMS320C2407原理与C语言控制应用实习 [M].武汉:中国水利水电出版社,2003.

[6]苏涛.实时信号处理系统设计[M].西安:西安电子科技大学出版社,2006.