基于74LS162数字钟设计及时间校准研究

2011-07-13黄红飞陈亦兵

黄红飞,陈亦兵

(广东茂名广播电视大学 广东 茂名 525000)

数字钟是一种用数字电路技术实现时、分、秒计时的装置,与机械式时钟相比具有更高的准确性和直观性,且无机械装置,具有更长的使用寿命,因此得到了广泛的使用[1]。数字钟的设计方法有许多。其电路一般设有校时功能,当计时出现误差时,电路可以进行校时、校分和校秒[2]。通常,用中小规模集成电路组成电子钟的校时电路,其校正时间的方法是:首先截断正常的计数通路,然后再进行人工触发计数或将频率较高的方波信号加到需要校正的计数单元的输入端,校正好后,再转入正常计时状态[2]。笔者以中规模数字集成芯片74LS162设计数字钟为例,介绍一种简单、易操作的校时电路,而且数字钟时间校准的操作不需加入专门的校时脉冲信号。

1 数字钟电路框图

通常的数字钟都是由产生频率为1 Hz时钟信号电路、60进制和24进制计数器、译码驱动及显示和校时电路等几个单元电路构成[2]。频率为1 Hz方波信号电路已有比较成熟的技术,用晶体振荡器或者555多谐振荡电路均可容易获得[3]。而数字钟的译码驱动及显示单元电路的设计更是简单。因此,本文只介绍数字钟计数单元的设计和时钟的校时功能。

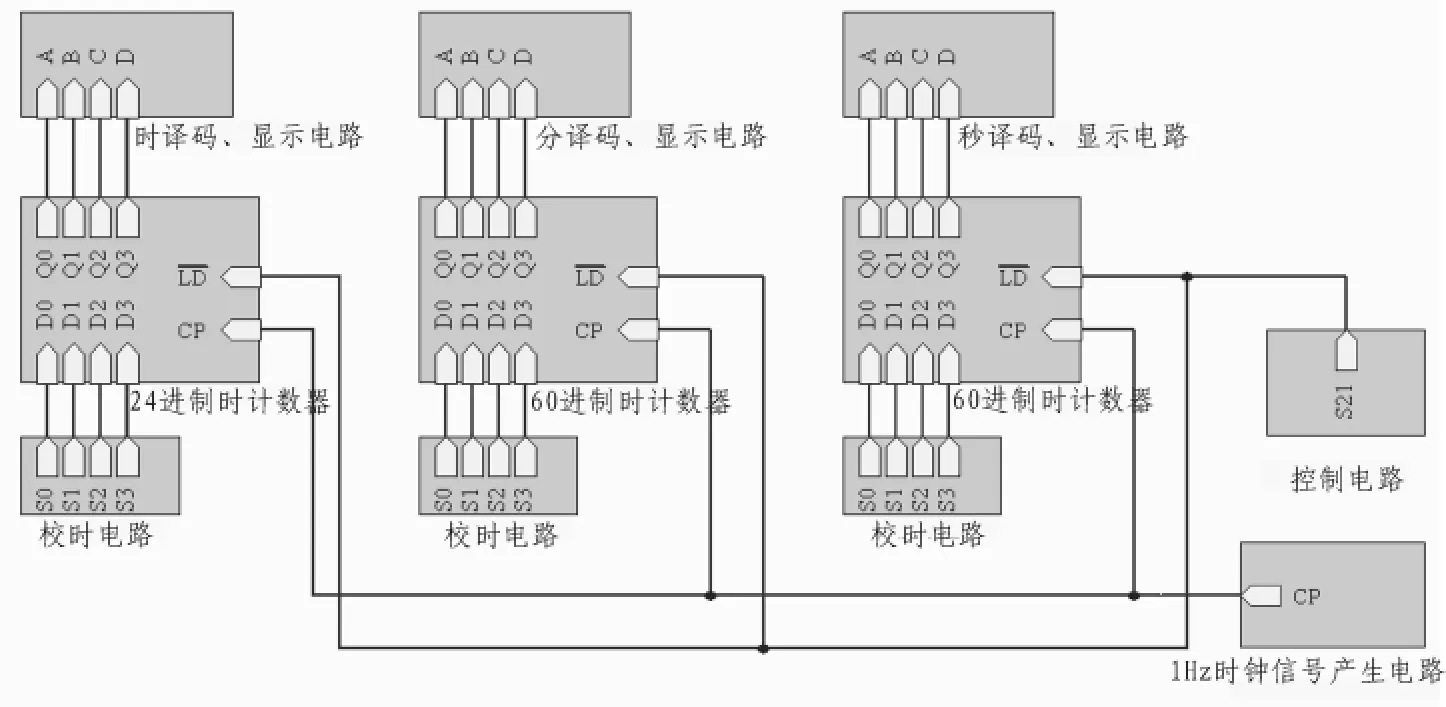

下面用数字钟的层次原理图[4]表达本电路的设计框图,由图1可见,电路设计有两个60进制和一个24进制计数器;每块计数器芯片的时钟输入端CP端均接同一个CP信号,CP信号频率为1 Hz;控制电路其实是一个开关,通过开关的接通与断开输出高、低电平信号送至所有计数器的置数端,同时控制计数器置数或加法计数;校时电路由多个开关组成,通过开关动作将相应的数字信号送至计数器的4个并行数据端 D3、D2、D1、D0,予以调整时间值。

2 “60进1”和“23翻0”的计时原理

中规模集成芯片74LS162是本文设计数字钟电路的主要芯片,它是同步十进制计数器,其功能表如表1所示。

由表1可知,74LS162主要有3种工作模式:同步清零、同步并行预置数和计数模式。3种工作模式都要求与CP上升沿同步操作。用其同步清零和同步置数的功能,可以设置任意进制的计数器。本文用同步清零实现时、分、秒电路;其同步置数则实现校时功能。

2.1 60进制分钟和秒钟计时电路

图1 数字钟框图Fig.1 Block diagram of digital clock

表1 74LS162的功能表Tab.1 74LS162 menu

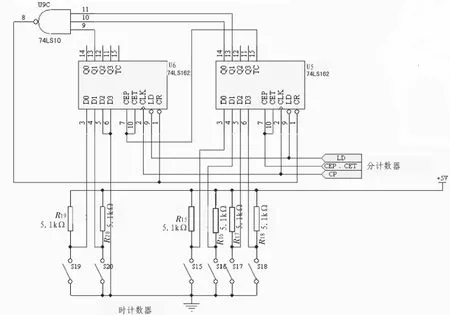

图2 60进制分钟和秒钟计时电路图Fig.2 60 decimal minutes and seconds timer circuit

通常,数字钟的分钟和秒钟计时电路要设计为60进制计数器[1]。如图2所示,是分钟和秒钟计时电路,分别用两个74LS162芯片构成60进制计数器。它们的个位芯片接成十进制形式,个位在1 Hz CP信号上升沿作用下按照8421BCD码进行加法计数[1],将此块芯片的进位输出端“TC”联接到十位芯片的使能端“CEP”和“CET”,此联接实现“逢十进一”的功能。十位芯片的设置非常重要,它要求有“60进1”的功能。由于74LS162有同步清零功能,十位芯片按(N-1)值反馈清零法[1]设为六进制(即N=6)形式。所谓(N-1)值反馈清零法是利用清零端“”和与非门,将(N-1)对应的输出二进制代码中等于“1”输出端,通过与非门反馈到清零端“CR”,使电路输出回零。因为N=6,其 (N-1)所对应的输出二进制代码为0101,所以电路将输出端Q2和Q0接至与非门进行反馈。但是,这样设置电路在运行到“50”时,电路便回零了。因此用74LS162同步清零设计分钟和秒钟时,再将个位芯片的进位输出端“TC”也通过三输入与非门74LS10进行反馈便能实现“59 翻 0”[1]的功能了。

在本电路的设计中有一条非常重要的连线,就是与非门74LS10输出的信号除用作自身输出回零外,此信号再经一级与非门取反后,连至下一级计数器单元电路的使能端“CEP”和“CET”。此设计的结果是分、秒计数器运行至“59”时,通过与非门反馈回零的低电平信号“0”,再经过一非门变为高电平“1”。 根据数字钟“60 进 1”[1]运行规律:秒计数器“59 翻 0”的同时,分计数器要按十进制加法计数“加一”;分计数器“59翻0”的同时,时计数器也按十进制加法计数“加一”。因此,本电路将此高电平送至下一级使能端,控制下一级计数器单元电路进入加法计数状态,从而实现数字钟“60进1”。其设计不同凡响!

2.2 24进制时钟计时电路

相对于分和秒计数器,时计数器电路的设计较为简单。由于74LS162是同步清零,时计数器的设计也采用(N-1)反馈清零法。如图3所示,两片74LS162连接成24进制计数器,其个位接成四进制(N=4)计数器形式,十位接成三进制(N=3)计数器形式即可。两片计数器输出(N-1)的状态对应的二进制代码中等于“1”的输出端经与非门反馈后同时送到两芯片的清零端“”,使电路以“23翻0”计时规律运行。分计数器回零信号经非门取反后送至时计数器个位芯片(图3右面片)使能端“CEP”和“CET”。这是时钟计时电路与分钟计时电路之间的必要联接,使得分计数器回零的同时,时计数器按十进制加法计数“加一”。

3 校时功能

本电路设计的校时操作非常简单、方便,只要动作开关便可进入校时状态。开关设在图2中右下角。

校时具体操作如下:

1)外接开关S21。由图2可见,通过动作开关S21输入信号控制所有计数器芯片的置数端。当开关S21闭合,置数端通过开关接地,所有计数器置数端获得低电平“0”信号,当CP上升沿到来时,计数器允许并行预置数D3D2D1D0;当开关S21断开,置数端与地开路,置数端获得高电平“1”信号,则计数器进行十进制加法计数。

2)4 个并行输入数据端D3D2D1D0分别外接开关,如图2和图3所示。本电路中预置的数据D3D2D1D0就是需设定的时间值。由于二进制与十进制之间可以相互转换,设开关断开,输入数据为高电平“1”;当开关闭合,输入数据为低电平“0”。所以,校正时间值时需将标准北京时间值转换成相应的8421BCD码,8421BCD码的4位二进制数则由其对应开关动作输入即可。电路共设有20个开关分别调整时、分、秒的时间值。每个开关动作一次确定了时间值。实际上,数字钟电路中分和秒计数器十位芯片的最高位端D3不需外接开关;时计数器十位芯片的二个高位端D3D2也不需要。从而简化电路结构并减少了元件。

可见,本数字钟的时间值均可简单通过开关动作设定。当时钟计时出现误差时,接通开关S21,各计数器允许“并行预置数”。由于所有计数器芯片的计数时钟输入端CP端均接有同一个CP信号,用此CP信号上升沿触发“并行预置数”。电路CP端的设置方法实现了时、分、秒校时的操作是任意的和互不干扰的。校时的操作无需截断正常的计数通路和加入校时脉冲信号,而且与4个数据端D3D2D1D0相连的开关最多动作一次就确定了要调整的时间值。当时、分、秒的时间值分别设定后,便断开开关,置数端恢复高电平“1”,计数器进行十进制加法计数,时钟继续正常运行。本电路的设计能对秒的时间值进行调整,因此电路精确度高。

图3 24进制时钟计时电路图Fig.3 24 decimal clock timing circuit

4 结 论

基于中小规模集成电路而设计的数字钟,其基本元件是计数器。计数器的功能非常多,如何掌握并灵活应用其基本理论呢。本文从设计的电路简单可行、容易操作、理论联系实际入手,灵活应用集成电路74LS162的同步清零和同步置数功能。电路的设计体现了数字集成电路的应用性、实践性,并强化了实际应用能力的培养。

[1]沈小丰.电子线路实验——数字电路实验[M].北京:清华大学出版社,2007.

[2]胡锦.数字电路与逻辑设计[M].北京:高等教育出版社,2002.

[3]孙建平.数字电子技术 [M].2版.西安:西安电子科技大学出版社,2005.

[4]赵伟军.Protel 99 SE教程[M].北京:人民邮电出版社,2007.

[5]徐莹隽.数字逻辑电路设计实践[M].北京:高等教育出版社,2008.

[6]王毓银.数字电路逻辑设计—脉冲与数字电路 [M].3版.北京:高等教育出版社,1999.

[7]张虹.数字电路与数字逻辑[M].北京:北京航空航天大学出版社,2007.

[8]刘常澍.数字逻辑电路[M].北京:高等教育出版社,2008.