S3C2440A芯片及应用

2011-06-09张豪杨春燕汪筱阳

张豪,杨春燕,汪筱阳

(空军工程大学 电讯工程学院,陕西 西安 710077)

S3C2440A是三星公司生产的一种16/32位RISC结构微处理器芯片[1],其带有先进的ARM920T内核,0.13 μm的CMOS标准宏单元和存储器单元,总线采用最新的Advanced Micro controller Bus Architecture(AMBA)架构。 ARM920T 内核采用MMU,AMBA,BUS和Harvard的高速缓存结构,具有独立的8字长16 kB指令缓存器和16 kB数据缓存器。

S3C2440A可提供一套通用的外设接口,无需在额外扩展外围器件,其功耗低,简单,方便,且全静态设计,特别适合于对成本和功率要求比较高的应用中。

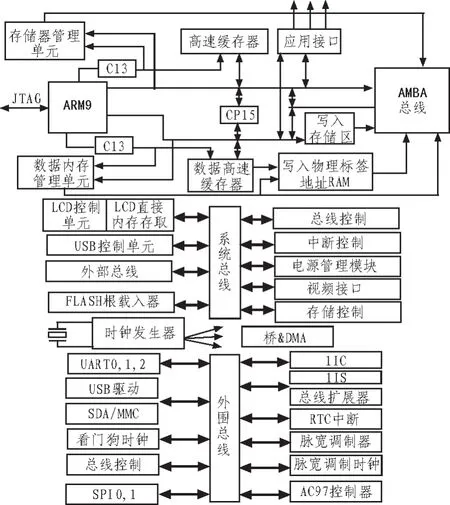

1 芯片内部结构以及功能

S3C2440A的内部结构如图1所示。

S3C2440A它主要有以下部分组成:

1.2 V内核,1.8 V/2.5 V/3.3 V存储器,3.3 V扩展 I/O,16 kB 指令 cache(I—chche)/16 kB 数据 cache(D—chche)

1)外部存储控制器(SDRAM控制盒片选逻辑)

2)集成LCD专用DMA的LCD控制器(支持最大4 k色STN256KTFT)

3)4路拥有外部请求引脚的DMA控制器

4)3路 URAT

5)2路 SPI

6)IIC总线接口(多主支持)

7)IIS音频编码接口

图1 内部结构Fig.1 Internal structure

8)AC97编解码器接口

9)1.0版SD主接口,兼容2.11版MMC接口

10)2路USB主机控制/1路USB期间控制(ver1.1)

11)4路PWM定时器/1路内部定时器/看门狗定时器

12)8路10位ADC和触摸屏接口

13)具有日历功能的RTC

14)摄像头接口

15)130个通用I/O,24个外部中断源

16)电源控制:正常,慢速,空闲,睡眠模式

带PLL片上时钟发生器

S3C2440A的内部核心器件是存储器控制器,Nand Flash控制器,Nand Flash控制器,时钟及电源管理模块,DMA,PWM及定时器,UART,ADC和触摸屏接口,看门狗定时器等,下面对它的各个模块功能进行介绍[2-5]。

1.1 存储器控制器

S3C2400A的存储器控制器提供访问外部存储器所需的存储器控制信号,它的存储器控制器具以下特点:

1)大小端(通过软件控制);

2)地址空间:每个bank有128 M的字节(总共1 G字节/8 个 banks);

3)可编程的访问位宽:bank0(16/32 位),其他 bank(8/16/32位);

4)共8个存储器banks,其中6个是ROM,SRAM等类型存储器bank。2个是可以作为ROM,SRAM,SDRAM等存储器bank;

5)7个固定的存储器bank起始地址。最后一个bank的起始地址可调整,最后两个bank大小可编程,所有存储器bank的访问周期可编程;

6)总线访问周期可通过插入外部wait来延长;7)支持SDRAM的自刷新和掉电模式。

1.2 Nand Flash控制器

S3C2400A是在Nand Flash上执行启动代码,在SDRAM上执行主程序。S3C2400A的驱动代码可以在外部的Nand Flash存储器上执行。为了支持Nand Flash的 boot loader,S3C2400A配备了一个内部的SRAM缓冲器名为steppingstone。启动时,Nand Flash上的前4 k byte字节将被装载到steppingstone上,steppingstone上的启动代码将会被执行。

1.3 时钟及电源管理模块

时钟电源管理模块包含了3个部分:Clock控制,USB控制,POWER控制。时钟逻辑单元能够产生S3C2400A需要的时钟信号,包括CPU使用的主频FCLK,AHB设备总线使用的HCLK,以及ABC总线设备使用的PCLK对于电源控制逻辑单元,S3C2400A有许多钟电源管理方案来针对所给的任务保持最优的电源消耗。S3C2400A的电源管理模块通过软件控制系统时钟来降低各个模块的电源消耗。

1.4 DMA(直接内存存取)

S3C2400A支持位于系统总线和外设总线之间的4个通道的控制器。每个DMA控制器通道无限制的执行系统总线上的设备或外设总线上的设备之间数据搬移。DMA的主要特点就是其其传输数据不需要CPU的干涉,DMA操作可由软件或来自内设或外部请求管脚来初始化。

1.5 PWM及定时器

S3C2440A有 5个 16位的定时器,定时器 0、1、2、3有脉冲调制功能(PWM),定时器4有一个没有输出引脚的内部定时器,定时器0有一个用于大电流设备的死区生成器。定时器的输出波形可以进行可编程任务控制。

1.6 UART

S3C2400A通用异步接收器和发送器(UART)提供了3个独立的异步串行I/O端口,每个端口都可以在中断模式或DMA模式下操作。UART使用系统时钟可以支持最高115.2 Kbps的波特率。如果一个外部设备提供UEXTCLK给UART。UART还可以在更高的速度下工作。每个UART通道对于接收器和发送器包括了2个64位的FIFO。

1.7 中断控制器

S3C2440A中的中断控制器可以从60个中断源接收中断请求。这些中断源由内部外设提供,例如DMA控制器、UART、IIC等。在这些中断源中,UARTn、AC97和外部中断EINTn对于中断控制器来说是或逻辑。

1.8 ADC和触摸屏接口

S3C2400A有10位ADC(模数转换器),它是有8通道模拟输入的循环类型设备。其转换模拟输入信号到10位的数字编码,最大的转化率是在2.5 MHz转换时钟下达到500KSPS。AD转换器支持片上采样和保持功能及掉电模式。

触摸屏接口可以控制或选择触摸屏触点用于XY的坐标转换。触摸屏接口包括触摸触点控制逻辑和有中断产生逻辑的ADC接口逻辑。

1.9 实时时钟

实时时钟(RTC)单元在系统电源关闭的情况下可以在备用电池下工作。RTC可以使用STRB/LDRBARM操作传输二进制码十进制数的8位数据给CPU。数据包括秒、分钟、小时、日期、天、月、年的时间信息。RTC单元可以在32.768 kHz的外部晶振下工作,可以执行报警功能。

1.10 看门狗定时器

S3C2400A的看门狗定时器是用于当例如噪音或系统错误引起的噪音时,恢复控制器操作。其作为一个普通的16位时间间隔定时器来请求中断服务。看门狗定时器产生一个128PCLK周期的复位信号。看门狗定时器的特点是:1)有中断请求的普通间隔定时器模式;2)当定时器计数器值为0(超时)时,对于128个PCLK周期内的复位信号被激活。

1.11 IIC总线接口

S3C2400ARISC微处理器可以支持多主设备IIC总线串行接口,专用串行数据线(SDA)和串行时钟线(SCL)承载主设备和连接IIC总线的外围设备之间的信息。SDA和SCL线都是双向的。在多组设备IIC总线模式下,多个S3C2400A微处理器可以从从属设备中接收或发送串行数据。主设备S3C2400A可以初始化和终止一个基于IIC总线的数据传输。在S3C2400A中的IIC总线使用标准总线仲裁步骤。

1.12 IIS总线接口

S3C2400A的Inter-IC Sound(IIS)总线接口作为一个编解码接口连接外部8/16位立体声音频解码IC,IIS总线接口支持IIS总线数据格式和MSB-justified数据格式。该接口对FIFO的访问采用了DMA模式取代中断。它可以在同一时间接收和发送数据。

1.13 SPI(串行外围设备接口)

S3C2400A的SPI接口可以接口串行数据传输。S3C2400A包括两个SPI接口,每个接口分别有两个8位的数据移位器用于发送和接收。在SPI发送期间,数据同时发送和接收。SPI的特点是支持两个通道的SPI、兼容SPI协议(2.11版本)、8位发送移位寄存器、8位接收移位寄存器、8位预定标器、查询,中断和DMA传输模式、容忍5 V输入,除nSS。

1.14 AC97控制器

S3C2400A的AC97控制器单元支持AC97的2.0版本特点。AC97控制器使用一个音频控制器连接 (AC-link)来和AC97编码器通讯。控制器发送立体声PCM数据给编解码器,编解码器中的外部数模转换器转换音频采样到模拟音频波形。控制器也从编解码器接收立体声PCM数据中单声道的MIC数据,然后将数据存在内存中。AC97控制器的特点:对于立体声PCM输入,立体声PCM输出和单声道MIC输入都有独立的通道、基于DMA的操作和中断的操作、所有通道仅支持16位采样、不同采样率的AC97编解码器接口(48 kHZ及以下)、每个通道有16个入口FIFO、仅支持主编解码器。

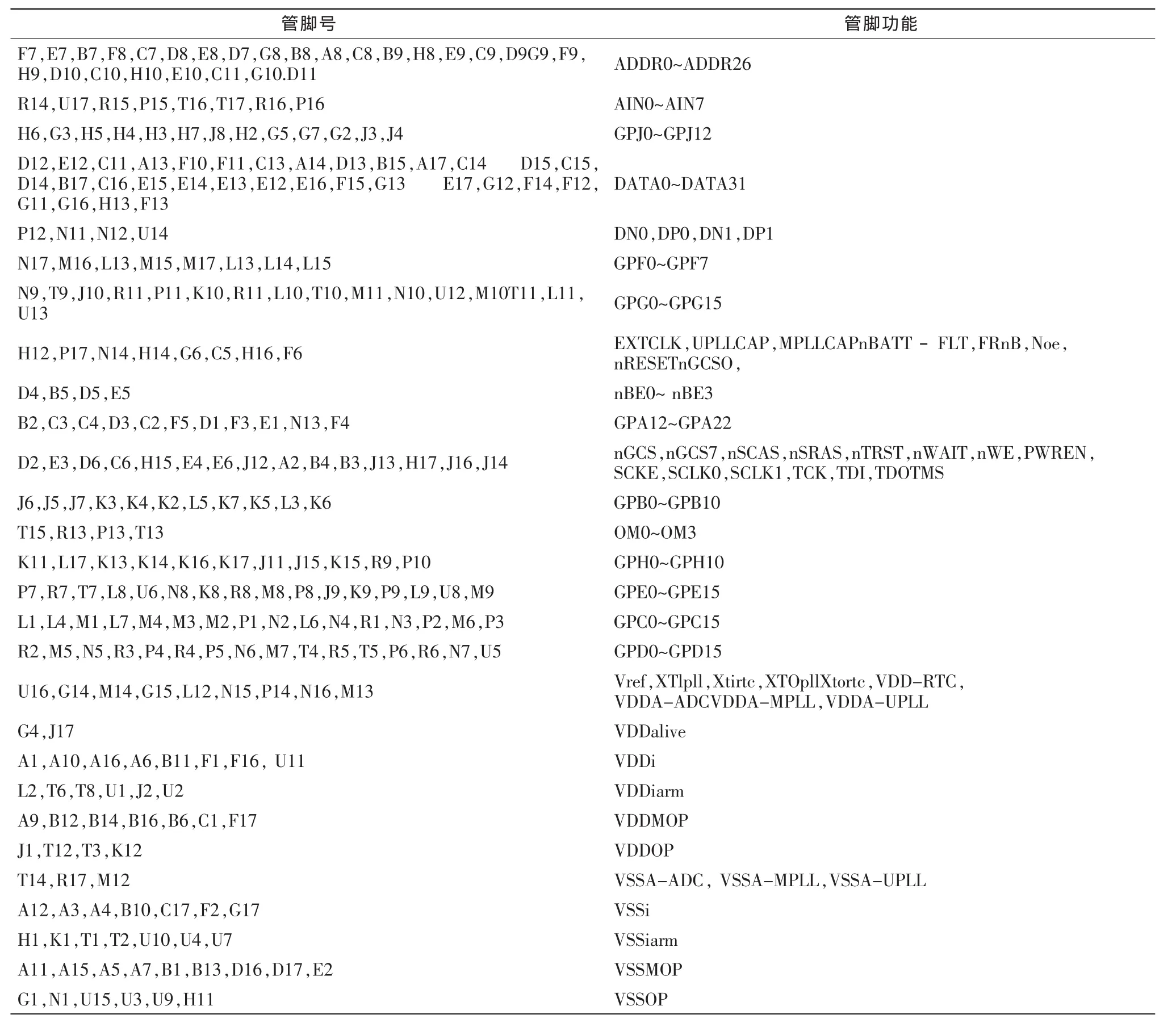

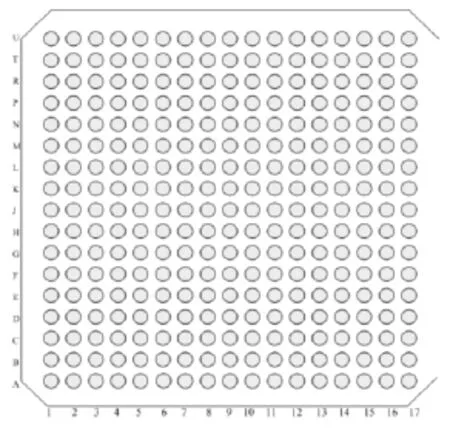

2 引脚功能

该管脚从左到右依次为1~17,从下到上依次为A、B、C、D、E、F、G、H、J、K、L、M、N、P、R、T、U。 管脚功能如表 1 所示。

S3C2440A共有289个管脚,采用的是FBGA封装[1]。它的管脚排列如图2所示。

表1 管脚功能Tab.1 Pin function

图2 管脚排列Fig.2 Pin assignment

其中GPF、GPG为中断,TDI为测试数据输入,TDO为测试数据输出,TMS为测试模式选择,nGCS为一般的芯片选择。

3 应用举例

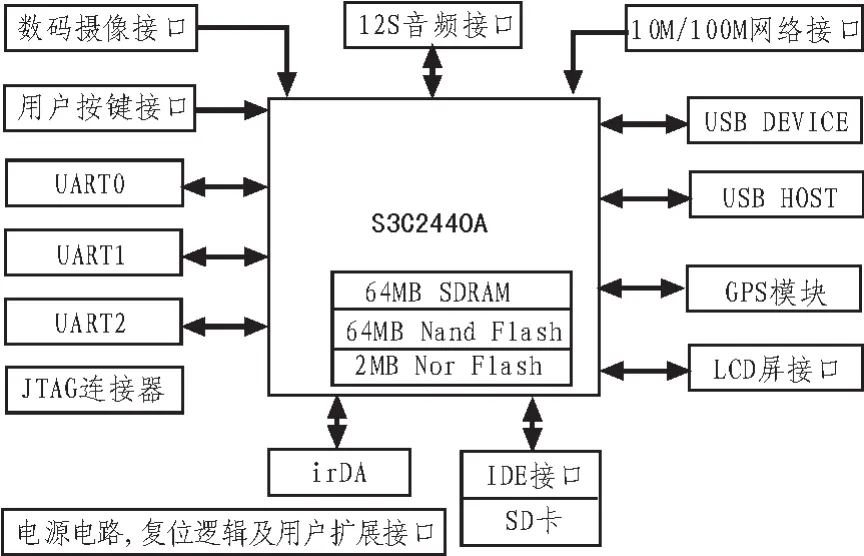

以S3C2440A为核心设计的YLE2440W开发板的结构如图3所示,该开发板外接了GPS模块,串口,两个外扩串口,网络接口,USB接口,WLAN模块,红外通信口,音频接口,存储接口,LCD和触摸屏接口和摄像头接口等[6]。其中S3C2440A具有27个地址端口,有32位数据端口,8位的模数转换器,并包含时钟电源等。该开发板的硬件连接如图3所示。

图3 YLE2440W内部结构Fig.3 Internal structure of YLE2440W

S3C2440A通过图4的方式和YLE2440W上的外围设备进行连接,其中 JTAG 和 nTRST,TCK,TDI,TDO,TMS 管脚连接,用来传输数据。UART以图4的方式管脚连接,用来数据传输,数据接收,中断生成,波特率生,红外模式自动流控制。SDRAM为芯片扩展的同步动态随机存储器。其他的管脚如图的方式连接。该开发板采用的是linux2.6的内核,支持RTC时钟。S3C2440 A支持启动模式,从NAND FLASH 启动和从NOR FLASH启动。基于YLE2440W开发板设计了导航装备信息管理接口[7],通过S3C2440 A的串口获取装备的数据,在片内进行数据处理以及协议转换,通过S3C2440 A外接的LCD显示屏进行数据显示。JTAG口进行程序的下载。

4 结束语

利用基于S3C2440A设计的开发板进行功能开发,方便简洁灵活,因为本身带有外设扩展口,所需外围芯片数量少,功耗低,体积小,非常适合于对体积以及功耗要求高的应用中。

图4 YLE2440W的电路图Fig.4 Circuit diagram of YLE2440W

[1]三星电子有限公司.S3C2440A微处理器芯片用户手册[S].2007.

[2]陈章龙,涂时亮.嵌入式系统—Inter StrongARM结构与开发[M].北京:北京航空航天大学出版社,2003.

[3]周立功.ARM微控制器基础与实战[M].北京:北京航空航天大学出版社,2003.

[4]马忠梅,马广云,徐回应,等.ARM嵌入式处理器结构与应用基础[M].北京:北京航空航天大学出版社,2002.

[5]Steve F.ARM SoC体系统结构[M].田泽,于敦山,盛世敏,译.北京:北京航空航天大学出版社,2002.

[6]深圳市优龙科技有限公司.YLE2440W开发板使用手册[S].2009.

[7]曹国鑫.基于ARM的导航装备信息管理接口研究[D].西安:空军工程大学电讯工程学院导航工程系,2010.