基于FPGA的以太网MAC控制器的设计与实现

2011-06-05丁世勇谭文文李桂英

丁世勇,谭文文,李桂英

(1.山东科技大学 信息与电气工程学院,山东 青岛 266510;2.山东科技大学 理学院,山东 青岛 266510)

随着网络的飞速发展,因特网(Internet)在人们的生活中占据着越来越重要的地位。目前,以太网802.3协议和TCP/IP协议是嵌入式系统接入Internet的首选协议。而以太网(Ethernet)的核心思想是通过带冲突检测的载波侦听多路访问协议(CSMA/CD)[1]来控制对介质的访问以实现多用户共享传输信道。根据OSI网络七层参考模型,以太网对应模型中的数据链路层和物理层,并把数据链路层分为逻辑链路层(LLC)和介质访问控制层(MAC)。以太网技术主要集中在物理层(PHY)和介质访问控制层(MAC)的实现上,MAC子层协议是数据帧收发的基础,负责上层数据和物理层比特流的封装和解封、流量控制以及差错校验等功能,是以太网控制器的核心。

1 总体设计方案

以太网MAC控制器由5个主要部分组成,如图1所示:主机接口模块,发送模块,接收模块,控制模块和MII(Media Independent Interface)管理模块。主机接口包含AHB总线的master和slave接口,提供以太网控制器与上层协议之间的接口,用于数据的接收、发送以及对控制器内的寄存器的设置,发送和接收模块主要提供MAC帧的发送和接收功能,直接提供了到物理层芯片(PHY)的并行数据接口。MAC控制模块用于执行全双工模式下的流量控制。MII管理模块提供了介质独立接口用于连接数据链路层和物理层。

图1 以太网MAC控制器的主要组成部分Fig.1 Main component of Ethernet MAC controller

2 发送模块

2.1 以太网数据帧格式

以太网数据帧格式[2]如图2所示,前导码的字段长度为7 b,内容为“101010..1010”;帧起始符字段长度为 1 b,内容为“10101011”;标志数据帧信号的开始;目的地址字段长度为7 b,可以为单播地址,多播地址或广播地址;源地址字段长度为6 B,表示发送方的MAC地址;长度/类型字段长度为2 B,如果该值小于802.3协议规定的最大帧长度,则表示数据字段的字节个数,如果大于最大帧长度则表示上层使用的协议;数据/填充字段的长度为46~1 500 B,表示数据字段的字节数,若小于46 B,需要添加填充字段,确保数据字段的长度达到协议规定的最小长度46 B;校验码字段长度为4 B,采用CRC校验,计算范围从目的地址到数据填充字段。

图2 数据帧格式Fig.2 Data frame format

2.2 数据发送模块

数据发送模块根据从主机接口发出的帧开始(TxStartFrm)和帧结束(TxEndFrm)信号,从存储器中获取相应的数据,对其进行数据帧格式的封装后,根据CSMA/CD协议,在信道空闲的时候把数据以半字节的形式传输给PHY。最后由PHY发送到网络上。

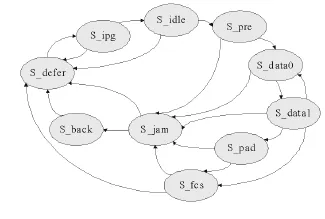

发送状态机模块是数据发送模块的核心,控制着整个发送过程,发送状态机一共有10个状态:S_idle、S_pre、S_data0、S_data1、S_pad、S_fcs、S_ipg、S_jam、S_back、S_defer。 其状态转移图如图3所示。

图3 发送状态机状态转移图Fig.3 State transfer diagram of transmitting state machine

系统复位后,状态机进入S_defer状态。当载波侦听信号(CarrierSense)变成无效时,状态机进入S_ipg状态。在等待一个帧间间隙(≥96个比特时间)[3]之后,状态机进入S_idle状态。如果在帧间间隙的前2/3个周期检测到信道忙则返回S_defer状态。在空闲状态下,当主机向发送模块发出帧起始信号(TxStartFrm),且载波空闲时,状态机进入S_pre状态。输出使能信号(MtxEn)有效并开始向PHY发送数据,7 B前导码发送后,发送1 B的帧起始符。之后状态机进入S_data0状态,发送模块将发送一个数据字节的低4位。之后状态机进入S_data1状态,发送模块则发送字节的高4位。之后,状态一直在S_data0和S_data1之间循环,直至数据发送完毕。还剩下最后一字节时,主机会发送帧结束信号(TxEndFrm)通知发送模块。如果帧长度大于或等于最小帧长度(在PACKETLEN寄存器中定义),并且循环冗余码校验(CRC)开启,状态机进入S_fcs。发送完32比特的校验码后,状态机进入S_defer状态,然后循环又重新开始。如果CRC不开启,状态机直接从S_data1转入S_defer状态。

如果数据帧的长度小于最小帧长度,状态就进入S_pad状态,发送模块根据系统设置来决定是否添加填充码,然后进入S_fcs状态。如果数据帧的长度大于最大帧长度,发送模块根据设置决定是否发送超长帧,如果不支持,状态机直接进入S_defer状态。

在发送数据过程中,发送模块会一直检查冲突检测信号。如果发现冲突且状态机正处于S_pre状态,状态机在发送完前导码和帧起始符后进入S_jam状态,并发送拥塞码,然后进入S_back状态,以等待重试。之后状态机经S_defer和S_ipg回到S_idle状态。如果重试计数器没有达到重试最大值,发送模块将重新开始发送刚才的帧;如果发现冲突时状态机处于S_data0、S_data1或S_fcs状态时,且没有超过冲突时间窗,状态机马上进入S_jam状态并发送拥塞码,依次经过 S_back、S_defer、S_ipg回到S_idle,并根据重试计数器的值决定是否重新发送刚才的数据帧;如果检测到发生冲突的时间超过了冲突时间窗,状态机将进入S_defer状态,经S_ipg到S_idle状态,并放弃重试。

在全双工模式下,发送数据帧过程中不会产生冲突。此时,发送模块将忽略PHY的载波侦听和冲突检测信号,但帧与帧之间仍然要遵守帧间间隙规则,因此,全双工模式下的发送状态机没有S_jam、S_back和S_defer 3个状态。

3 接收模块

该模块的主要功能是接受物理层输出的半字节数据,并转换成字节形式,判断接受帧的各个字段,去除前导码和帧起始符,对接受帧的目的地址进行检查,对接受数据帧进行CRC校验,根据校验结果判断是否接收数据[4]。

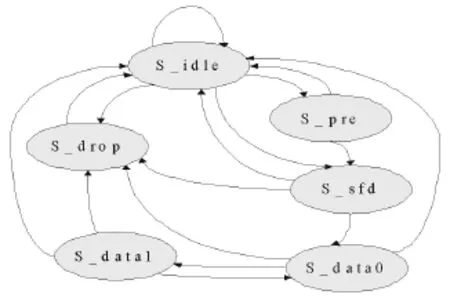

接收状态机模块是数据接收模块的核心,控制着整个接收过程, 接收状态机一共有 6个状态:S_idle、S_pre、S_sfd、S_data0、S_data1、S_drop。其状态转移图如图4所示。

图4 发送状态机状态转移图Fig.4 State transfer diagram of receiving state machine

系统复位后,接收状态机进入S_drop状态,如果接收使能信号(MRxDV)无效,状态机进入S_idle状态,并一直处于S_idle状态等待输入帧。一般情况下接收模块在接收数据包之前会检测前导码,标准的前导码7 B长,之后是1 B的帧起始符。由于以太网控制器也支持接收不带前导码只有帧起始符的数据帧。所以,当MRxDV有效时,判断接收到得数据MRxD是否为0x5,如果不是,状态机进入S_pre模块,并且一直处于S_pre状态直至MRxD为0x5时状态机转入S_sfd状态。当MRxD为0xd且表示前后两帧间隙是否满足规定的信号IFGCounterEq24有效时,状态机进入S_data0状态以接收字节的低4位,之后进入S_data1状态以接收字节的高4位。直至数据传输完毕,PHY芯片使MRxDV无效,状态机进入S_idle。如果两帧间隙不满足规定,状态机直接从S_sfd状态进入S_drop状态,直到MRxDV无效时进入S_idle状态,循环重新开始。另外当状态机处于 S_pre、S_sfd、S_data0或S_data1时只要MRxDV变成无效,状态都进入S_idle状态。

4 MII管理模块

4.1 以太网管理帧格式

MII对物理层寄存器的操作是通过发送管理帧来实现的,管理帧格式[5]如图5所示。前导码字段长度为4 B,全为1,已使物理层与数据同步;帧起始符字段长度为2 b,值为“01”;操作码字段长度为 2 b,“01”表示写操作,“10”表示读操作;物理层地址字段长度为5 b,表示物理层地址;寄存器地址字段长度为5 b,表示物理层内部的寄存器地址;转换码字段长度为2 b,表示数据输入或输出,读操作时转化码为“Z0”,写操作时,状态为“10”;数据字段长度为 2 b,表示写入或读出的寄存器的值。

图5 管理帧格式Fig.5 Management frame format

4.2 MII管理模块

MII管理模块提供了与外部PHY芯片交互的接口,可以对PHY里的配置寄存器进行设置或读出寄存器的状态。接口有两个信号组成:时钟信号 (MDC)和双向数据信号(MDIO)。MDIO有输入信号Mdi,输出信号Mdo以及输出使能信号MdoEn组成。MII管理模块包含3个子模块:时钟产生模块,移位寄存器模块和输出控制模块。

时钟产生模块产生时钟信号Mdc用于与PHY通信,设置Mdc的频率时要参照外部PHY芯片的说明。可通过设置MIIMODER寄存器来设置Mdc的分频系数。

移位寄存器作用是在输出数据时把并行数据一位一位串行的输给外部PHY,接收输入数据时把串行数据转化为并行存入MIIRX_DATA寄存器。

输出控制模块主要是产生输出数据和输出使能信号,虽然MDIO是双向数据信号,但Mdi是输入信号,不属于MAC控制器的一部分,如果在MIIMODER寄存器中设置前导码(Preamble)有效,输出控制模块会在有效数据前产生32比特的前导码

5MAC控制模块

MAC控制模块实现全双工模式下的流量控制功能。当接收站点的接收缓冲区快要溢出或者主机发出流量控制请求时,就会发出流量控制请求至MAC控制模块,MAC流量控制模块在接收到流量控制请求后会发送PAUSE控制帧。数据帧发送端接收到PAUSE帧后,根据帧中的参数设置定时器。PAUSE定时器到之前,发送端将暂停发送数据,从而防止接收缓存溢出。

6 主机接口

主机接口模块为MAC控制器与上层协议模块的接口,可将上层协议模块输入的数据传输到数据发送模块,将数据接收模块接收的数据输出到上层模块,并控制MII管理模块。

主机接口模块内有一组寄存器,可用于存储上层协议对MAC设置的参数以及MAC的状态信息。上层协议对MAC设置的参数包括接受超短帧使能、添加填充码使能、全双工模式或半双工模式、发送和接收使能、帧间间隙的长度、最大帧和最小帧的长度、重试次数限制以及本机的MAC地址等。

7 验证与仿真

利用Modelsim对Ethernet控制器进行了仿真[6],图6为发送状态机的仿真波形。可以看到状态机在S_defer状态时载波侦听信号无效,随即状态机进入S_ipg状态,在等待一个帧间间隙之后,状态机进入S_idle状态,此时,帧起始信号(TxStartFrm)有效,状态机进入S_pre状态,发送完7 B前导码和1 B帧起始符后,状态机进入S_data0,然后在S_data0和S_data1之间循环,直至数据发送完毕。从图6可知设计的时序与802.3规定的时序一致。

图6 发送状态机的仿真波形图Fig.6 Simulation wave chart of transmitting state machine

8 结束语

文中设计的以太网MAC控制器IP可正确接收和发送数据,实现了802.3协议中MAC层的功能,可通过介质独立接口(MII)与以太网物理层芯片相连接,实现半双工和全双工两种工作模式的传输。

[1]Andrew S.Tanenbaum.计算机网络[M].4版.潘爱民,译.北京:清华大学出版社,2004.

[2]龚坚,彭晖,乔庐峰,等.标准802.3以太网MAC控制器的FPGA设计与实现[J].军事通信技术,2005,26(4):21-24.GONG Jian,PENG Hui,QIAO Lu-feng,et al.FPGA design and implementation ofstandard 802.3 ethernetMAC Controller[J].Journal of Military Communications Technology,2005,26(4):21-24.

[3]IEEE Std 802.3,2000 Edition Part3:Carrier sense multiple access with collision detection (CSMA/CD)access method and physical layer specifications[S].USA,LAN/MAN standards Committee of the IEEE Computer Society,2000.

[4]许全泉,胡文江,苏里.基于PFGA的以太网控制器设计[J].电子元器件应用,2007,9(6):21-25.XU Quan-quan,HU Wen-jiang,SU Li.The design of ethernet controller based on FPGA[J].Electronic Component&Device Application,2007,9(6):21-25.

[5]张博,张琨.基于FPGA的以太网MAC控制器的设计[J].科技情报开发与经济,2009,19(27):97-99.ZHANG Bo,ZHANG Kun.The Design of Ethernet MAC Controller based on FPGA[J].Sci-tech Information Developmen&Economy,2009,19(27):97:99.

[6]杨宗凯.数字专用集成电路的设计与验证[M].北京:电子工业出版社,2004:197-205.