基于FPGA高精度浮点运算器的FFT设计与仿真

2011-06-01张雪姣伍萍辉

张雪姣,伍萍辉

(河北工业大学信息工程学院,天津 300401)

FFT作为数字信号处理中的重要的手段之一[1],主要在数字通信、语音信号处理、图像处理、功率谱估计、仿真、系统分析、雷达理论、光学、医学、地震以及数值分析等方面得到广泛应用。基于FPGA实现FFT,具有软件编程的灵活性及电路扩展性强等优点。随着集成电路技术进步和制造工艺水平的提高,FPGA芯片具有的功能越来越强,成为快速实时实现FFT的重要手段[2]。采用基2法完成基于FPGA浮点运算器的FFT。

1 基于FPGA浮点运算器的FFT

1.1 浮点的IEEE标准格式

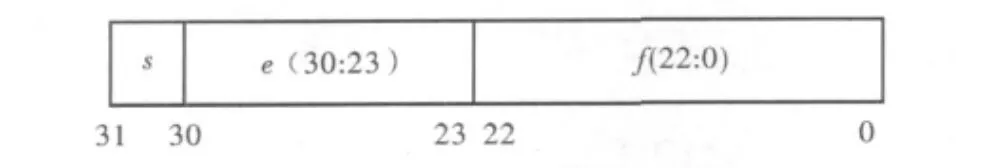

设计采用单精度浮点运算,IEEE定义的二进制浮点格式为32位。结构表示如图1所示。

图1 单精度浮点存储格式

将32位分为3部分[3]:31位为符号位S,S为0时表示正数,为1时表示负数;30~23为指数E,是一个0~255之间的八位二进制数,其实际的指数是E-127,所表示的指数范围是2-127~2128;22~0表示尾数F,小数点前还隐藏了一位‘1’,单精度尾数可表示最大数为2(23+1)=16 777 216。因为 107<16 777 216<108,所以单精度浮点数的有效位数是7位,即浮点数的精度为10-6。为方便FFT的运算,文中采用原码存储。

1.2 基2的DIT-FFT算法

在蝶形运算中采用复数形式表示数据[4]。对于一个2点的蝶形运算,输入复数为A=x+jX,B=y+jY;经A'=A+B,B'=A-B运算,输出复数A'=(x+ycosφ +Ysinφ)+j(X+Ycosφ -ysinφ),B'=[x-(ycosφ +Ysinφ)]+j[X-(Ycosφ -ysinφ)]。

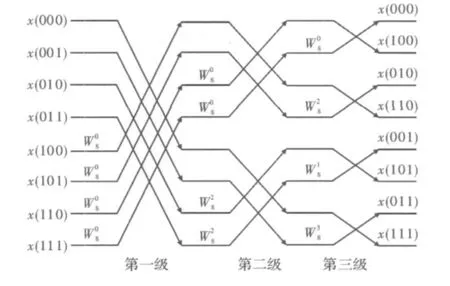

设计主要针对8点FFT进行设计,8点FFT算法的原理图如图2所示。

图2 8点DIT-FFT的蝶形运算流图

整个FFT过程中共有三级蝶形运算,每级蝶形运算有4个蝶形运算单元。在数据输入时按照自然顺序输入,最后倒序输出[5]。

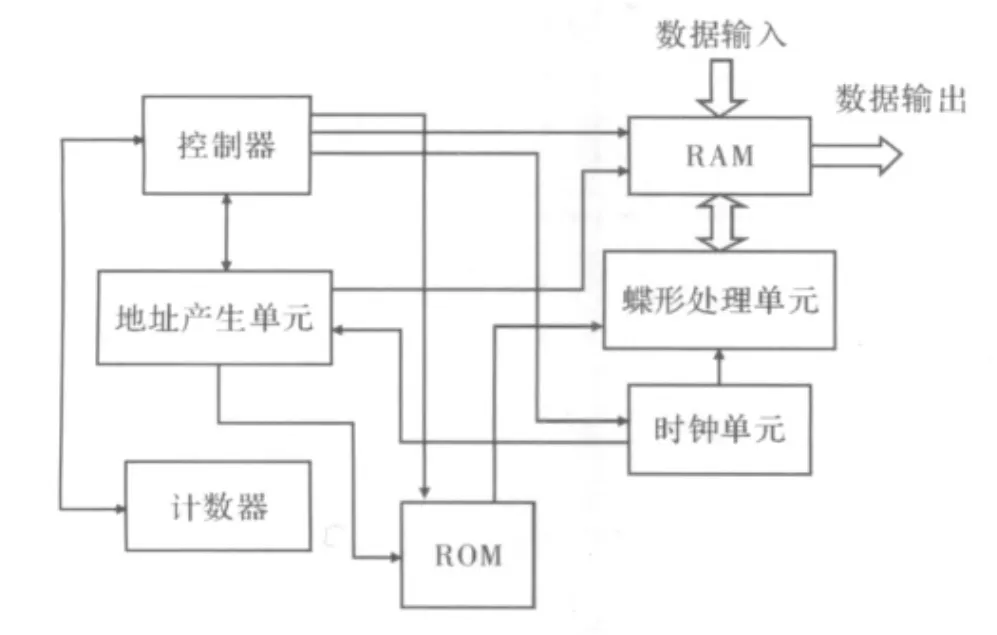

1.3 FFT处理器

FFT处理器主要对数据进行蝶形运算及数据存取。设计采用基2蝶形运算器,包括存储器ROM和RAM,控制器及地址产生单元等。其FFT的结构模型如图3所示。

图3 FFT结构

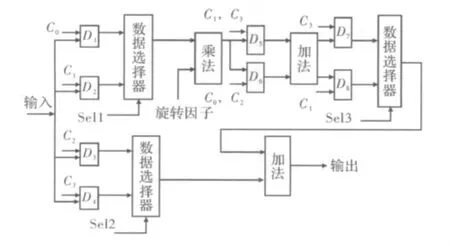

1.3.1 蝶形处理单元

蝶形处理单元是整个FFT的中心环节,采用复数表示,将实部与虚部分别存储,利用基2的DIT-FFT算法实现运算。

图4 蝶形处理单元结构图

蝶形运算过程包括一个乘法运算B和一个加/减法运算A±B。数据的读取由时钟单元的信号来控制:当时钟为c0时,读取y;c1时,读取Y;c2时,读取x;c3时,读取X。经蝶形运算后得到x'=x+(ycosφ+Ysinφ),X'=X+(Ycosφ -ysinφ),y'=x- (ycosφ +Ysinφ),Y'=X-(Ycosφ -ysinφ)然后将数据写入同样地址的RAM中,至此,2点的蝶形运算单元完成。在蝶形运算共需一个乘法器和两个加法器。

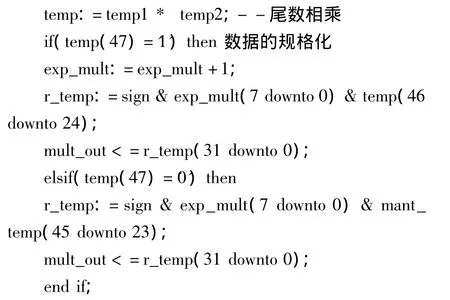

(1)浮点乘法器。乘法过程对浮点数的符号位、指数以及尾数分别进行计算,符号异或,指数相加再减127,尾数加入隐含的‘1’后再进行乘法运算,如果尾数相乘的结果有溢出则指数加1尾数取前23位,若无溢出,则取最高位后的23位。但若输入的数据有一个是0,则输出为0。

图5的波形为两浮点数的乘法运算,输入以16进制表示,分别将不同类型的数据搭配进行测试,结果表示仿真正确。

图5 浮点乘法器的仿真图

(2)浮点加法器。加法运算是将两数指数比较,存储较大的指数,将指数小的尾数移位,再进行加减操作,规格化后输出。加法过程由多个模块组合实现,包括比较模块,右移模块、加/减法模块、前导零检测模块、左移模块和结果整合输出模块。

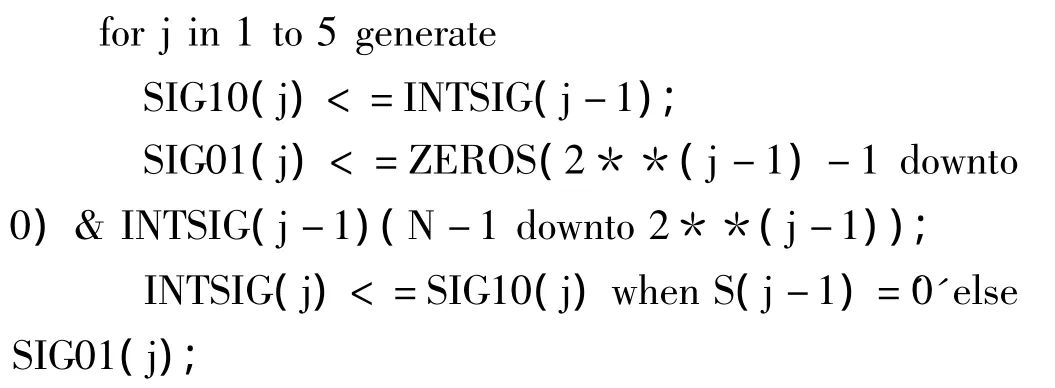

比较模块主要对指数操作,判断指数的大小,较大的指数暂作结果的指数,较小指数的数做移位操作,其阶差为移位量。以下程序采用for循环来实现移位,S(5 downto 0)存储阶差,最大值是32。

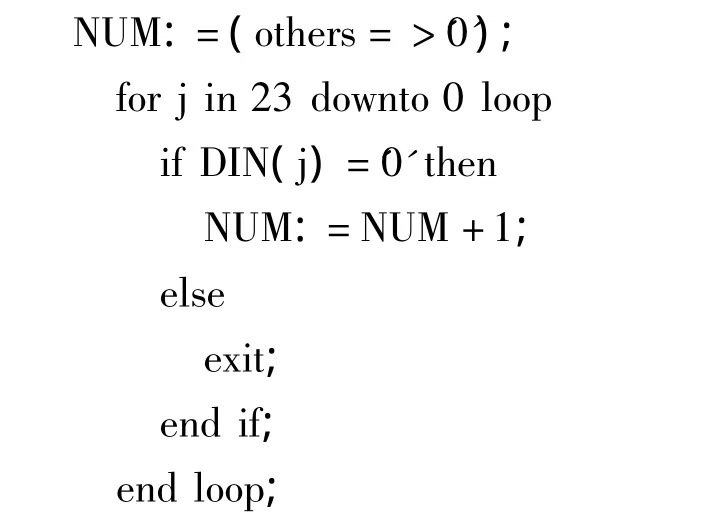

然后尾数经加减运算后规格化并输出,为了以标准浮点格式输出,规格化需要前导零检测。

然后进行移位操作,最后将规格化后的数据整合输出,就完成两个浮点数的加法运算。

图6的波形为两个输入浮点数的加法运算数据,以16进制表示。上述数据分别将不同类型的数据搭配运算,数据表明该仿真结果正确。

图6 浮点加法器的仿真图

1.3.2 地址产生单元

地址产生单元主要是跟踪FFT运算进度,进而更好地调配存储单元,及控制各相关模块的运行。

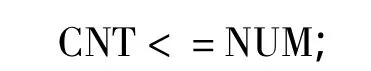

(1)通过计数器来跟踪记录FFT计算的状况。为方便对存储单元操作,采用计数器来记录FFT的计算情况。8点的FFT,每个单元包括4个数据,所以用一个4位计数器Butterfly表示全部的运算状态。一个2位级计数器Stage表示三级蝶形单元。当Butterfly计数为4时,级计数器Stage加1,当Stage计数为3时,表示FFT的计算操作完成。当Butterfly计数为15时,输入输出信号置‘1’,反馈回控制器输入输出操作完成。

(2)ROM读取的地址。旋转因子WkN存储在ROM中,由实部cos(2×k×π/8)和虚部sin(2×k×π/8)两部分组成,读取由时钟单元的信号控制。由图2可以看出每一级参加蝶形运算的旋转因子不同。

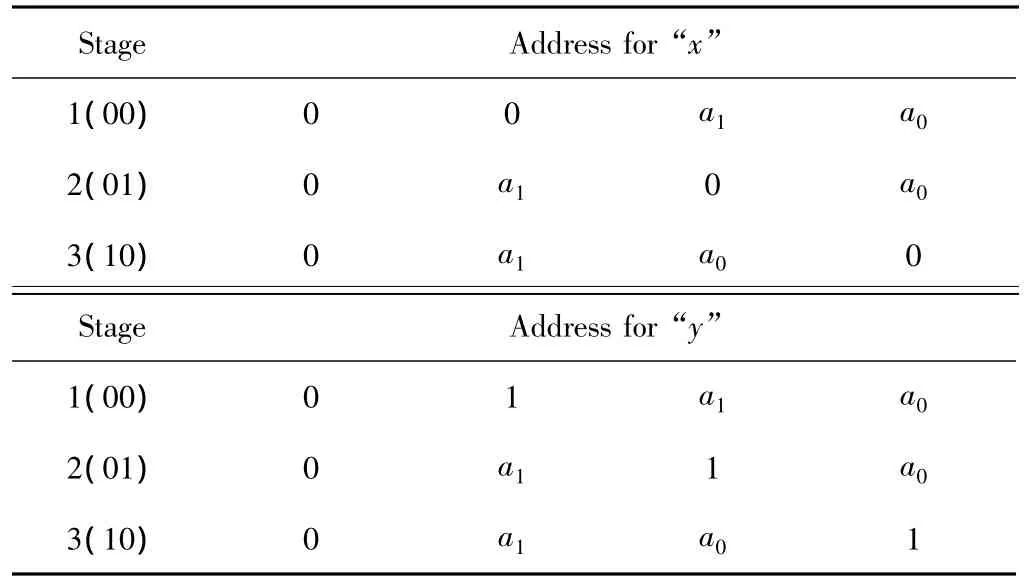

(3)RAM数据地址。在整个地址单元中,分配RAM中数据的地址是重点,8点蝶形运算共需16个存储单元,数据地址的产生遵循一定规则。例如,Butterfly的信号为“a3a2a1a0”,则x,y的地址产生规则如表1所示。

表1 输入数据的地址产生表

数据的读取靠时钟信号来控制。

1.4 FFT仿真结果分析

图7中输入8点数据为[-1,1,2,-0.5,-3,-1,2,0]。仿真结果经转换后,用10进制表示的最后结果为[0,3.76775 - 1.06065i,- 8 - 0.5i,0.23225 -1.06065i,0.5,0.23225+1.06065i,- 8+0.5i,3.76775+1.06065i]。Matlab仿真后结果为[-0.5000,3.7678-1.0607i,- 0.8000 - 0.5000i,0.2322 - 1.0607i,0.5000,0.2322+1.0607i,- 0.8000+0.5000i,3.7678+1.0607i]两结果很接近,误差较小,仿真结果正确。

图7 FFT仿真结果

2 结束语

文中在分析了FFT算法后,描述了运算的蝶形单元,地址生成单元及FFT的实现过程。从实际设计出发,完成了基于FPGA的单精度浮点运算器的FFT设计,精度达到10-6。其输出结果与Matlab仿真结果相近,达到了利用FPGA实现FFT的目的。

[1]程佩青.数字信号处理教程[M].2版.北京:清华大学出版社,2001.

[2]马强.基于FPGA的快速傅里叶变换实现[D].南京:南京理工大学,2005.

[3]IEEE Orgnzation.IEEE Standard for Binary Floating - Point Arithmetic,ANSI/IEEE Std 754 - 1985[S].USA:IEEE Orgnzation,1985.

[4]BAESE M U.数字信号处理的 FPGA实现[M].2版.刘凌,译.北京:清华大学出版社,2006.

[5]胡广书.数字信号处理理论、算法与实现[M].北京:清华大学出版社,2003.