基于8051核的高精度多通道数据采集系统设计

2011-05-31李江达

杨 兵,陶 伟,李江达

(1.江南大学物联网学院,江苏 无锡,214122;2.中国电子科技集团公司第58研究所,江苏 无锡,214035)

1 引言

数据采集系统广泛应用于工业、农业、军事及日常生活等各个领域。通常对数据采集系统的要求是速度快,精度高,存储容量大,抗干扰能力强,能实时记录数据采集的时间,并能灵活选择数据输出的方式,而采用普通的数据采集系统很难满足上述要求。该文介绍了一种以8051核为核心、配合大容量存储器和各种通用外设所构成的数据采集系统的单芯片SOC设计方法。

2 系统设计

该系统(如图1)是高度集成的高精度12位数据采集系统。系统组合了带有片内可重新编程非易失性FLASH存储器的高性能8051核,它用于控制多通道的12位DAC和12位ADC以及处理采集数据;它还组合了全部辅助功能模块以充分支持可编程的数据采集核心,这些功能模块包括FLASH数据存储器、看门狗WTD、电源监视器PSM以及各种标准并行和串行接口。

系统主要工作流程:

(1)根据数据采集系统实际应用情况,向8kb的程序存储器烧写用户程序;

(2)根据用户程序配置相应的各种外设,包括8通道的DAC以及8051 CORE的各种通用外设;

(3)被选择的速率为200ksps的12位ADC进行有效的数据转换;

(4)采样数据或者加工处理后的采样数据可以选择性地存储在RAM中或者640B的FLASH中;

(5)根据具体应用情况,8051核可以对采样数据进行处理;

(6)采样数据或者加工处理后的采样数据可以选择性地存储在片内存储器中或者通过8051核的外设通道直接送出。

3 子模块设计

3.1 8051核

(1)工作频率12MHz(最大16 MHz);

(2) 3个16位定时器/计数器;

(3) 32条可编程的I/O线;

(4) 高电流驱动能力;

(5) 9个中断源,2个优先级;

(6) 8kB片内FLASH程序存储器,640B片内FLASH数据存储器和片内充电部分;

(7) 16MB外部数据地址空间和64kB外部程序地址空间;

(8)片外UART串行I/O,I2C总线和SPI总线;

(9) 片外看门狗定时器和电源监视器;

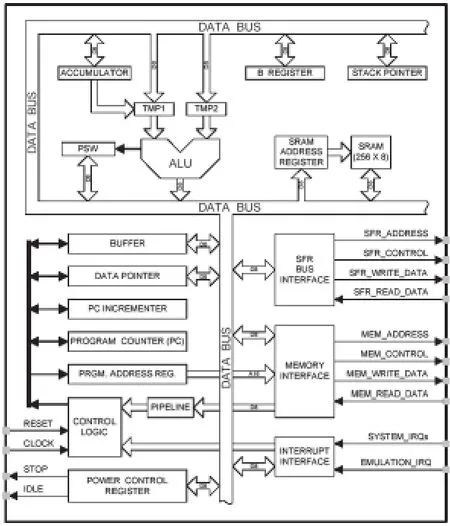

(10)8051核有三条总线,与内部数据RAM的数据传输通过IRAM BUS,与内部程序ROM的数据传输通过IROM BUS,与外部存储器的数据传输通过MEM BUS,而与外设之间的数据传输是通过SFR BUS来实现的。电路基本结构如图2。

3.2 存储器组织

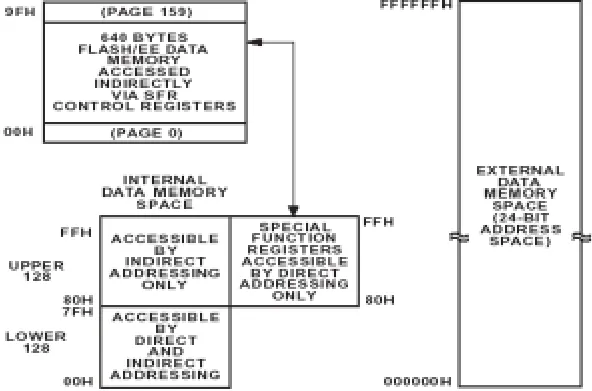

与所有8051兼容的器件一样,对于程序和数据存储器,该系统具有分开地址空间,如图3、图4所示。

图2 8051核电路结构

图3 程序存储器空间

图4 数据存储器空间

内部数据存储器的最低32字节分为8个寄存器(R0到R7)的4个组;寄存器组上紧接的16个字节构成了位可寻址的存储器空间块,位地址从00H到7FH;而SFR空间映射到内部数据存储器空间的高128字节。SFR区仅通过直接寻址来访问并提供CPU和所有片内外围设备之间的接口。

3.3 ADC模块

3.3.1 基本工作原理

ADC转换块包含了5μs / 8通道12位单电源A/D转换器。此模块为用户提供多通道多路转换器、跟踪/保持、片内基准、校准特性以及A/D转换器,并且模块内所有部件都能方便地通过3-寄存器SFR接口来设置。

A/D转换器由基于DAC的常规逐次逼近转换器组成,转换器接收的模拟输入范围为0至参考电压Vref。片内提供高精度、低漂移并经过工厂校准的2.5V基准电压。片内基准可经外部Vref引脚过驱动,外部基准可在2.3V到AVDD的范围内。在此范围内,设计的代码跳变发生在连续的整数LSB值的中间(即1/2LSB,1/2LSB,1/2LSB—— FS-3/2LSBs)。当Vref=2.5V时,输出码是直接的二进制数,1LSB=FS/4096或2.5V/4096=0.61mV。在0到Vref范围内理想的输入/输出转移特性如图5所示。

图5 AD输入输出转移特性

用软件或者通过把转换信号加到外部引脚CONVST可启动单步或连续转换模式,也可以设定定时器2来产生用于ADC转换的重复触发信号,也可以配置ADC以便工作在DMA模式,因此ADC块连续转换并把采样值捕获到外部RAM空间不需来自MCU核的任何干扰,并且这种自动捕获功能可以扩展到16MB外部数据存储器空间。

系统设计芯片装有工厂编程的校准系数,它在上电时自动下载到ADC,以确保最佳的ADC性能。ADC核包括内部失调和增益校准寄存器,所提供的软件校准子程序可允许用户在需要时重写工厂编程的校准系数,以便使用户目标系统中端点误差的影响最小。

来自片内温度传感器的电压输出正比于绝对温度,它也可以通过前端ADC多路转换器(实际上是第九个ADC通道输入)传送,这方便了温度传感器的实现。

3.3.2 基本功能电路

ADC的工作状态完全由3个SFR寄存器控制:ADCCON1寄存器控制ADC的转换和采集时间,硬件转换模式和掉电模式;ADCCON2寄存器控制ADC的通道选择和转换模式;而ADCCON3寄存器对用户软件给出ADC忙状态的指示。

3.4 并行I/O端口

该系统使用4个通用数据端口与外部器件交换数据。除了实现通用I/O外,某些端口能实现外部存储器操作;其他端口则与器件上外围设备其他功能多路复用。端口0、2和3是双向端口,端口1只是输入端口。所有端口都包含输出锁存器和输入缓冲器,I/O端口也包含输出驱动器。对端口0~3引脚的读和写访问通过它们对应的特殊功能寄存器SFR来实现。

图6 12位ADC功能电路

3.5 串行I/O端口

UART是全双工的,可以同时发送和接收数据,通过8051核可以配置为四种工作模式之一;而串行外设SPI接口是工业标准的同步串行接口,它允许8位数据同时同步地被发送和接收,系统可配置为主(Master)或从(Slaver)操作;与I2C兼容的串行接口有两个,可配置为软件主(Software Master)或硬件从(Hardware Slave)模式,并且可与SPI串行接口多路复用。

3.6 定时器/计数器

该系统具有三个16位定时器/计数器,每个定时器/计数器都包含两个8位寄存器THx和TLx(x=0、1和2),所有三个定时器/计数器均可配置作为定时器或者事件计数器。在“计数器”功能中,每个机器周期TLx寄存器增量,而在“计数器”中,TLx寄存器根据其对应的外部输入引脚T0或T1上的1到0的跳变增量。

3.7 片内监视器

该系统集成了两个片内监视器功能以便使灾难性的编程或其他外部系统故障期间内代码或数据的破坏最小,并且两个监视器功能完全可通过SFR空间来配置。

3.8 看门狗定时器

看门狗定时器的用途是当该系统可能由于编程错误、电气噪声或RFI而进入出错状态达到适当时间时产生器件的复位。它是通过清除看门狗控制(WDCON)SFR中WDE(看门狗使能)位而永远被禁止。当它被使能时,如果在预定时间间隔内用户程序没有刷新看门狗,那么看门狗电路将产生系统复位,复位时间间隔可通过SFR预定标位在16ms~204ms范围内进行调整。

4 总结

该系统芯片集成了大量的外围设备,是一个可编程、自校正、高精度的数据采集系统,可以取代传统的MCU+A/D+RAM高成本、大体积产品,尤其是它的高精度和高速度A/D模块,特别适应于智能传感、瞬间获取、数据采集和各种通讯系统。

[1] 潘名莲,童义生. 微计算机原理[M]. 北京:电子工业出版社,1989.

[2] 沈美明,温冬婵. IBM-PC汇编语言程序设计[M].北京:清华大学出版社,1991.

[3] [美] L.C.埃格布雷赫编著,孙承鉴等译. IBM-PC微型机接口[M]. 北京:科学技术出版社.