Chirp-UWB通信系统中锁相解调接收机的设计与实现

2011-05-17唐展波樊孝明

唐展波,樊孝明,吴 政,李 昂

(桂林电子科技大学 信息与通信学院,广西 桂林541004)

目前,超宽带(UWB)无线传输技术被认为是未来短距离无线通信最理想的技术。Chirp-UWB信号是瞬时频率随时间做线性变化的正弦波信号,频谱带宽较大,因具有良好的自相关性、经过匹配滤波器后信号宽度压缩、不存在峰均功率比(PAPR)等特点开始吸引更多的关注[1]。然而设计结构简单、复杂度低的Chirp-UWB系统接收机一直是设计的难点之一。对Chirp-UWB信号的解调中多采用匹配滤波的方法,但是该方法具有灵活性差且成本高等缺点。本文研究和设计了一种基于电荷泵的宽带PLL解调Chirp-OOK调制信号的方案。

1 Chirp-OOK调制信号

发射Chirp信号的表达式为:

其中d(t)为发送的基带数据,即

式中,ω0为中心频率,T为基带脉冲的时宽,μ为调频斜率,μ=2πB/T,B为调频带宽。发射机采用 Chirp-OOK调制,在发送码元“1”时,整个码元周期内信号频率从580 MHz~710 MHz连续变化;发送码元“0”时,信号在整个码元周期内保持580 MHz的单一频率,从而实现Chirp-OOK调制,其中心频率为645 MHz,带宽B=130 MHz,符合FCC规定的超宽带定义。其中实测发射信号频谱如图1所示。

2 PLL解调电路的设计与实现

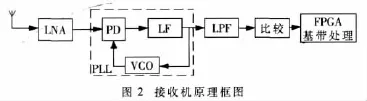

根据发射机的调制方式,文中提出了基于调制跟踪环的解调方案,其原理框图如图2所示。在该方案中让锁相环(PLL)工作在调制跟踪状态,使VCO的输出信号s0(t)的相位可以跟踪输入信号si(t)的相位,从而达到解调的目的。

2.1 PLL解调工作原理

为了分析锁相环(PLL)解调的工作原理,首先必须建立 PLL的线性化相位数学模型[2,3],如图 3所示。

设信号经过空间传输后只是在幅度上引入衰减而没有其他的失真,则在接收端收到的信号可以表示成:

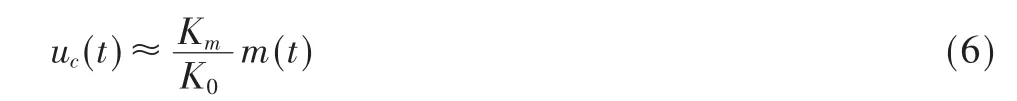

式中θi(t)=Kmm(t)/p为 si(t)的瞬时相位偏移,其中Km为si(t)的调频灵敏度,单位为rad/(s·V)。为分析方便且不失一般性,设R=1,N=1。由图3可得

对式(4)进行傅里叶变换得

可见,直接由uc(t)输出达到解调的目的。

2.2 环路参数的设计

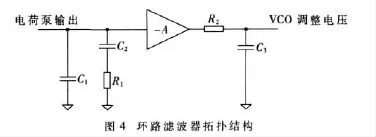

锁相环解调的成功与否,关键在于环路滤波器的设计,环路滤波器设计的好坏将直接影响到后续电路的信号处理。由于环路要工作在调制跟踪状态,而环路的输入信号为相位加速度信号,要使环路能跟踪上这类信号,环路滤波器必须含有理想的积分环节,此时的环路为二型环。采用电荷泵输出的锁相环结构易于设计成比较理想的二型环,故这类锁相环得到了广泛的应用。然而在设计环路滤波器之前必须首先确定环路滤波器的拓扑结构,在带电荷泵输出的锁相环中多采用无源环路滤波器,与有源环路滤波器相比它具有价格低廉、电路简单、带内噪声少的优点,然而在一些应用中由于VCO需要更高的调谐电压,而当PLL的电荷泵的输出电压不能达到设计所需的要求时,就必须使用有源环路滤波器来满足所需的控制电压。为了更好地降低由于有源器件的引入而增加的带内噪声,典型的有源三阶环路滤波器其拓扑结构如图4所示[4]。

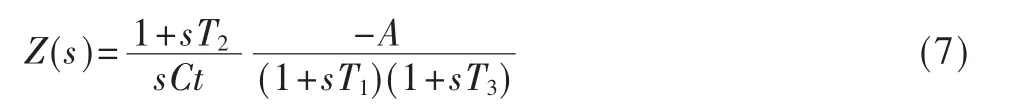

二阶环路滤波器通过计算可得到环路阻抗的准确数学表达式,而三阶或更高阶次的环路滤波器就不可能精确得到它们的阻抗表达式,但是可以通过引入一些近似处理仍然可以得到其阻抗的近似精确的表达式。虽然这类环路滤波器中因运放所处的位置不同使得阻抗计算的方法有所不同,但在图4所示的结构中,由于运放的隔离作用,可以很方便准确地表示出极点、零点与元件的关系。采用这类环路滤波器的阻抗都可以表示成式(7)所示的通用形式:

由于选择的电荷泵器件是可编程的,因此可以通过编程来选择电荷泵的输出极性。假设通过编程使电荷泵的输出为负极性,则开环环路增益为

式中:

为了求解环路参数必须确定 Ct、T31、环路带宽ωc和相位裕度θ的值;T31的范围通常在 0~1之间,常取 0.8。而ωc、θ的值则根据设计的具体指标预先指定一个合理的值,对三阶以上的高阶环路工程设计中通常取开环增益过零点处的频率作为设计的环路带宽ωc,相位裕度θ通常取 30°~60°之间,令开环环路增益在环路带宽频率处的模值为1求得Ct值后,则可以按照式(11)得到实际使用的元件值。

由于这种计算方法引入了近似 T1+T3<T2,而C3的值必须大于VCO的输入电容值,以至于不影响VCO的输入电容并能有效滤除有源器件引入的热噪声,通常取CVCO<C3≤C1/5。根据已知的参数,通过计算和仿真就可以得到 C1、R2、C2、R3、C3的值。

应当指出,由于环路采用的是有源环路滤波器,环路中加入运放可以提高输出电压和增益,但同时还会引入热噪声和附加相移。一个选择不理想的运放可以很容易使相位噪声增加10 dB,而运放在某个设计所期望的放大倍数上引入的附加相移将严重影响环路的稳定性,使得按稳定参数设计出来的环路可能无法正常工作。随着集成运放的发展,运放的附加相移可以是正的也可以是负的,因此,在设置相位裕度θ时,需要认真考虑运放附加相移的影响,否则环路可能会不稳定。通常期望在环路滤波器中加入的运放为理想运放。但实际的运放不可能满足设计的要求,因此期望运放的输入阻抗足够大,输出阻抗足够小,噪声系数低,在所期望的放大倍数上引入较小或者不引入附加相移,AD公司的AD820和AD823是一个比较合理的选择。

3 实验结果与分析

设计中采用ADF4112作为鉴相器,将锁相环的中心频率选择为发射信号的中心频率645 MHz,鉴相频率设计为20 MHz,压控灵敏度K0=43.3 MHz/V。考虑到实际发送的码元速率为2 MHz,而环路工作在调制跟踪状态,因此应该在码元速率附近来选择所需的环路带宽,笔者实验测试了4组数据,并以此观察在不同环路带宽的条件下环路对信号解调的影响。在这些条件不变的情况下,测试了环路带宽 ωc分别为 500 kHz、1.5 MHz、2 MHz和4 MHz时各环路的参数,结果如表1所示。

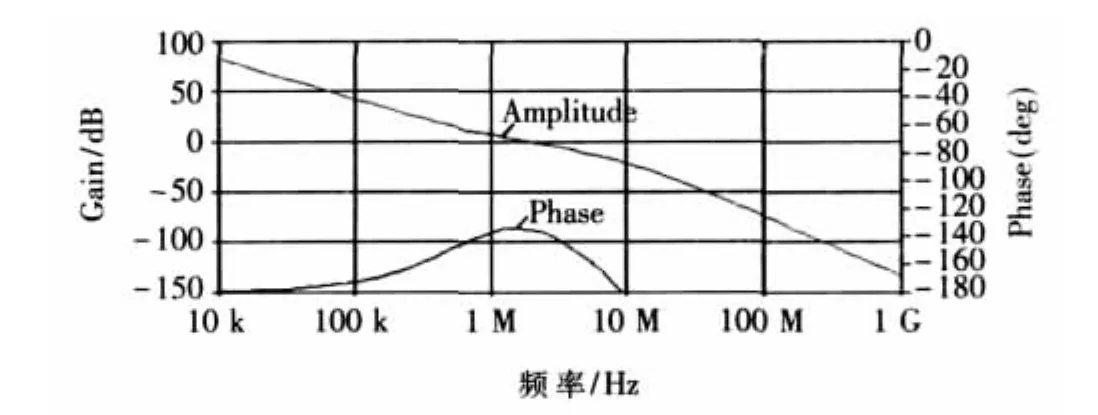

从表1中可以看出,环路带宽越窄,对应的同步带和捕获带也越窄,使得信号跟踪不上环路的最低和最高端的频率,从而产生失真。相反,如果环路的带宽大,环路的同步带和捕获带也大,但是环路的信噪比下降使得环路容易受干扰而产生不稳定。考虑到上述情况,实验选取环路带宽ωc为2 MHz来设计环路的具体元件参数,并在该参数下仿真了环路的开环频率和相位曲线,如图5所示。从图5可以看出,环路开环增益过零点对应的相位裕度大于60°,因此环路在带宽ωc设计在2 MHz时系统是稳定的。

表1 不同环路带宽下环路的参数测试结果

图5 环路的开环频率和相位曲线

环路在带宽ωc为2MHz的条件下,利用安捷伦数字示波器实测解调的波形,如图6所示。

从解调的波形图可以看出,环路在发送连“1”码字时不能快速地下降到0,这是由于发射机采用的是直接调制方式,利用DA芯片产生的锯齿波形去作为VCO的控制电压来改变VCO频率变化,然而实际中运放带宽的限制使得产生的锯齿波不可能从最高点电压快速地下降到所需的低电平,因而产生拖尾,但这不影响信号的解调。实验中采用电荷泵结构的锁相环,其输出是正负脉冲,经过环路后,由于环路的积分作用,环路中电容的充放电跟不上码字的变化速度,使得发送码字在发送一连串的码字“1”时电容放电不充分而一直保持为高电平,但是实际上并不影响解调的过程。相反,可以利用这个特性来解调信号,图6很好地反映了分析的结果。

由于电荷泵型鉴相器与传统的鉴相器有很大的不同,电荷泵的输出信号不仅与相位误差θe有关,在未达到捕获状态时也与频率误差Δω=ω1-ω2有关。 因而它的捕获带宽,捕捉时间短,线性范围大,所以利用它的这些特性设计的宽带锁相环完全有可能跟踪输入信号的变化。实验测试结果显示,接收机检波输出与仿真结果相符合,且检波器输出峰值动态范围较大,利于判决电路选择合适门限。当发射功率为-9 dBm时传输距离能达到5 m,码元速率达到2 Mb/s,数据传输基本正确。实验表明,采用Chirp-UWB的数字通信系统具有发射功率低、信源速率高、抗干扰能力强等优点,适合于复杂多径环境下的超宽带远距离传输。

[1]贺鹏飞,吕英华,张洪欣,等.基于 Chirp-BOK调制的超宽带无线通信系统研究[J].南京邮电大学学报,2006,26(2):23-27.

[2]张厥盛,郑继禹,万心平.锁相技术[M].西安:西安电子科技大学出版社,2003.

[3]郑继禹,林基明.同步理论与技术[M].北京:电子工业出版社,2003.

[4]BANERJEE D.PLL Performance Simulation and Design Handbook(2th Edition)[M].Dog Ear Publishing,2006.