基于N型工艺的基准电压源设计

2011-03-26李仲秋

李仲秋

(空军航空维修技术学院湖南长沙410014)

由于在集成电路中很难制造出具有高精度的电阻,因而不能采用普通的电阻分压方法来获取基准电压。但是利用集成电路具有良好图形对称性的特点可以制造出具有低温度系数和高电源电压抑制比的带隙电压源等基准电压产生电路。它们广泛用于频率合成、A/D、D/A等需要高稳定参考电压源的模拟或模数混合的集成电路中。

然而,在某些只存在N型MOS或者NPN型晶体管的特定工艺中,没有P型器件,难以用传统的带隙电压源结构来产生精确的参考电压,这些工艺中如果需要基准电压,目前的做法都是由外部电路来产生这个电压,这不但增加了整个系统的成本,而且还增加了外围电路的复杂性,不利于系统集成和小型化。

笔者首先介绍了传统互补型工艺中带隙基准电压源的优缺点及局限性,然后阐述了一种可以集成于只有N型有源器件和无源元件工艺中的基准电压产生电路,并分析和测试了此种基准电压源产生电路的特性。

1 传统的带隙基准电压产生电路的特点及局限性

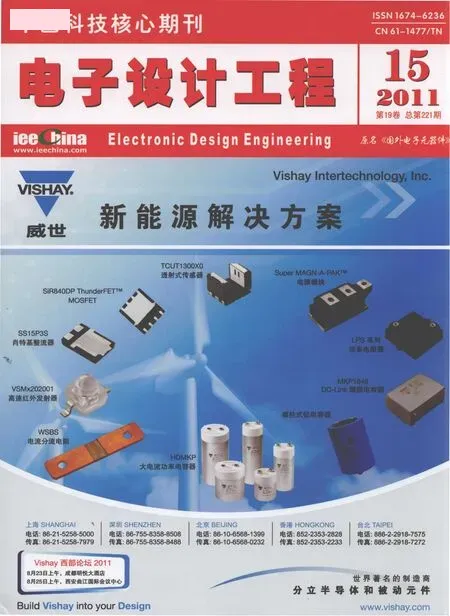

在传统的互补型金属氧化物半导体(CMOS)工艺中,一般采用带隙电压源结构[1-2]来产生参考电压,如图1所示,这是因为在这种工艺中,有带隙电压源电路所需的全部器件,包括N型MOS、P型MOS、PNP晶体管和电阻,这种电路结构所产生的基准电压(VOUT)可表示为为玻耳兹曼常数,T为温度,q为电荷量,n为Q1、Q2的面积比,Vbe为PNP管的结压降,通过调节电阻R2/R1比值和晶体管Q1、Q2的面积比n,可以调节基准电压的输出值和温度特性,这种结构的电路具有良好的温度特性和电源电压抑制比,并且其输出电压与工艺的相关性较小[3-4]。

但是在某些特定工艺中只存在N型MOS或者NPN型晶体管,例如用于射频功率放大器芯片的GaAs HBT工艺和用于射频开关的GaAs pHEMT工艺中均只有N型有源器件和无源元件(包括电阻、电容和电感),由于这些工艺中没有P型器件,很难用图1这种传统的带隙电压源结构来产生精确的参考电压,图1电路只能应该于集成N型器件、P型器件、BE结二极管(由PNP、NPN或直接的二极管组成)和被动元件的工艺中。

图1 传统的带隙基准电压产生电路Fig.1 Conventional bandgap benchmark voltage circuitt

2 N型晶体管基准电压产生电路

2.1 N型晶体管基准电压产生电路的结构和原理

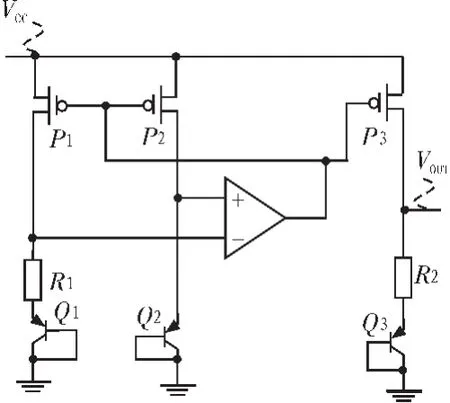

由于在没有P型有源器件的工艺中很难实现如图1所示的带隙基准电压产生电路[5-6],这些工艺中如果需要基准电压,目前的做法都是由外部电路来产生这个电压,这不但增加了整个系统的成本,而且还增加了外围电路的复杂性,不利于系统集成和小型化。为了解决这个问题,图2提供了一种可以集成于只有N型有源器件和无源元件工艺中的基准电压产生电路。

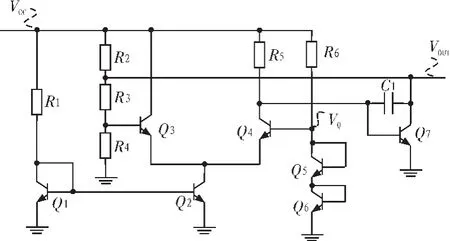

图2 NPN三极管基准电压产生电路Fig.2 NPN transistor benchmark voltage circuit

图2电路主要通过运放反馈的形式来产生基准电压,所采用的器件只有两种,分别为NPN型晶体管和电阻,共包含7个NPN型器件和6个电阻。电阻R1、晶体管Q1产生偏置电流;电阻R6、晶体管Q5、晶体管Q6产生偏置电压VQ;电阻R2、电阻R3、电阻R4产生一个与电源电压VCC相关的分压;晶体管Q2、晶体管Q3、晶体管Q4、和电阻R5组成一个运算放大器,运放的偏置电流由晶体管Q1、晶体管Q2组成的镜像电流源提供,运放的两输入端分别接偏置电压VQ以及电阻R3和电阻R4的分压点,运放比较两输入信号后的输出结果来控制晶体管Q7的基极,晶体管Q7为一个下拉放大管,基极接运放的输出端,集电极接VOUT,即电路的参考电压输出端,晶体管Q7的电流会受到运放比较结果的影响,而晶体管Q7电流的变化会影响电阻R2上的压降,通过闭环环路控制,可以达到调整VOUT的目的。

2.2 N型晶体管基准电压产生电路的性能特点

图2所示的N型晶体管基准电压产生电路所产生的基准电压具有良好的电源抑制比特性,由于运放构成的闭环负反馈控制作用,基准电压受电源电压变化的影响很小,输出的基准电压与电源电压变化的关系仿真结果如图3所示。从仿真结果可以看出:当电源电压变化1 V时,基准电压只变化了0.065 V。说明图2电路具有高电源抑制特性。

图3 基准电压随电源电压变化曲线Fig.3 Benchmark voltage changing curves with power voltage

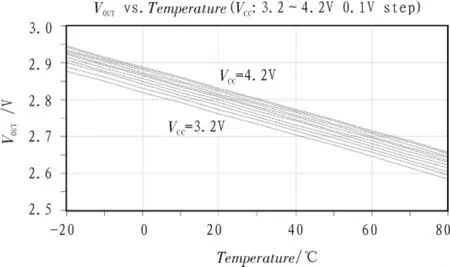

本电路结构由单一的N型器件构成,其输出电压VOUT与N型器件结压降的温度特性一致,具有负温度系数,其仿真结果如图4所示,图4为参考电压随温度变化的曲线(电源电压:3.2~4.2 V,0.1 V间距),从此图可以看出基准电压随温度升高而降低,这与所采用的N型器件的温度特性是一致的。这种特性可以有效地补偿N型器件结压降变化,明显改善应用电路的温度特性。

图4 基准电压随温度变化曲线Fig.4 Benchmark voltage changing curve with temperature

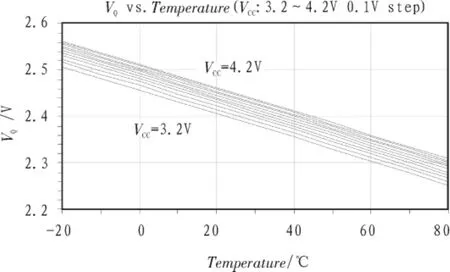

为了说明这种特性的作用,图5是对两个串联二极管(N型)电压(图2中的VQ点)随温度变化的仿真曲线(电源电压:3.2~4.2 V,0.1 V间距),此图与图4的温度曲线变化趋势是一致的。

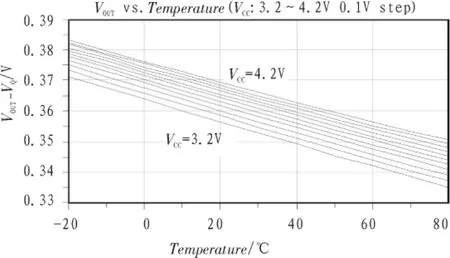

图6为输出参考电压和两二极管串联电压(图2中的VQ点)差值随温度变化曲线(电源电压:3.2~4.2 V,0.1 V间距),从图6可以看出,当温度从-20度变化到80度,发生100度的变化时,输出参考电压和两二极管串联(N型)电压(图2中的VQ点)差值只变化了0.035 V,即使电源电压从3.2 V变化到4.2 V,其温度特性基本相同。因此,综合上述分析与仿真结果可以说明图2电路所示单N型晶体管基准电压源电路其输出参考电压和两二极管串联(N型)电压(图2中的VQ点)差值具有良好的温度特性。

图5 两个串联二极管电压(VQ)随温度变化曲线Fig.5 Two series diode voltage(VQ)changing curve with temperature

图6 Vout与VQ差值随温度变化曲线Fig.6 VQ,Vout and poor value changing curve with temperature

2.3 N型晶体管基准电压产生电路回路稳定性的改善

图7为另外一种改善型的NPN三极管参考电压产生电路,这个电路在图2所示电路的基础上增加了一个补偿电容C1,这个补偿电容与晶体管Q7的BC结并联,通过调节这个电容可以改变环路零极点的分布[7],改善环路的相位裕度,达到提高整个反馈回路稳定性的目的。

图7 带有补偿功能的NPN三极管基准电压产生电路Fig.7 NPN transistors benchmark voltage circuit with compensation function

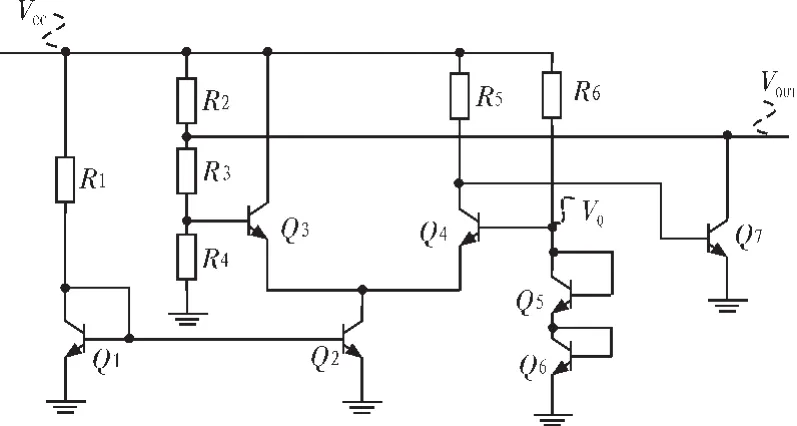

2.4 NPN工艺的基准电压源投片测试结果

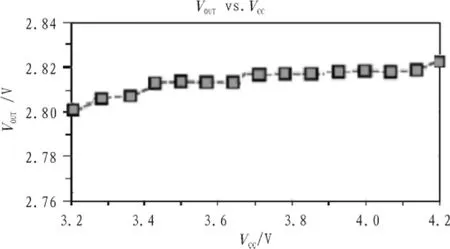

电路采用中芯国际(SMIC)0.18 μm工艺进行了投片(无补偿电容),图8所示是典型样片在不同电源电压条件下的测试结果,输出电压值约为2.76~2.84 V之间。由该结果可以看到,输出的基准电压具有稳定的电源电压抑制能力。

图8 输出基准电压随电源电压变化的测试结果Fig.8 The test results of output benchmark voltage changed with power voltage

3 结束语

在分析传统互补型工艺中带隙基准电压源的优势及局限性的基础上,设计了一种可以集成于只有N型有源器件和无源元件工艺中的基准电压产生电路,并对电路的电源抑制比特性和随温度的变化特性进行了仿真分析;从仿真结果看,此种基准电压源产生电路具有良好的电源抑制比特性和输出的基准电压具有与N型晶体管相同的温度特性,可以达到补偿晶体管工作电流的目的。为只存在N型MOS或者

NPN型晶体管,没有P型器件,难以用传统的带隙电压源结构来产生精确的参考电压的特定工艺,提供了一种基准电压源电路,测试结果表明达到并高于设计指标;本文还提出了改善N型晶体管基准电压产生电路回路稳定性的措施。

[1]Lasanen K,Korkala V,Raisanen-ruosalainen E,et al.Design of a 1-V low power CMOS bandgap reference based on resistive subdivision[C]//Proceedings of 45th IEEE Midwest Symposium on Circuits and Systems.Oklahoma,USA,2002:564-567.

[2]刘军儒,牛萍娟,高铁成,等.一种高精度带隙基准电压源设计[J].现代电子技术,2010,33(2):1-3.

LIU Jun-ru,NIU Ping-juan,GAO Tie-cheng,et al.Design of high precision bandgap voltage reference[J].Modern Electronics Technique,2010,33(2):9-11.

[3]李仲秋.低压COMS带隙电压源[J].半导体技术,2004,29(4):61-64.

LI Zhong-qiu.Low-pressure COMS bandgap voltage source[J].Semiconductor Technology,2004,29(4):61-64.

[4]张彬,冯全源.一种高电源抑制比带隙基准源[J].微电子学,2010,40(1):59-61.

ZHANG Bin,FENG Quan-yuan.A high PSRR bandgap reference circuit[J].Microelectronics,2010,40(1):59-61.

[5]石颖伟,韩良,王科.一种COMS工艺低电压带隙基准源[J].微电子学与计算机,2008(5):185-189.

SHI Ying-wei,HAN Liang,WANG Ke.A COMS process low voltage bandgap benchmark source[J].Microelectronics and Computer,2008(5):185-189.

[6]江金光,王耀南.高精度带隙基准电压源的实现[J].半导体学报,2004,25(7):852-857.

JIANG Jin-guang,WANG Yao-nan.Realization of high precision bandgap reference[J].Chinese Journal of Semiconductors,2004,25(7):852-855.

[7]毕查德.拉扎维(美).模拟CMOS集成电路设计[M].西安:西安交通大学出版社,2003.