基于DSP的地震波信号采集仪设计

2011-03-16姚竹亭顾秀江

王 ,姚竹亭,顾秀江

(中北大学 机械工程与自动化学院,山西 太原 030051)

0 引言

地震测试仪主要用于测量、记录和分析由自然震源或类似于地下爆炸的人工震源发射的地震信号[1]。近年来,其在民用防震减灾工作中的应用也十分广泛,地震测试仪的开发也越来越受到重视。随着地震观测技术的不断进步,对地震检测仪器的分辨率、动态范围、抗干扰能力、多信道以及地震数据处理技术等方面的要求也越来越高。而一批高性能、低功耗和低价格的数字信号处理器的DSP芯片的出现及其与PC通信接口技术的完善,恰恰可以适应目前地震测试设备开发要求。

1 系统总体结构及原理

该系统总体结构见图1。

图1 总体结构框图

DSP处理器是本系统的核心,它负责协调外围电路完成对信号的采集和处理。来自三分量检波器的震动信号经调理电路进行滤波,幅度变换之后,进入带有多路循环扫描的并行A/D芯片;A/D变换后的数字信号接入DSP处理器,在其内部由各种处理算法将信号进行快速运算和处理;最后将处理后的信号通过USB接口器件送入PC,实现进一步的数据分析并完成数据存储和人机交互等功能。

2 硬件设计与实现

2.1 检波器的选择

采用由美国输入/输出公司开发的VectorSeis数字传感器,它是MEMS加速度传感器正交直角安装成的一种超小型三分量数字传感器。可以实现来自传感器的模拟信号到24位数字信号的A/D转换,并含有假频滤波器,采用了数字漂移滤波技术。其采样率有250Hz、500Hz和1000Hz三种模式可选[2]。

2.2 DSP模块电路设计

TMS320VC5402是TI公司为实现低功耗、高速实时信号处理而专门设计的定点数字信号处理器,采用改进的哈佛结构,具有高度的操作灵活性和运行速度,可满足实时嵌入式应用的需要。其内核电压为1.8V,I/O电压为3.3V,工作速率可达100MIPS。片内包括一个JTAG仿真接口、一个控制接口、一个主机接口(HPI)、一个时钟接口、两个多通道缓冲串行接口McBSP0和McBSP1等单元,它的8组16位总线(1组程序总线、3组数据总线和4组地址总线),形成了支持高速指令执行的硬件基础[3]。

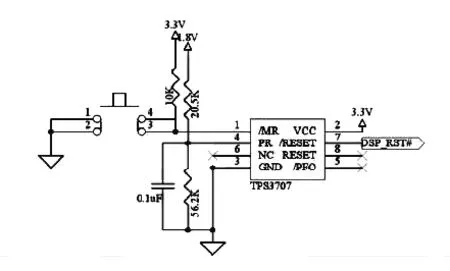

该模块的复位电路采用手动复位方式,采用TI公司的监控电路处理器TPS3707,该芯片无需外加电容就可实现延迟200ms的上电复位功能,将该芯片的RESET#引脚接到TMS320VC5402的RST#上,即可在开关接通的时候使芯片的MR#引脚产生低电平,这时TMS320VC5402芯片就可以完成复位。复位电路原理图见图2。

图2 复位电路

TMS320VC5402可以支持无源晶振和有源晶振两种方式,时钟电路采用精度高、稳定性好、使用方便的有源晶振,选用10MHz。DSP有一组引脚CLKMD1-CLKMD3,可以用来调整DSP的工作频率。

仿真器通过JTAG仿真接口和计算机相连,用户可以通过此接口向DSP芯片加载程序并完成系统仿真及程序调试的任务。它共有14个引脚,其中6引脚悬空,引脚EMU0和EMU1是仿真引脚。

2.3 扩展存储器模块电路设计

考虑到TMS320VC5402有限的片内存储空间(16K×16bit的RAM和4K×16bit的ROM),为了适应大量数据存储和计算的需要,该系统扩展了FLASH程序存储器和SRAM数据存储器。

Flash程序存储器用来存储系统运行的程序代码,可以避免系统掉电时程序的丢失。系统上电时,程序被载入DSP片上的RAM中全速脱机运行,以充分利用DSP对数字信号的高速处理优势。采用SSTVF400A FLASH存储器,它的供电电压是+2.7~+3.6V,数据读取时间为70ns,容量大小为256K×16bit(4MB),存储器内部组织分为区、块、片结构,使用时可分别擦除。

SRAM在系统中主要用作程序的运行空间、数据堆栈区。本设计中,选用了高速、低功耗的64K×16bit的GS71116TP,它采用+3~+3.6V的单电源供电,操作电流小于100mA,不需要外部时钟或时间频闪观测器,存取操作的时间为10ns。

CPLD模块用来实现DSP对Flash和SRAM读写的时序逻辑控制。本系统中采用了Ateral公司的复杂可编程逻辑器件EPM7064芯片。

2.4 电源模块

根据TMS320VC5402的内核电压(1.8V)和I/O电压(3.3V)的要求,采用TI公司的双路低压差电压调整器TPS767D301电源方案。它带有可单独供电的双路输出,一路为3.3V的固定输出,一路可在+1.5~+5.5V范围内可调;每路输出电流的范围为0~1A[5]。将两路调整器的复位输出端并联起来再通过一个上拉电阻与3.3V相连,接到DSP的复位输出端,这样,一旦1.8V或3.3V中任何一个电压下降到其门限电压以下,便产生一个低电平脉冲使DSP复位。

3 基于USB接口的数据传输

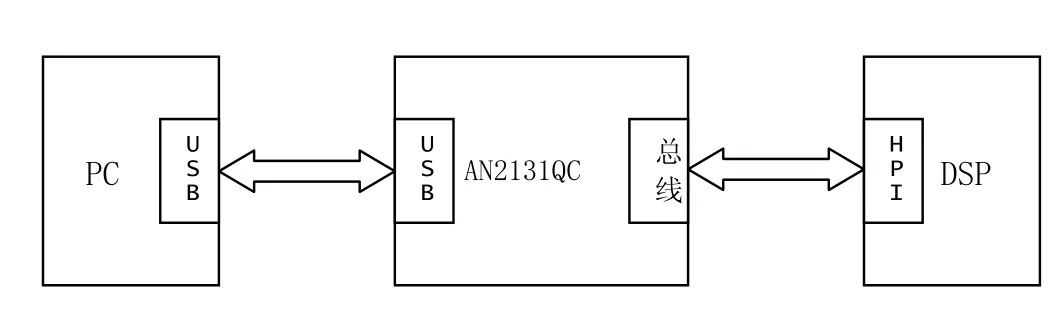

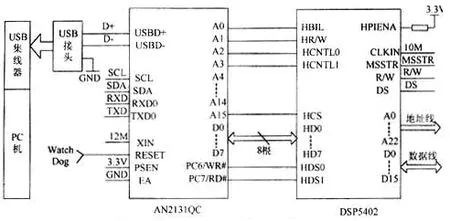

系统采用PC主机通过USB接口与USB集成芯片通信,USB集成芯片再通过访问DSP的HPI口(主机接口)与DSP通信的方式实现DSP与PC的USB通信,通信模型见图3。USB集成芯片用Cypress公司的EZ-USB系列的AN2131QC芯片,该芯片支持存储器扩展,具有低功耗、低噪声、有效的高级语言支持和增强的指令集等特性,完全符合USB1.1规范。提供16个传输端点,各端点的缓冲区为64 B,各端点可以互不干扰地通过USB发送存储数据[6]。AN2131QC有块传输、中断传输、同步传输以及控制传输4种USB传输模式。连接原理图如图4所示。

图3 DSP与PC的USB通信模型

图4 USB通信电路

3.1 PC与AN2131QC的通信

要实现PC与USB芯片AN2131的之间进行数据传输需同时具备上层PC端程序和底层AN2131程序。在PC上,由于Cypress提供了EZ-USB的底层驱动,因此基本不需要改动就可以直接应用,此处不详述。

对AN2131硬件编程时,按照Cypress的建议,修改必要的描述符,完成USB和外部接口初始化工作。在主程序段的循环等待过程中,检测PC传送来的数据是否已存于端点缓冲区,有就读出并写字节计数器,通知EZ-USB内核程序已完成数据读取。然后,完成必要的数据处理任务。如果有来自DSP模块的数据要传送给PC,可将数据放到特定的端点缓冲区中,写端点的字节计数寄存器通知内核,由内核完成向PC上传数据的任务。需要注意的是:由于端点缓冲区只有64 B的长度,底层硬件每次只能接收64B,而PC却没有长度的限制,所以用户要进行多组数据的组合工作。

3.2 AN2131QC与TMS5402间的数据传输

使用DSP的HPI口作为AN2131QC与DSP的通信通道。TMS5402的HPI是一个8位的通信接口,采用地址线、数据线复用模式,另有10根控制线来辅助完成数据的传送。TMS5402的增强型HPI口可以通过HPI口外部处理器可以访问DSP内部所有RAM,可以依靠自身的主时钟操作,无需同步模式。

将TMS5402的HPI口与AN2131QC外部总线连接起来,使得对于AN2131QC而言,DSP的HPI口相当于一个只有几个存储单元的外部设备。AN2131QC通过外部总线实现HPI接口的控制时序,此处使用HPI查询模式。具体连线方法如图6所示。

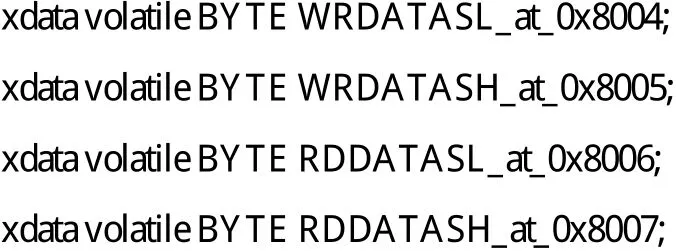

这种连接方法,用户可将TMS5402的HPI口的各个寄存器映射为AN2131QC的外部地址,通过读写这些地址,更改TMS5402的HPI口寄存器中的内容即可实现向TMS5402内部RAM读写数据的功能。在编写AN2131QC底层软件代码时,可以将这部分的功能定义为几个宏,进行以下地址映射:

根据上述地址定义,AN2131QC可以通过先写地址、再读写数据的方式,操作DSP5402 16 kB片内RAM的内容,即可实现双机通信,进而实现PC与底层DSP的通信[7]。

4 基于DSP的数据处理算法

地震信号具有非平稳、非高斯、非线性、信噪比低、海量数据等特点。于是对地震数据处理和记录提出了较高的要求。而快速傅里叶变换(FFT)、小波等算法在该类信号的去噪和压缩等处理中起到了一定的作用。

为提升后续地震波形回放效果、保证采集数据的可靠性,必须对采集的数据作陷波、滤波等数字信号处理。回放显示滤波用DSP作频域滤波,滤波参数可调。频域滤波比时域滤波具有速度快、精度高的优点,但滞后相对较多,频域滤波需等待数据采集后才可进行,时域滤波可边采集边滤波。因为回放是数据采集后才进行的,所以滞后的影响可以忽略。频域滤波的一般方法是即将采集信号作FFT变换,然后去掉非期望频率,再作IFFT[8]。

为适应记录数据存储要求,地震数据压缩是非常必要的,除了可以节省存储空间,而且还可以提高地震数据的处理速度。利用二维小波分解去相关性质,可以高效地对地震数据进行压缩, 地震数据的压缩比高达40倍,而且失真小[9]。

用DSP作数据处理时,以TMS320C54x系列芯片为基础的DSPLIB库函数,便于在DSP芯片进行FFT运算[10]。TMS320C54x系列函数库是优化了的C函数库,它含有50个通用的信号处理程序,由汇编编写,并可由C调用。这些程序用在对执行速度要求快,计算量大的实时运算中。使用这些程序,能取得比用标准C编写的相关程序要快得多的执行速度。

5 实验结果及分析

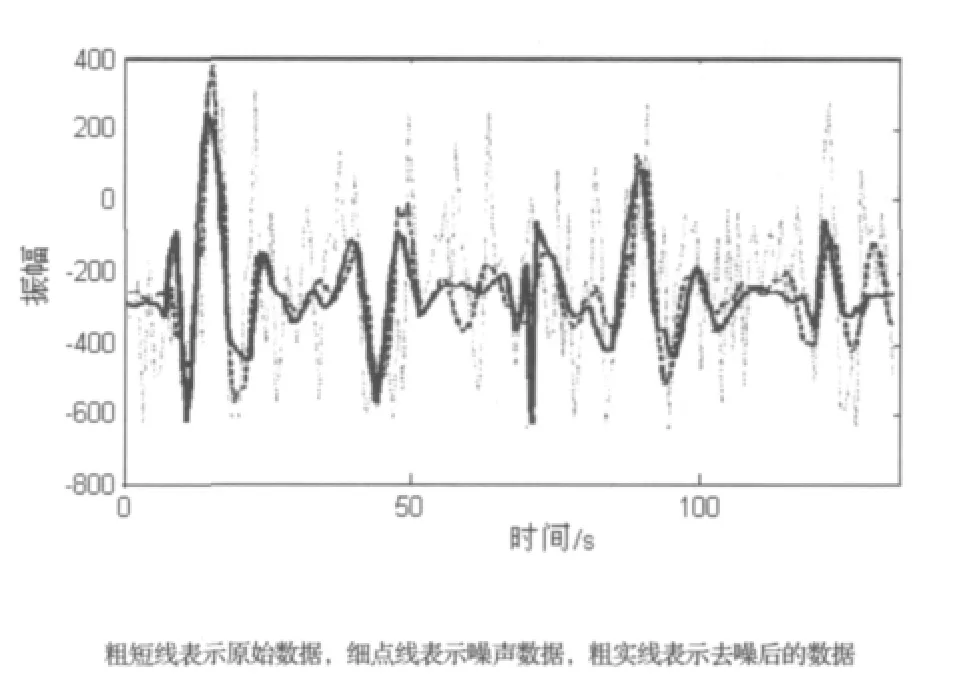

以下是应用了上述基于DSP的数据处理算法后的地震波形与原始波形的对比如图5所示。可见二维小波算法在去除噪声方面起到了一定的作用,尤其是在对边沿点非连续点的隔离方面效果比较明显。实验表明经过算法处理后的地震波数据在视觉效果和峰值信噪比值方面都有一定的效果。

图5 地震波算法处理比较

[1] Bhattacharya S N,Dattatrayam R S.Recent advances in seismic instrumentation and data interpretation in India[J]. Current Science,2000,79(9):1347-1358.

[2] INOVA公司.VectorSeis数字检波器[Z].天津: 英洛瓦(天津)物探装备有限责任公司,2010.

[3] 朱利.超小型精密三分量地震传感器[J]. 地质装备,2004,5(2):13-14.

[4] Texas Instruments.TMS320VC5402 datasheet[Z]. Texas Instruments,2000.

[5] Texas Instruments.TPS767D301,TPS767D318,TPS767 D325[Z]. Texas Instruments,2000.

[6] 张大勇,王立德. 基于EZ-USB实现PC机与DSP设备间的高速通信方案[J].现当电子技术,2004(1):31-33.

[7] 罗兵.用DSP作地震勘探信号实时处理[J].石油工业计算机应用,2001(2):20-21.

[8] A Vassiliou. Comparison of wavelet image coding schemes for seismic data compression [A]. 67th SEG Annual Meeting[C],1997:1334-1337.

[9] 邱立存,闻武,刘海英.TMS320C54X系列DSP上FFT运算的实现[J].微计算机信息,2005,21(7-2): 34, 136-137.