基于FPGA的BPSK调制与解调器设计★

2011-03-16高磊陈志强吴黎慧胡洋蒲南江

高磊,陈志强,吴黎慧,胡洋,蒲南江

(中北大学信息探测与处理技术研究所,山西 太原 030051)

0 引言

BPSK(二进制相移键控)是利用载波的相位变化来传递数字信息,具有抗噪声性能好、易于产生、误码率低等优点。但传统的用硬件实现BPSK的方法,设备相对比较复杂,成本高。本文针对BPSK信号的特点,提出了基于FPGA的BPSK调制解调器的一种实现方法,这种方法利用数字基带信号去控制输出载波相位,产生一种相位发生跳变的BPSK信号,而且原理通俗易懂,电路结构简单,容易实现。在解调器的设计中,已调信号有两个不同的相位,

通过VHDL语言编程实现将已调信号解调出基带信号。

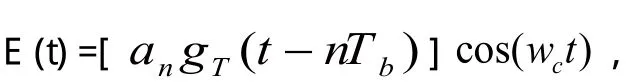

1 基本理论

图1 BPSK原理图

2 设计思想

2.1 基带信号的产生

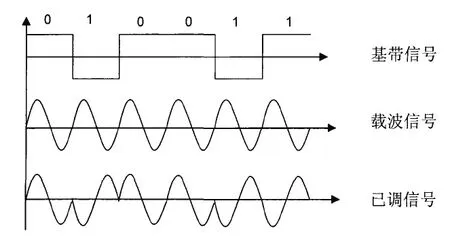

伪码最重要的特性是具有近似于随即信号的性能。因为噪声具有完全的随即性,也可以说具有近似噪声的特性。二元m序列是一种伪随机序列。构造一个产生m序列的线形移位寄存器,首先要确定本原多项式,本电路设计中,构造的M序列n=4,周期P=15,PN码为111101011001000,本原多项式为f (x )= x4+ x3+1,通过Altera公司的集成开发环境对软件进行仿真验证,如图2所示。其中clk为时钟信号,clr为复位信号,PRN为初值,output为输出信号。

图2 伪码仿真图

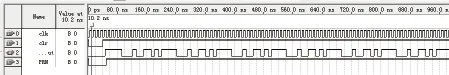

2.2 BPSK调制

BPSK调制在扩频载波调制中是一种极重要的调制方式,它的抗干扰性及通频带的利用率均优先于ASK移幅键控和FSK移频键控。因此,PSK技术在高速数据传输中得到了十分广泛的应用,本文中采用BPSK调制技术,利用VHDL语言编程实现BPSK调制。BPSK调制结构图如图3所示。计数器对外部时钟信号进行分频与计数,并输出两路相位不同的数字载波信号;2选1开关在基带信号的控制下,对两路载波信号进行选通,输出的信号即为BPSK信号。

图3 BPSK调制结构图

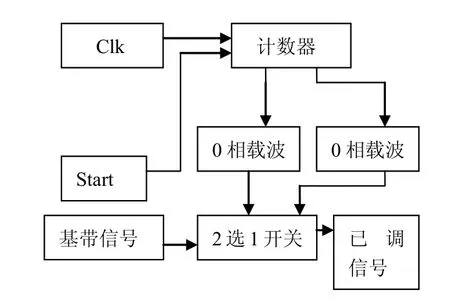

通过Altera公司的集成开发环境对软件进行验证,如图4所示。其中clk为时钟信号,clr为复位信号,PRN为初值,output为输出信号,start为开始信号,t1为m序列信号即输入信号。可以看到,每当输入信号发生0、1变化的时候,输出信号均会发生信号跳变。

图4 BPSK调制仿真图

2.3 BPSK解调

BPSK解调器的结构图如图5所示。图中,计数器输出与发射端同步的0相数字载波;将计数器输出的0相载波与数字BPSK信号中的载波进行与运算,当两比较信号在判决时刻都为1时,输出为1,否则输出为0,从而实现解调。

图5 BPSK解调结构图

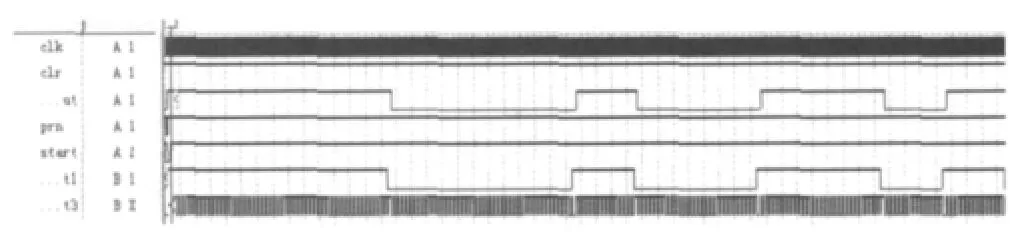

通过Altera公司的集成开发环境对软件进行验证,如图6所示。其中clk为时钟信号,clr为复位信号,PRN为初值,output为输出信号,start为开始信号,t1为m序列信号即输入信号。可以看到,每当输入信号发生0、

1变化的时候,t3信号均会发生信号跳变,表明调制成功,而output与m序列输入信号一致,表明解调成功。

图6 BPSK解调仿真图

3 结束语

本文论述的基于FPGA的BPSK调制与解调系统简单易行,具有很强的实用性,通过VHDL语言编写程序完成BPSK信号的调制与解调,为相关领域提供了较好的模型和方法,具有很强的实际使用价值。但本系统在提高码速率方面亟待进一步提高。

[1] 吴继华,王诚.Altera FPGA/CPLD设计[M].北京:人民邮电出版社,2007.

[2] 刘裕晓,方强.EDA技术与VHDL电路开发应用设计[M].北京:电子工业出版社,2009.

[3] 束礼宝,宋克柱,王砚方.伪随机数发生器的FPGA实现与研究[J].电路与系统学报,2008,8(3):121-124.

[4] 邬杨波,王曙光,胡建平.有限状态机的VHDL设计及优化[J].信息技术,2008,28(1):75-78.

[5] 许艳丽.扩展频谱通信系统[J].青岛大学学报,2009,(12):12-18.

[6] 童成意.扩频通信技术的应用研究[J].湘潭师范学院学报:自然科学版,2008,(8):21-28.

[7] 郑晓昆,王兰勋.同步系统在直扩系统中的作用[J].河北大学学报:自然科学版,2008,24(4):430-433.

[8] 宫二玲,王跃科,杨俊.直接序列扩频码元同步的快速捕获及跟踪[J].国防科技大学学报,2009,(4):77-78.