存在不稳定失效现象光耦的失效分析研究

2011-02-04孟猛张延伟王旭

孟猛,张延伟,王旭

(中国空间技术研究院,北京 100029)

1 引言

随着光电技术的发展,光电器件已广泛应用于多个领域,光电耦合器就是其中之一。由于其体积小、无接触和寿命长等特点,可用于电器隔离、开关电路和高压隔离等多种电路中。光电耦合器的大量使用,以及半导体技术的迅速发展,集成度越来越高,在使用中发生失效的现象也呈现多样、复杂的特点,甚至存在诸多不稳定的失效现象[1-3]。本文结合某用户使用的、AGILEN T公司生产的光电耦合器4N 55/883B发生1例失效的典型案例,对存在不稳定的、分析过程中故障现象消失的光电耦合器的失效分析技术和方法进行讨论,最终确认器件的失效原因是外部过电应力导致器件烧毁失效。

2 失效现象

2.1 光电耦合器原理及现场失效现象

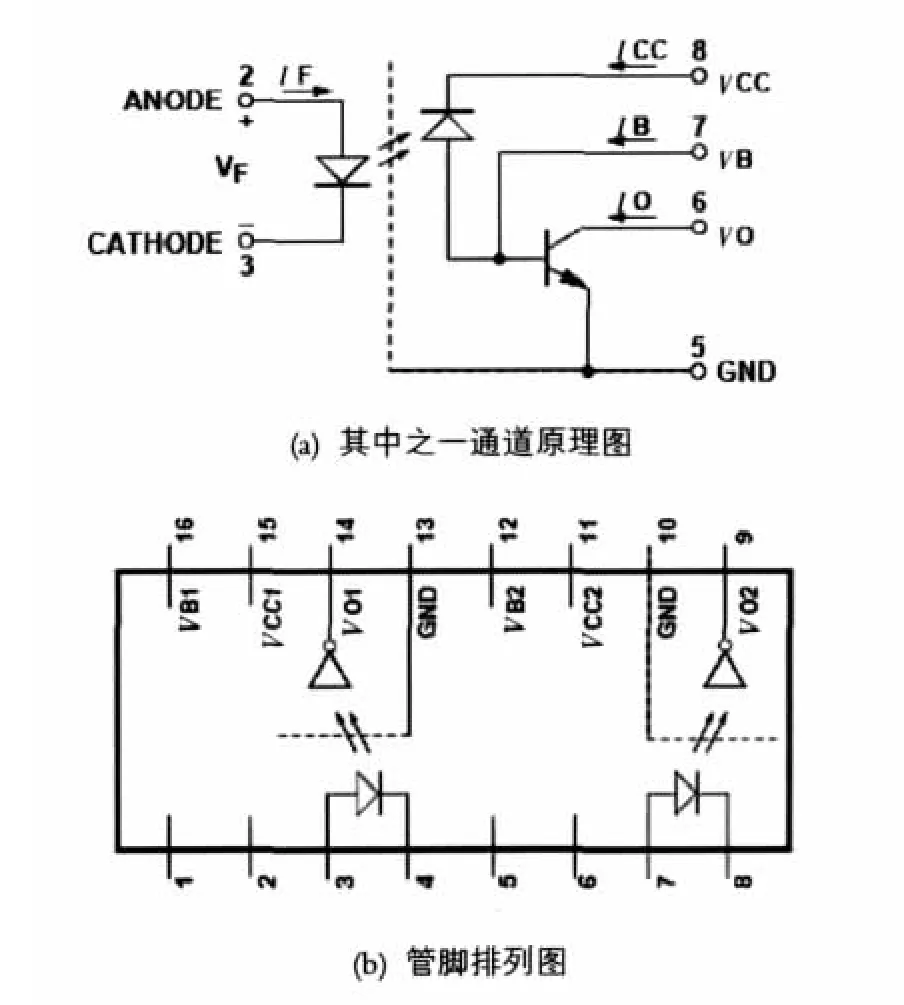

4N 55/883B为独立的2个通道光电耦合器,图1给出了其中之一通道原理图和外部管脚排列图。

图1 4N55/883B原理图

器件现场失效现象为:用户描述在对该光耦加电测试时,发现器件失效,具体表现为Pin9输出电平恒为高,断电后用万用表测试,发现器件Pin12与Pin10之间成不稳定的低阻特性,开始为193.0 Ω,后变为313.9 Ω,最后约为1.1 M Ω左右。器件失效的测试结果与器件Pin9输出电平恒为高的结果是一致的,原因是Pin12-Pin10(B-E)之间成低阻特性,该特性导致输出三极管基极无法控制集电极输出,因此,Pin9无低电平输出,恒为高电平。

2.2 失效分析单位的故障复现及不稳定现象

失效器件至失效分析单位后,首次测试结果如下:

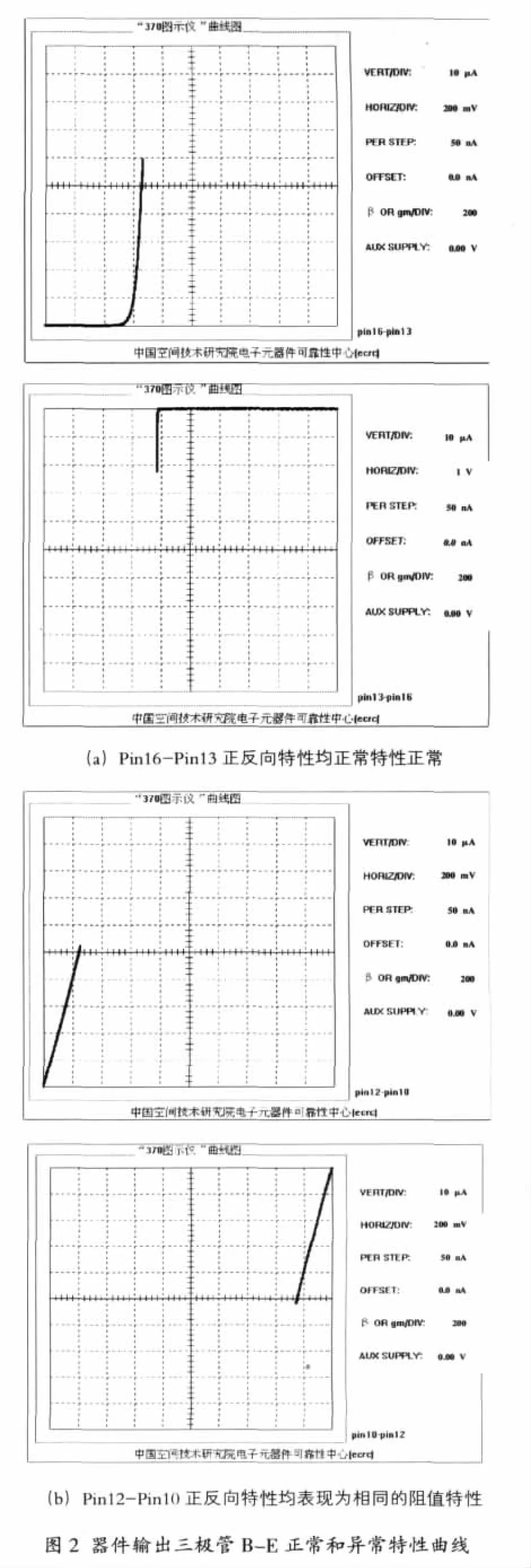

a) 用图示仪T ek370测试

Pin16-Pin13特性正常,相对应功能相同的另外一通道Pin12-Pin10之间成阻性,阻值约为5 kΩ,见图2。其它管脚间的特性未见异常。

b) 用万用表测试

Pin16-Pin13之间的阻值为4.82 M Ω,Pin12-Pin10之间的阻值为4.76 M Ω,器件故障现象消失。

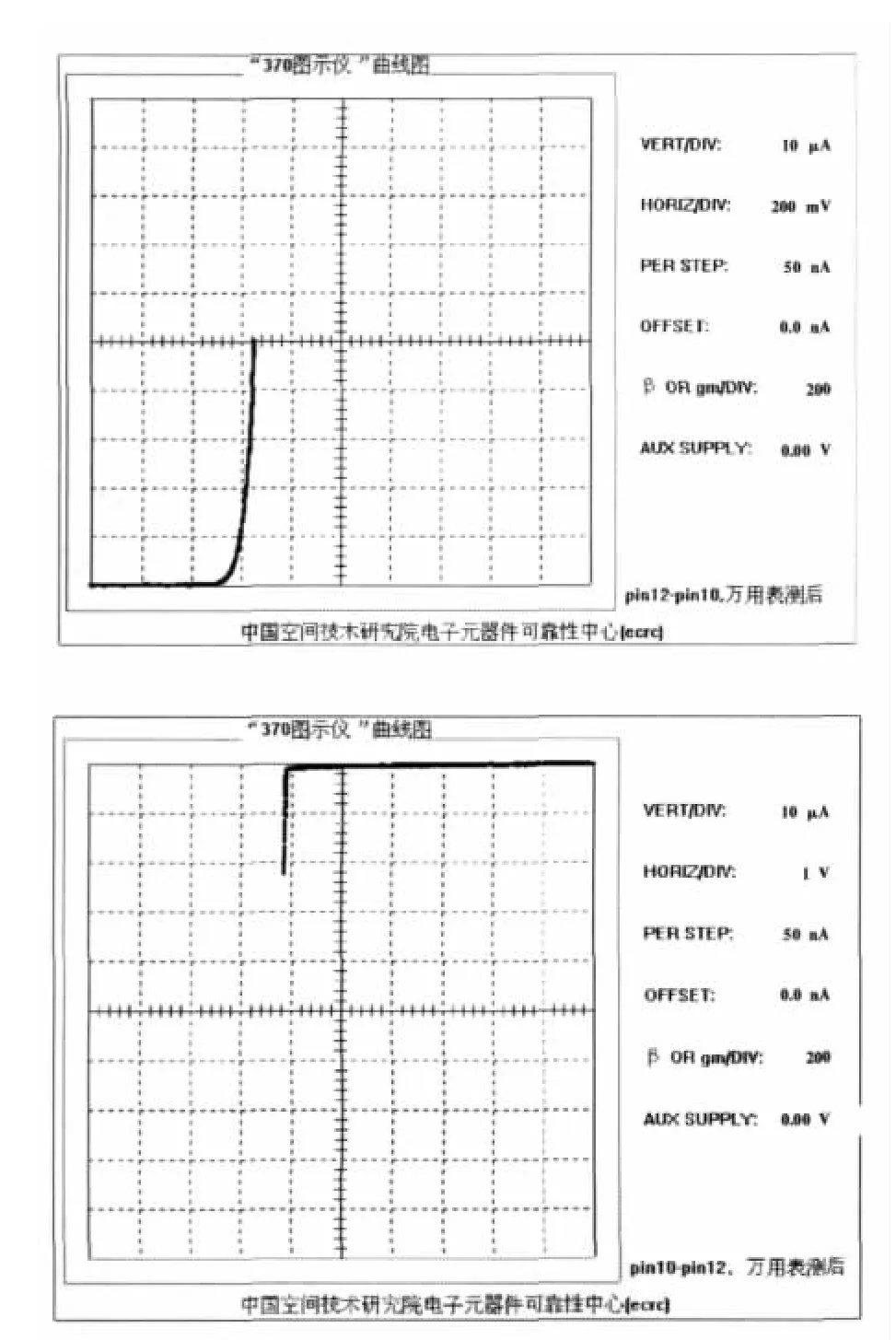

c)重复用图示仪T ek370测试

Pin16-Pin13与Pin12-Pin10之间的特性曲线相同,器件故障现象消失,见图3。

d) 室温放置48 h后测试

Pin12-Pin10之间的特性未见明显变化。

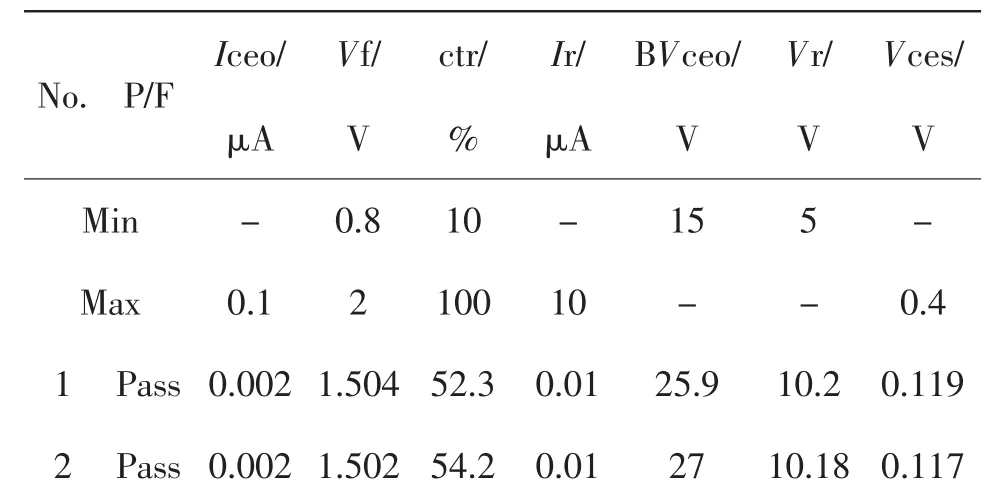

e)用专用测试设备对全部器件参数进行测试

全部合格,且2个通道间没有明显的异常,测试结果详见表1。

图3 器件故障现象消失后Pin12-Pin10之间正向、反向特性曲线恢复正常

表1 器件电参数测试结果

3 针对4N55/883B的失效分析

3.1 故障复现检查和试验

从失效光电耦合器4N 55/883B的失效现象分析结果来看,器件的失效与其内部的发光二极管以及它和光敏三极管的耦合部分的关系很小,失效的部位很可能是其输出部分。器件的失效现象在现场测试时即不稳定,在失效分析单位的首次测试后,失效现象即消失。为了能够顺利进行失效分析,需要进行一系列的针对性的检查和试验,这些检查和试验针对一些可动金属多余物、低温结露和芯片离子沾污等可能造成不稳定故障现象的原因,进行逐一分析、排除。主要包括:1)X射线实时检测系统检查,器件内部未见异常;2)进行+125℃、+5℃、0℃、-5℃、-10℃、-55℃测试,进行-10~+5℃温度变化的监测,器件故障现象未能恢复;3)高温反偏试验、老炼试验,试验前后测试器件,故障现象未能恢复;4) PIN D、密封性试验均合格。

3.2 解剖分析

能够进行的无损检查和故障复现试验没有复现器件的故障现象,为了查找器件失效的真正原因,进行解剖检查、分析。

a)开帽内部检查

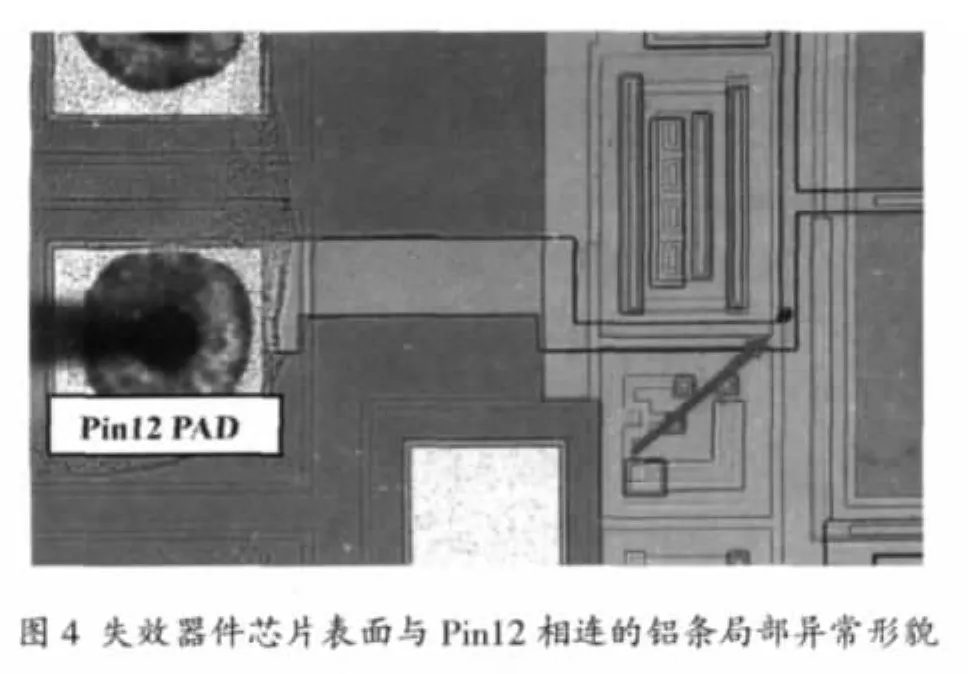

开帽后,用体式显微镜检查,器件内部结构和外键合区未见异常。由于该光耦器件采用立体结构,且内部有封装胶,无法直接对芯片进行详细的检查。取下盖在芯片上的发光二极管,用化学法去除内部封装胶。用体式显微镜和金相显微镜检查芯片表面,发现与Pin12直接相连的金属化铝条局部存在异常,见图4。但普通光学检查不能进一步确认该异常与器件故障现象的关系。

b) SEM检查和EDS分析

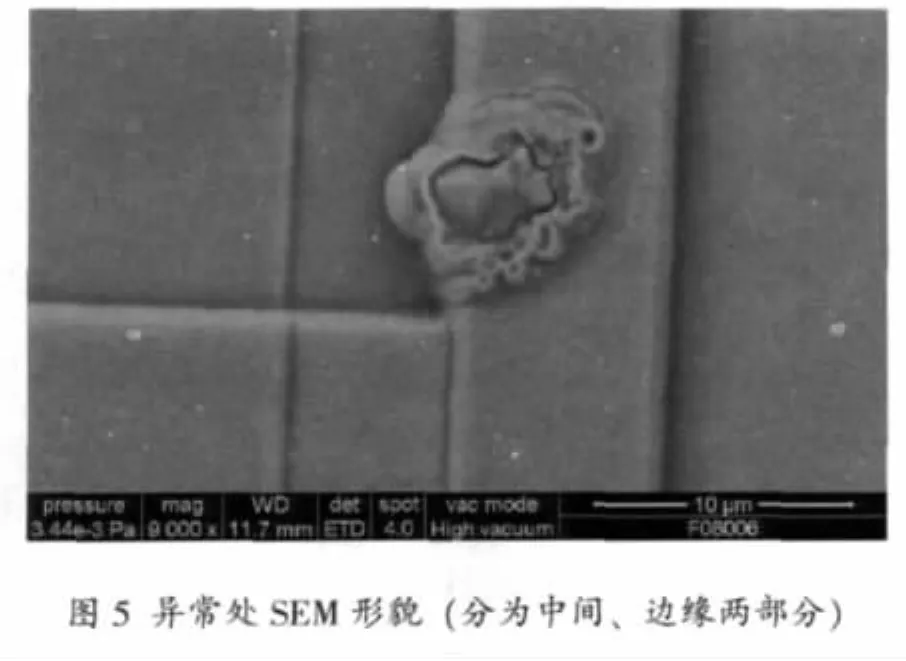

对器件芯片表面异常处进行SEM检查和EDS分析,SEM形帽见图5。SEM检查表明,异常处分为明显的中间、边缘两部分。能谱分析结果为(详见图6):异常处的边缘部分与无异常的芯片金属化部分成分相同,主要为Al(芯片金属化层为Al)、O、Si(芯片表面钝化层为 SiO2); 异常处的中间位置主要为O、Al,没有Si元素,即该处为裸露的Al(部分被氧化),没有SiO2钝化层覆盖。

c) FIB剖面分析

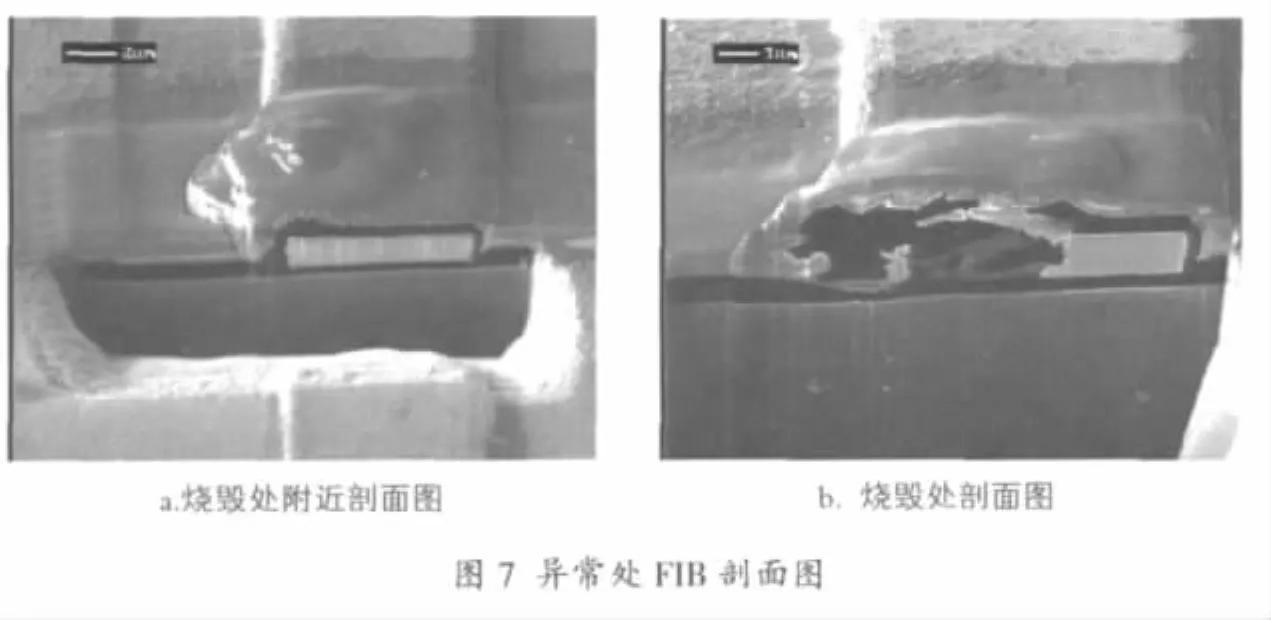

对器件内部异常处利用FIB制作剖面进行分析,发现该处铝条呈现熔融迹象,铝条上方的钝化层有受热鼓起形成的空洞,分析认为是外部异常电应力烧毁所致,见图7。

4 4N55/883B的失效原因分析

4.1 故障现象内部原因分析

对于导致器件Pin12-Pin10成短路特性,但是故障现象不稳定,并分析过程中消失的原因,认为可以分为以下几个方面进行分析:

a)器件外部沾污导致的故障现象

外观检查器件Pin12、Pin10附近,未见异常,且该两管腿不直接相邻,Pin12-Pin10故障现象存在时,Pin12-Pin11特性曲线正常,因此该原因可排除。

b)器件内部(芯片外部)多余物导致的故障现象

开帽内部检查,内引线的外键合区、引线之间等敏感部位没有可导致短路的多余物,因此该原因可排除。

c)芯片钝化层N a离子等沾污导致的故障现象

芯片表面钝化层可动电荷N a+沾污可引起敏感部位短路,并且现象不稳定。对器件pin12-Pin10施加反向4.8 V电压,在125℃时进行24 h高温反偏试验,未能复现故障现象,表明该原因导致失效现象的可能性很小。

d) 芯片内部P-N结异常导致的故障现象

芯片内部P-N结由于内部缺陷或外部异常电应力导致异常,可引起短路,但是该现象常温下一般不会恢复;并且,对器件进行48 h老化,器件故障现象仍未复现,因此该原因可排除。

e) 与Pin12相连的铝条异常处导致的故障现象

内部检查发现,与Pin12直接相连的金属化铝条局部存在异常。排除以上原因,该处异常导致器件故障现象的可能性很大。SEM和EDS分析表明,该异常分中间、边缘两部分,边缘部分的主要成分为Al、O、Si,中间部分主要为Al、O,即中间部分为裸露的Al(部分被氧化),没有SiO2钝化层覆盖。用FIB对该异常进行剖面分析,发现该处铝条呈现熔融迹象,铝条上方的钝化层有受热鼓起形成的空洞。

分析认为,外部异常电应力导致与Pin12直接相连的金属化铝条损伤、熔融,并造成如下失效现象:

a)对于铝条上面,由于钝化层和光电耦合胶(封装胶)存在,烧毁产生的热量无法及时散失,导致钝化层鼓起产生空洞,熔融的铝条突破芯片钝化层(SiO2),在芯片表面形成边缘为钝化层堆积、中间没有钝化层覆盖的Al。

b)对于铝条下面,熔融的铝条使该铝条部分突破下层氧化层,并与芯片隔离区虚接,而电路设计上,该隔离区与“地”(Pin10)相连,因此,导致器件Pin12-Pin10之间成不稳定的低阻特性。如图8所示。

图8 芯片金属化受外部异常电应力损伤后,导致其与隔离区虚接示意图

4.2 故障现象外部原因分析

器件铝条烧毁处直接与Pin12相连,因此外部异常电应力从Pin12引入,存在ESD和外部过电应力两种可能:

a)使用过程中Pin12悬空,未涂三防漆,静电放电(ESD) 可能导致与Pin12相连的铝条局部烧毁。但是ESD的电压高,能量低,并且器件的使用环境为静电受控的环境,此环境下一般情况对器件的损伤不会导致铝条大面积烧毁,器件因ESD导致失效的可能性很小。

b)使用过程中Pin12悬空,未涂三防漆,外部过电应力(EOS) 可能导致与Pin12相连的铝条局部烧毁。由于Pin12与Pin11(VCC2) 相邻(图1),并且它们之间的间距很小,测试过程中万用表笔很容易将这两个管腿短接,导致Pin12与VCC2误接,而VCC2可接2~18 V电源,这导致光敏三极管的B-E结处于瞬间正向导通状态,与Pin12相连的铝条通过大电流,在拐角处铝条局部熔融,发生文中的失效现象。

5 结论

光电耦合器件4N 55/883B的Pin12-Pin10之间呈不稳定的阻性,导致器件失效,但该故障现象在失效分析过程中消失,经过多个环境试验和加电试验等复现试验后,均未复现。解剖检查,发现与Pin12直接相连的金属化铝条局部存在异常;SEM、EDX和FIB对该异常进行分析,发现该处铝条中央呈现熔融迹象,铝条上方的钝化层有受热鼓起形成的空洞。结合器件的使用过程分析认为,外部过电应力导致与Pin12直接相连的金属化铝条烧毁,该铝条下面,熔融的铝条使该铝条部分突破下层氧化层,并与芯片隔离区虚接,而电路设计上,该隔离区与“地”(Pin10)相连,从而导致器件Pin12-Pin10之间成不稳定的低阻特性。该失效案例较为特殊,外部过电应力没有造成器件永久、恒定失效,原因在于芯片表面铝条损伤较轻,处于临界状态。损伤后,在外部持续通电的情况下,短路通道被破坏,而在一般的故障复现试验中,难以恢复。因此,对于该类失效分析,每一步的测试、记录显得尤为重要。

6 结束语

器件的VB、VCC外管脚相邻且间距较小,VB仅为预留测试使用,实际应用时VB悬空,而VCC接2~18 V以上的电源。因此,用户在使用过程中检测时,很容易用万用表表笔等导体将VB、VCC短接,从而引起VCC电源直接加至输出三极管的B-E结,导致器件烧毁失效。实际上,器件Pin1、Pin2、Pin5、Pin6仍没有定义(图1),从结构分析(CA)的角度,完全可改进器件管腿排列结构,将VB合理安排,避免类似情况再度发生。

[1]张延伟.半导体器件典型缺陷分析和图例[M].北京:中国科学技术出版社,2004.

[2]陈媛,李少平.芯片剥层技术在集成电路失效分析中的应用[J].电子产品可靠性与环境试验,2009,27(增刊):10-14.

[3]龚欣,王旭.时序逻辑电路失效分析[J].半导体技术 ,2009, 34(10): 974-977.