基于FPGA同步电路的实现

2011-02-04刘如金

刘如金

(工业和信息化部电子第五研究所,广东 广州,510610)

1 引言

近年来,随着超大规模集成电路的发展,FPGA/CPLD等可编程逻辑器件的资源也有了极大的发展,FPGA在开发阶段具有安全、方便、可随时修改设计等不可替代的优点,在电子系统中采用FPGA可以极大地提升硬件系统设计的灵活性、可靠性,以及提高硬件开发的速度和降低系统的成本。ewFPGA的固有优点使其得到越来越广泛的应用。

对于FPGA设计,同步设计将优于异步设计。对于静态同步设计,当满足以下两个条件时,我们说这个系统是同步的:1)每个边缘敏感部件的时钟输入是一次时钟输入的某个函数,并且仍是像一次时钟那样的时钟信号;2)所有的存储元件(包括计数器)都是边缘敏感的,在系统中没有电平敏感存储元件。FPGA的同步设计可以理解为所有的状态改变都由一个主时钟触发,而对具体的电路形式表现为所有的触发器的时钟端都接在同一个主时钟上。

相比异步设计来说,同步设计有许多的优点,同步是通信系统中一个重要的问题。在数字通信中,除了获取相干载波的载波同步外,位同步的提取是更为重要的一个环节。因为只有确定了每一个码元的起始时刻,才能对数字信息作出正确的判决。利用全数字锁相环可直接从接收到的单极性不归零码中提取位同步信号。

2 系统组成

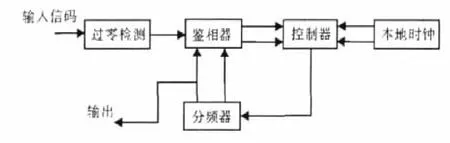

2.1 原理框图

数字锁相环位同步提取电路原理框图如图1所示。

图1 位同步提取电路框图

本地时钟产生两路相位相差p的脉冲,其频率为fo。输入信码的正、负跳变经过过零检测电路后变成了窄脉冲序列,它含有信码中的位同步信息,该位同步窄脉冲序列与分频器输出脉冲进行鉴相,分频比为m,若分频后的脉冲相位超前于窄脉冲序列,则在“1”端有输出,并通过控制器将加到分频器的脉冲序列扣除一个脉冲,使分频后的脉冲相位退后;若分频后的脉冲相位滞后窄脉冲序列,则在“2”端有输出,并通过控制器将加到分频器的脉冲序列附加一个脉冲,使分频后的脉冲相位提前。直到鉴相器的“1”、“2”端无输出,此时环路锁定。输出端就得到了该输入信码的位同步信号。

2.2 电路实现

基于FPGA的锁相环位同步提取电路的实现如图2所示,由双相高频时钟源、过零检测电路、鉴相器、控制器和分频器组成。

图2 锁相环位同步提取电路

2.2.1 双相高频时钟源

该电路由D触发器组成的二分频器、两个与门和两个非门组成(电路最右端)。它将FPGA的高频时钟信号clk_xm变换成两路相位相反的时钟信号,由e、f输出,然后送给控制电路的常开门G3和常闭门G4。其中f路信号还作为控制器中的D1和D2触发器的时钟信号。在实际系统中,FPGA的高频时钟频率为32.768 M Hz,e、f两路信号频率为32.768/2=16.384 M Hz。

2.2.2 过零检测电路

该电路见图2中jianxiang部分,它由D触发器和异或门组成。过零检测的输出脉冲codeout的宽度应略大于f路信号一个周期,但为了减少锁相环的稳态误差,该输出脉冲不宜过宽。在实际系统中,过零检测电路的时钟信号clkin由FPGA的高频时钟四分频得来,这样输出的脉冲宽度约是f路信号的两个周期。

2.2.3 鉴相器

该电路由两个与门组成,分别是超前门G1和滞后门G2(电路中间的两个与门)。过零检测电路的输出信号b与位定时信号clkout一起进入鉴相器,若clkout超前b,则滞后门G2被封锁,输出为0,超前门G1的输出端有窄脉冲输出;若clkout滞后b,则超前门G1被封锁,输出为0,滞后门G2的输出端有窄脉冲输出。

2.2.4 分频器

该电路对应于图2中div64部分。输出的信号频率是256 kHz,e、f两路信号的频率均为16.384 M Hz,故该电路完成16384 /256=64的分频功能。当控制电路无超前或滞后控制脉冲输出时,D1的q端为0,D2的q端也为0,常开门G3处于打开状态,常闭门G4处于关闭状态,e路信号通过常开门G3、异或门G5到达64分频器的输入端,经分频后产生稳定的位定时信号。

2.2.5 控制器

分频器输出的位定时信号clkout与过零检测脉冲b进行相位比较。当位定时信号clkout超前于b时,超前门G1有正脉冲输出。在触发脉冲f的上升沿,G1触发器的q端由低变高,经过非门后,使常开门G3关闭一个时钟周期,将e路脉冲扣除一个,使clkout相位向滞后方向变化一个时钟周期。当位定时信号clkout滞后于b时,滞后门G2有正脉冲输出。在触发脉冲f的上升沿,D2触发器的q端由低变高,使常闭门G4打开一个时钟周期,在分频器输入端添加一个脉冲,直到电路锁定。

2.3 实际结果

以上是全数字锁相环的电路工作原理,全部电路已在芯片上实现。芯片的工作频率选为32.768 M Hz,也作为位同步提取电路的本地高频时钟。另外,该时钟信号四分频后还作为过零检测电路的时钟。输入的单极性不归零码的码元速率为256 kbps。从输入信码中提取的位同步信号如图3所示,从波形上看,该全数字锁相环位同步提取电路能很好地从输出的信码中提取位同步信号。

3 结束语

图3 输入的信码与提取的位同步信号

在FPGA设计中,同步设计要优于异步设计,本文提出了一种数字锁相环的位同步提取电路的方案,并已成功地用FPGA器件进行了实现。此时钟提取电路可以快速、准确地对串行输入信码进行位同步时钟的提取,即使输入码流中的毛刺现象,本设计也有很好的时钟调整恢复功能,能极大地减小误码率。

[1]樊昌信.数字专用集成电路设计[M].北京:人民邮 电出版社,1999.

[2]徐志军,徐光辉.CPLD/FPGA 的开发与应用[M].北京:电子工业出版社,2002.