组合逻辑电路中竞争冒险的仿真分析

2011-01-11朱宏文

朱宏文

(海南软件职业技术学院 电子工程系,海南 琼海 571400)

在组合逻辑电路的分析设计中,经常将高低电平的变化看做理想化.由于半导体元件都有开关时间,所以当信号经过逻辑门电路时会产生一定的延迟.如果门电路的两个输入信号同时向相反的方向发生跳变(称之为竞争),可能使输出端产生干扰信号,即出现竞争冒险,这是数字逻辑电路应尽力克服的问题.一个逻辑电路是否存在冒险,常用代数判断法、几何判断法和表格判断法来确定,这几种方法虽然提供了检查各种电路竞争冒险的途径,但往往还需要经过实验的方法检验,才能最终确定电路是否存在竞争冒险现象.因此,只有实验检查的结果才能得出最终的结论,但是真正的实验观察法所需实验设备较多,操作相对比较繁琐,若以Multism为平台,则可方便、灵活地进行虚拟仿真实验,更好地检测到冒险竞争现象.同时,也有利于教师进行形象生动的课堂教学活动,帮助学生将理论与实际联系起来.

1 理论分析判断

2 建立仿真电路

2.1 确定输入信号

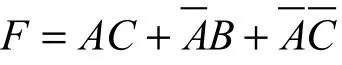

在仿真时需向逻辑电路输入端C提供变化的信号.这里变化信号由Multisim10软件中的虚拟信号发生器提供.打开信号发生器属性框(如图1所示),选择方波信号,设置频率为1 MHz,幅值为5 V.

图1 信号发生器面板图

2.2 建立仿真电路

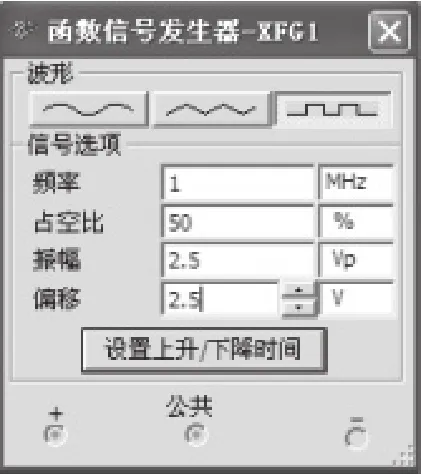

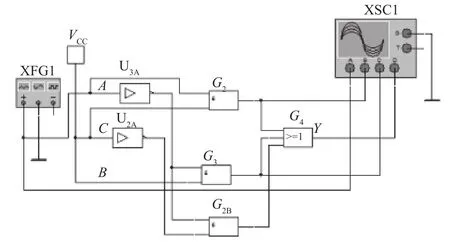

Multisim10软件的元件库中有大量的逻辑门可供选择,这里选择74HC_6V系列逻辑门和misc digtl库中的元件[3],为了能够对电路的多个信号同时进行观察比较,这里选择4通道的虚拟示波器,分别画出以A为研究对象的仿真电路模型和以C为研究对象的仿真电路模型,分别如图2和图3所示.以A为研究对象的仿真电路模型中,示波器的A通道用来观察输入信号,B通道用来观察传输门G2的输出,C通道用来观察传输门G3的输出,D通道用来观察传输门G4的输出.以C为研究对象的仿真电路模型中,示波器的A通道用来观察输入信号,B通道用来观察传输门G2的输出,C通道用来观察传输门G3的输出,D通道用来观察传输门G4A的输出.

图2 以A为研究对象的仿真电路

图3 以C为研究对象的仿真电路

3 仿真实验

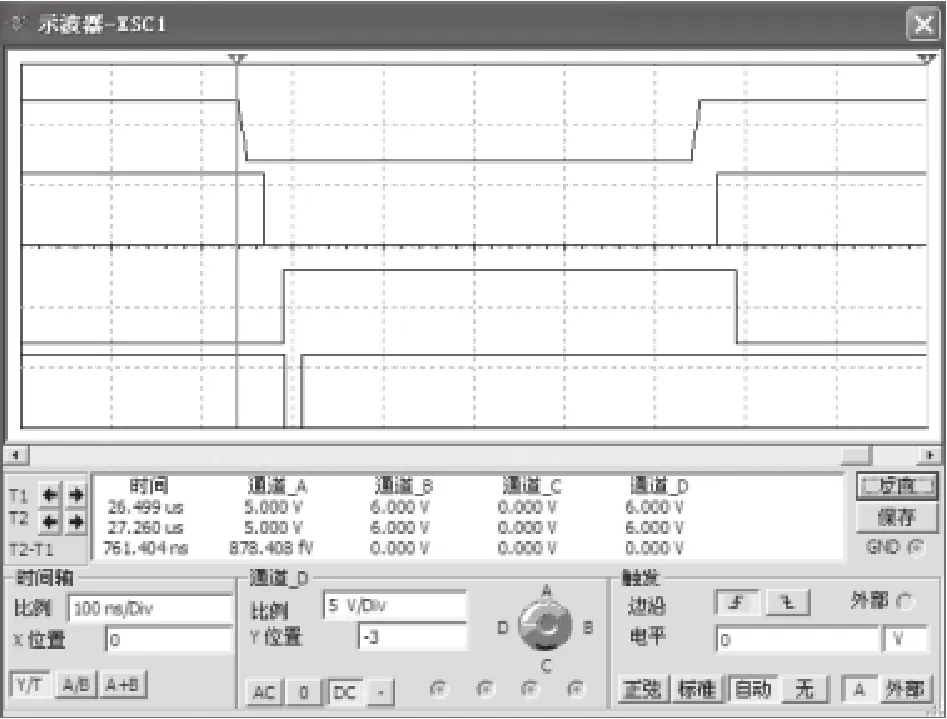

基于输入信号的频率为1 MHz,设置仿真时间为100 ns,这样观察2个周期就可以了.运行仿真,完成后打开示波器,以A为研究对象的仿真电路的仿真结果如图4所示.

示波器窗口界面中,自上而下依次为A端输入信号、传输门G2输出信号、传输门G3输出信号、传输门G4输出信号.当A端输入信号由高电平突变为低电平时,传输门G2由于传输延迟的存在,其输出信号由高到低的变化相比输入信号的变化时刻出现了延迟.传输门G3的输出同样也出现了延迟,而且从输入端到G3的输出经过了U2A、G3两个逻辑门,因此G3输出信号的延迟比G2输出信号的延迟更大,这就是传输路径的不同导致了延迟的不同.由以上分析可知,由于G2输出信号由高到低的变化和G3输出信号由低到高的变化不是同时发生的,存在时间差,出现了竞争,经过逻辑门G4后导致了低电平冒险脉冲的出现,该脉冲的输出也存在延迟.从图4中可以较为清楚地观察到竞争冒险的发生.

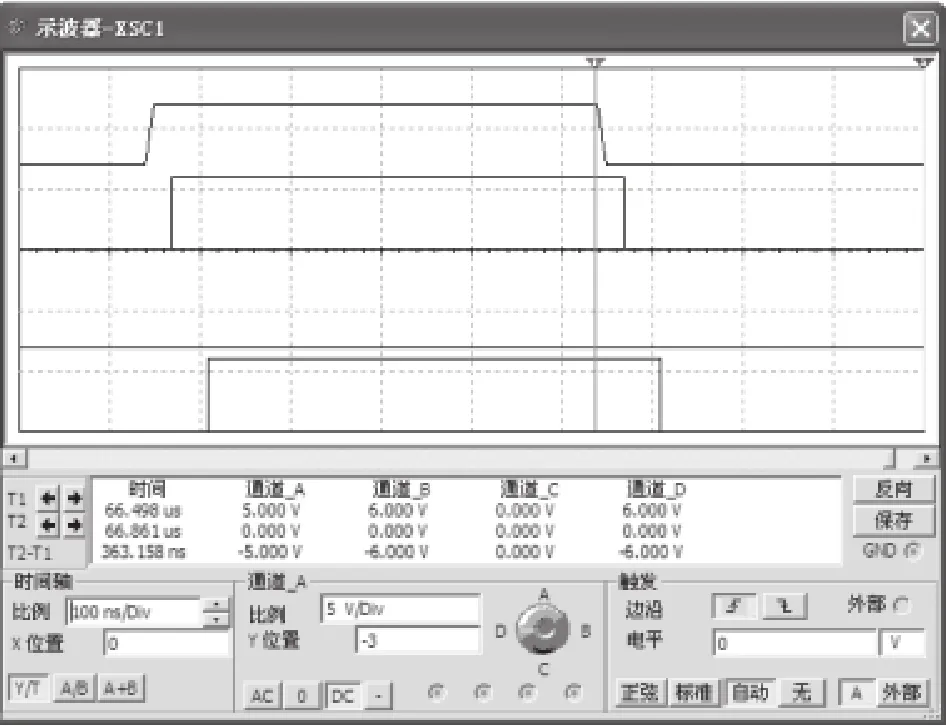

以C为研究对象的仿真电路的仿真结果如图5所示,示波器窗口界面中,自上而下依次为C端输入信号、传输门G2输出信号、传输门G3输出信号、传输门G4输出信号.当C端输入信号由高电平突变为低电平时,传输门G2由于传输延迟的存在,其输出信号由高到低的变化相比输入信号的变化时刻出现了延迟.但G3输出信号为零,不存在竞争的条件,逻辑门G4的输出信号应与G2信号相同,但由于G4也存在延迟,所以G4信号比G2信号滞后.

图4 以A为研究对象的仿真结果

图5 以C为研究对象的仿真结果

4 结 论

本文针对竞争冒险这一电路实际运行中发生的现象,在教学过程中引入Multisim10软件,利用Multisim10软件模拟实际电路的运行情况,由此观察当输入信号发生变化时,电路中各传输门的输出变化及之间的时序关系,以更加深入地分析和揭示竞争冒险现象的产生机理,对课堂教学起到了良好的辅助作用.

[1] 赵波. Multisim在竞争冒险教学中的应用[J]. 现代电子技术,2010(7):166-168.

[2] 鄢峰,卢超. 基于Multisim的竞争冒险仿真分析[J]. 电子科技,2009(12):38-40.

[3] 杨玉龙. 组合逻辑电路中的竞争冒险与Multisim2001仿真分析[J]. 黔西南民族师范高等专科学校学报,2008(4):108-110.

[4] 胡伟. 组合逻辑电路中竞争冒险的虚拟仿真实验设计[J]. 湖南第一师范学院学报,2010,10(5):152-156.

[5] 田野,孙宏宁,祖大鹏. 基于Multisim V7平台的组合逻辑电路中竞争冒险的分析[J]. 哈尔滨师范大学学报:自然科学版,2005,21(4):32-34.

[6] 张京英. 组合逻辑电路中的竞争冒险现象的判断和消除[J]. 青海师范大学学报:自然科学版,2003(2):43-44.